SCARICHE

ELETTROSTATICHE E LATCH-UP

Sia scariche elettrostatiche (ESD) sia scariche dovute a fattori dinamici ( EOS) possono dare rotture o

malfunzionamenti in un circuito e vanno evitate con determinati accorgimenti. Le scariche possono

verificarsi per diversi motivi:

-persone elettrostaticamente cariche che toccano uno o più piedini

-durante il trasporto dei circuiti questi possono venire a contatto con corpi carichi

-il circuito integrato può trovarsi in mezzo a un campo elettrico o avere accoppiamenti capacitativi con altri

sistemi

Se tali scariche superano certe soglie possono verificarsi o la ROTTURA DEL DIELETTRICO o la

ROTTURA DELLA GIUNZIONE p-n. Le soluzioni per limitare questo fenomeno vanno dal collegamento a

massa degli operatori che maneggiano i dispositivi , a imballaggi antistatici, all’uso di circuiti di protezione

(a diodo clamped) che sono inefficaci e inattivi finche i potenziali variano entro i limiti , mettono a massa o a

Vdd gli IN e gli OUT quando da questi entrano potenziali eccessivi.

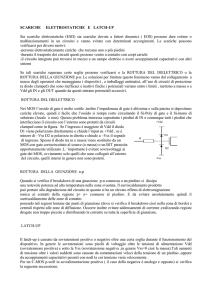

ROTTURA DEL DIELETTRICO

Nei MOS l’ossido di gate è molto sottile ,inoltre l’impedenaza di gate è altissima e sulla piastra si depositano

cariche elevate, quindi è facile che l’ossido si rompa corto circuitando il Si-Poly di gate e il Si-mono di

substrato (locale o non). Questo problema interessa soprattutto i piedini di IN e comunque tutti i piedini che

+Vdd

interfacciano il circuito con l’esterno sono protetti da circuiti

clamped come in figura. Se l’ingresso è maggiore di Vdd il diodo

D1 viene polarizzato direttamente e chiude l’input su +Vdd , se è

D1

minore di –Vss D2 si polarizza in diretta e chiude a –Vss il segnale

R

di ingresso. Spesso il diodo tra in e massa viene sostituito da un

MOS con gate cortocircuitato al source (a massa) o un BJT parassita

D2

opportunamente utilizzato .L ‘importante è evitare sovravoltaggi ai

gate dei MOS, ovviamente solo quelli che sono collegati all’esterno

-Vss

del circuito, quelli interni in genere non sono protetti.

ROTTURA DELLA GIUNZIONE n-p

Quando si verifica il breakdown di una giunzione p-n connessa a un piedino si dissipa

una notevole potenza ad alta temperatura nella zona svuotata. Il surriscaldamento prodotto

può portare alla degradazione del circuito in quanto si ha un elevato effetto di elettromigrazione

ionica ai contatti della regione p+ n+ connesse al piedino. E da evitare assolutamente quindi il

surriscaldamento delle zone di contatto

ponendo tali regioni lontane dai punti di giunzione (dove si verifica il breakdown cioè nella zona di bordo) e

centrali rispetto alle zone di diffusione. Occorre inoltre evitare addensamenti di corrente ,realizzando regioni

drogate non troppo piccole e distribuendo la corrente su tutta la superficie di giunzione.

LATCH-UP

Il latch-up è causato da sovratensioni positive o negative oltre una certa soglia durante il funzionamento del

dispositivo. In genere le sovratensioni sono picchi di voltaggio oltre le tensioni di alimentazione Vdd

(sovratensione positiva) e sotto la Vss (sovratensione negativa ,in genere Vss=0 cioè la massa).Tali aumenti

di tensione oltre i valori suddetti sono causate da commutazioni veloci della tensione di un piedino ,oppure

da accoppiamenti capacitativi pesanti con nodi la cui tensione varia velocemente .

Per un C-MOS p-well in sovralimentazione positiva ( il caso della negativa è analogo e opposto) si verifica

la seguente successione:

-picco di sovratensione positiva al drain del P-MOS ( nel p-well il substrato è N dove si trova il P-MOS).

Tale P-MOS ha il drain P a potenziale (Vdd+Xpicco) maggiore del substrato N(che è a Vdd) ed è polarizzato

in diretta. Allora il drain P emette lacune nel substrato.

-Tali lacune si muovono per diffusione nel substrato N e arrivano al p-well

- Il p-well raccoglie le lacune e per deriva (per campo elettrico)si muovono verso il CP (P+) del N-MOS nel

p-well che è a potenziale Vss e raccoglie tali lacune .

- Il moto di cariche attraverso tutto il p-well crea una caduta di potenziale dovuta alla resistenza di p-well

Rpw, e pone il p-well a potenziale maggiore del source del N-MOS che è di tipo N+, ed è a potenziale

minore. Quindi p-well e N+ (del source del N-MOS) sono polarizzati in diretta e il source libera elettroni nel

p-well.

-Tali elettroni si muovono per diffusione nel p-well verso il substrato N che li raccoglie

-Gli elettroni iniettati nel substrato N si muovono per deriva ( per campo elettrico) verso la connessione CN a

potenziale Vdd ( N+,contatto di polarizzazione del substrato N) , e attraversando tutto il substrato ,tali

cariche risentono della resistività non nulla di quest’ultimo Rsub.

-Si ha di nuovo una caduta di potenziale che pone il source del P-MOS a potenziale maggiore rispetto al Nsubstrato , quindi P+ del source e substrato N sono polarizzati in diretta.

-Il source P+ del P-MOS inietta lacune nel substrato.

-Tali lacune ricominciano in giro andando per diffusione verso il p-well e il ciclo si autoalimenta.

Si hanno quindi due transistor BJT parassiti che sono la causa del Latch-up e danno origine a un triristore

(SCR). Se tali transistor hanno un beta abbastanza elevato (si è visto che in genere i BJT parassiti dei MOS

hanno beta =100 200 quindi lavorano bene), cioè hanno un buon guadagno di corrente, il fenomeno diventa

rigenerativo e non si ferma ,anche se la sovralimentazione che la causato sparisce, si ha in pratica un circuito

bistabile. ( Il transistor BJT parassita verticale ha un beta molto elevato)

Vin

Vout

P+

Vout

Vdd

(source-subP-MOS)

N+

Vss

(source-p-wellN-MOS)

P+

P+

++

e-

N-substrato ( Vdd)

N+

N+

Rp-well ++

p-well

Vdd

SUBST

Vdd

Rsub

p-well

P+

e-

Rp-well

Rsub

Sezione C-MOS p-well con sovralimentazione + e latch-up

Vss

Circuito equivalente del latch-up

Se la sovratensione da luogo a una tensione e a una corrente

superiori a Vt e It ( valori di INNESCO) si innesca il latch-up

, e il funzionamento del circuito bistabile prosegue fino a che

o la tensione o la corrente non scendono al valore di Vh o Ih

,che sono i valori di MANTENIMENTO.

La conseguenza più drastica del latch-up è l’ incontrollato flusso

di corrente che attraversa il circuito, distruggendo le piste di metallo.

Usando un generatore a bassa erogazione di corrente si può valutare

L’effetto latch-up senza portare in distruzione il dispositivo ,che si

Limiterà a non funzionare finchè il latch-up non verrà spento.

Per controllare e limitare tale fenomeno ci sono alcuni accorgimenti:

separazione fisica adeguata dei due MOS P e N cosi la base del BJT

parassita orizzontale risulta molto spessa e il beta si abbassa limitando

il gain di corrente e il buon funzionamento del pnp orizzontale (si possono

inserire i pad tra i due MOS complementari)

Idd

Latch

Ih

It

Vh

Vt

Vdd

Curva di trasferimento del latch-up

inserimento di un anello di guardia drogato p (p guard-ring) a potenziale Vss del p-well attorno tutto il PMOS, Così si aggiunge un extra-collettore al BJT parassita pnpche riduce la raccolta di lacune da parte

del p-well

posizionare il contatto di polarizzazione del p-well alla estremità sinistra, vicino al drain del N-MOS

dove ho raccolta di lacune, così si diminuisce la resistenza di p-well

inserimento di un anello di guardia drogato n+ (n+ guard-ring) a potenziale Vdd. Cosi ho un extracollettore al BJT parassita npn

inserimento di un anello di guardia drogato n+ (n+ guard-ring) a potenziale Vdd. Questo deve stare tutto

attorno al transistor P-MOS, cosi diminuisco la resistenza di substrato ,Rsub

Realizzare ottimamente i contatti di guard-ring

Separazione fisica adeguata delle strutture di in e out, e la circuiteria interna

Vdd

Vout

Inserimento di un solo N-MOS per ognip-well

P+

Rsub,diminuita con ring

SUBST

Con tutte queste modifiche e aggiunte l’area di silicio occupata sarà

Vdd

notevolmente maggiore, tuttavia per evitare il latch-up, tali sistemi

sono indispensabili. Nei casi di integrazione spinta, dove non sia Extra-collettore

extrap-well collettore

possibile eseguire le modifiche precedenti ,il problema si risolve in

alternativa con:

Uso di strato epitassiale :cioè si costruiscono i dispositivi

Rp-well

deponendo gli strati su silicio EPI poco drogato(per s1vracompensazioni

diminuita

moderate) posto sopra uno strato di silicio drogato N+ di resistività molto bassa.

Abbasso così di molto la resistenza di substrato.

Vss

Uso buried layer molto conduttivi per abbassare le resistenze di substarto e di

p-well (come nei BJT il buried layer serve ad abbassare la resistenza di collettore) Circuito equivalente del latch-up

Riduzione del tempo di vita medio dei minoritari con opportuni drogaggi

in modo da alzare la –Is, corrente di leakage, e abbassare il beta dei BJT parassiti.

in tal modo però perdo in prestazioni del MOS ,perchè la bassa corrente

di leakage (con basse perdite di potenza in statica), è il punto forte dei

C-MOS.( soluzione per latch-up poco usata)

STI :shallow tranch isolation, isolamento mediante trincee scavate con RIE nel silicio e riempite di

isolante, così sono più sottili( che non la LOCOS ). Tale soluzione ,unitamente all’uso di strati

epitassiali ,è molto efficace contro il latch-up in quanto ,si ha bassa resistenza di substrato e isolamento

tre i MOS ,i cui BJT parassiti non possono diffondersi cariche. Vi sono però problemi di rumore ,in

quanto i disturbi passano ovunque attraverso il substrato molto conduttivo, e si infilano tra le trincee.

N.B. lo strato EPI dei MOS è uniforme su tutto il substrato, e viene quindi prodotto dalla ditta di componenti,

l’EPI del BJT deve essere prodotto dalla ditta che fa la fetta, perchè non è uniforme (c’è sopra il buried

layer), e costa molto di più