Transistori MOS

Ing. Ivan Blunno

21 aprile 2005

1

Introduzione

In questa dispensa verranno presentati i transistor MOS (Metal Oxide Semiconductor) di tipo N e P dal punto di vista del loro funzionamento elettrico, senza

analizzare i fenomeni di trasporto di carica che ne determinano il comportamento. In particolar modo verranno discusse le equazioni e le curve caratteristiche

dei componenti MOS.

2

Il transistor NMOS

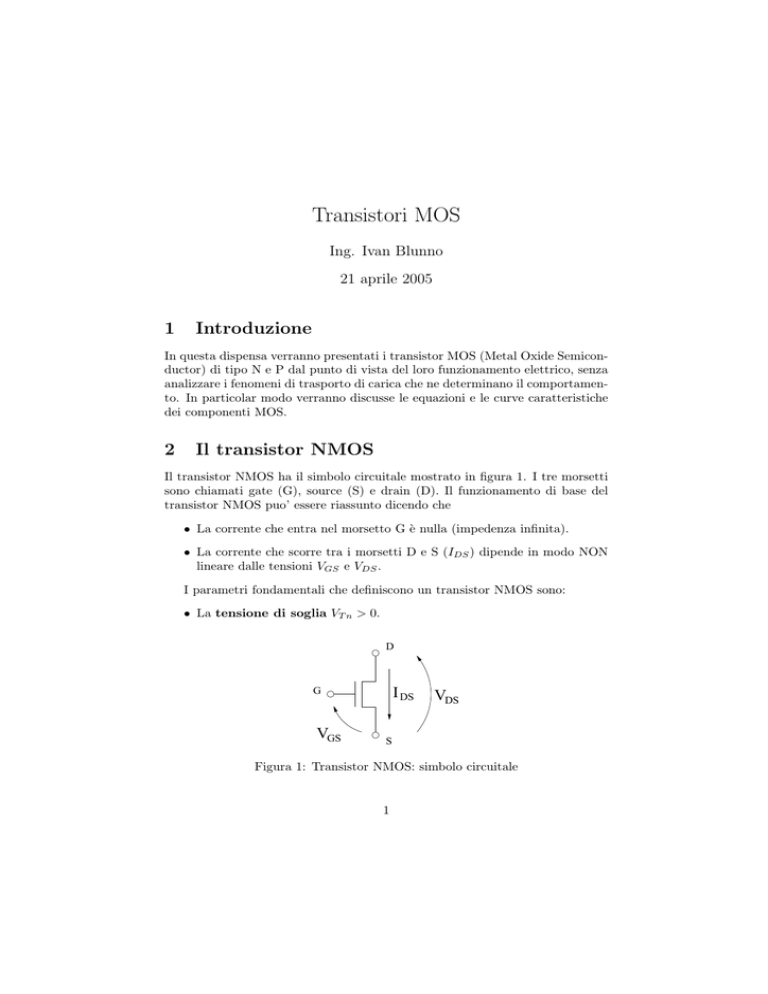

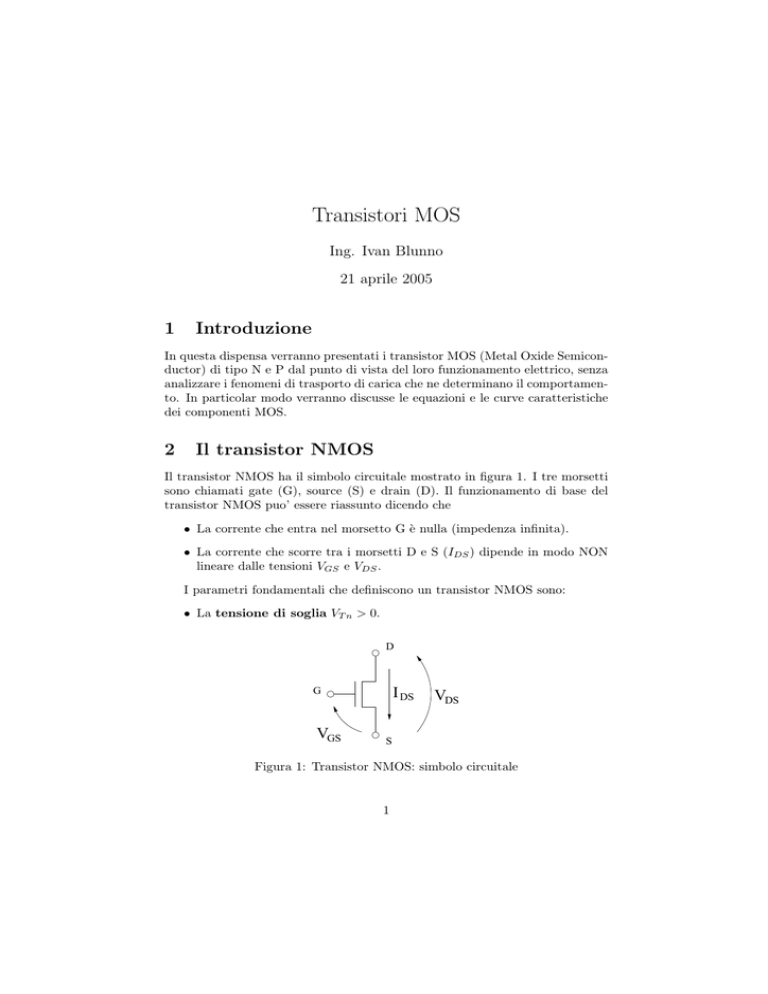

Il transistor NMOS ha il simbolo circuitale mostrato in figura 1. I tre morsetti

sono chiamati gate (G), source (S) e drain (D). Il funzionamento di base del

transistor NMOS puo’ essere riassunto dicendo che

• La corrente che entra nel morsetto G è nulla (impedenza infinita).

• La corrente che scorre tra i morsetti D e S (IDS ) dipende in modo NON

lineare dalle tensioni VGS e VDS .

I parametri fondamentali che definiscono un transistor NMOS sono:

• La tensione di soglia VT n > 0.

D

I DS

G

VGS

VDS

S

Figura 1: Transistor NMOS: simbolo circuitale

1

• Il guadagno βn = µn CLox W . In questa formula µn rappresenta la mobilità

degli elettroni, Cox la capacità dello strato di ossido tra gate e substrato

e W e L rispettivamente la larghezza e la lunghezza del canale.

A seconda dei valori delle tensioni VDS e VGS possono essere individuate 4

zone di funzionamento del transistor.

Zona di interdizione: VGS < VT n , ∀VDS

IDS = 0

Zona lineare: VGS > VT n , VDS ¿ VGS − VT n

IDS = βn (VGS − VT n )VDS

Zona triodo: VGS > VT n , VDS < VGS − VT n

h

V2 i

IDS = βn (VGS − VT n )VDS − DS

2

Zona di saturazione: VGS > VT n , VDS > VGS − VT n

IDS =

βn

(VGS − VT n )2

2

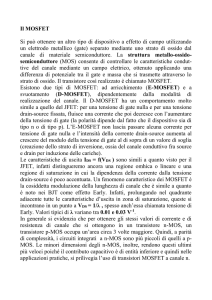

Il comportamento globale del transistor NMOS può essere osservato nel grafico di figura 2. Il grafico è parametrico secondo il valore di VGS − VT n . Dalle

equazioni mostrate in precedenza si può notare che il passaggio dalla zona triodo a quella di saturazione si ha quando VDS = VGS − VT n . Sostituendo questa

uguaglianza nell’equazione della zona triodo (o di quella della zona di satura2

zione) si ottiene che IDS = β2n VDS

. Questa relazione è un funzione parabolica

che rappresenta il luogo dei punti di passaggio dalla zona III alla zona IV. La

zona I rappresenta la zona di interdizione in cui la corrente IDS vale 0 (tutto

l’asse VDS ). La zona II è la zona lineare. In questa zona il transistor si comporta come una resistenza variabile di valore R = βn (VGS1−VT n ) . Infine in zona di

saturazione (zona IV) il transistor si comporta come un generatore di corrente

di valore I = βn (VGS − VT n )2 .

3

Il transistor PMOS

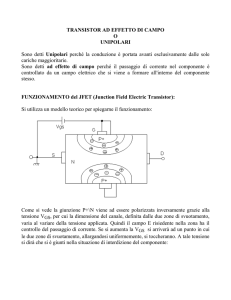

Il comportamento del transistor PMOS (il cui simbolo circuitale è rappresentato

in figura 3) può essere derivato da quello del transistor NMOS fatte salve alcune

differenze che verranno di seguito evidenziate:

2

I DS

III

IV

VGS - VTn = 4

VGS - VTn = 3

II

VGS - VTn = 2

VGS - VTn = 1

I

VDS

Figura 2: Transistor NMOS: curve caratteristiche.

S

VGS

I DS

G

VDS

D

Figura 3: Transistor PMOS: simbolo circuitale

3

VDD

I DS

R

vo

vi

VDS

VGS

Figura 4: Inverter NMOS

• La tensione di soglia VT p < 0. La condizione di conduzione sarà pertanto

VGS < VT p la cui analogia con l’equivalente relazione del NMOS può essere

meglio rilevata considerando i valori in modulo: |VGS | > |VT p |

• Le tensioni VGS , VDS e la corrente IDS sono tutte negative. Anche in

questo caso le equazioni che le contengono rimangono invariate rispetto

al caso del NMOS se invece del valore reale si considera il loro valore in

modulo.

• Il guadagno sarà βp =

mobilità delle lacune.

µp Cox W

L

dove in questo caso µp rappresenta la

A puro titolo di esempio viene di seguito riportata l’equazione della corrente

IDS che scorre in un PMOS in zona lineare (|VGS | > |VT n |):

|IDS | = βp (|VGS | − |VT p |)|VDS |

La corrente scorrerà da S verso D.

4

Inverter NMOS

Allo scopo di meglio comprendere il funzionamento del transistor MOS e di presentarne un primo possibile utilizzo analizziamo il funzionamento dell’inverter

NMOS rappresentato in figura 4. Il funzionamento di principio è il seguente:

per una tensione di ingresso vi = 0 il transistor sarà interdetto e la corrente

IDS = 0. Non essendoci caduta sulla resistenza R la tensione di uscita vo risulterà pari a VDD . Per una tensione di ingresso vi = VDD il transistor sarà

in conduzione e la corente IDS comporterà un abbassamento della tensione vo .

4

Il comportamento di questo circuito è proprio quello di un inverter in cui una

tensione bassa in ingresso comporta una tensione alta in uscita e viceversa.

Come esercizio proviamo a determinare quale deve essere il valore di R tale

da avere vo = VDD

per vi = VDD

nel caso che:

2

2

W = 2L , VT n = 0.7V , µn Cox = 100µA/V 2 , VDD = 5V

In queste condizioni

βn =

µn Cox W

= 200µA/V 2

L

Poiché deve essere vo = vi = VDD

e poiché vo = VDS e vi = VGS avremo

2

anche che VDS = VGS . Questa condizione identifica la zona di funzionamento

del NMOS che è quella di saturazione. La corrente che scorre in R sarà pertanto

IDS

βn

=

2

µ

VDD

− VT n

2

¶2

= 324µA/V 2

vo = VDD − IDS R

VDD

= VDD − IDS R

2

VDD

R=

= 7.72kΩ

2IDS

Completiamo questo semplice esercizio determinando qual è il valore minimo di vo che si può ottenere. Tale valore si otterrà per il massimo valore di

IDS . Allora applichiamo il massimo valore di tensione all’ingresso: vi = VDD .

In questo caso non possiamo sapere il quale zona starà lavorando il transistor.

In ogni caso, poiché VGS − VT n = 5 − 0.7 = 4.3V e poiché ci aspettiamo che

VDS abbia un valore basso, sicuramente non saremo in zona di saturazione. In

ogni caso possiamo verificare numericamente che l’assunzione di essere in zona

di saturazione sarebbe sbagliata:

IDS =

βn

(VDD − VT n )2 = 1.85mA

2

vo = VDD − IDS R = 5 − 14.27 = −9.27V

Ovviamente non può essere vo < 0 e quindi è evidente che l’assunzione

di trovarci in zona di saturazione è sbagliata. Analogamente si verifica (con

qualche calcolo in più) che il transistor non può essere neanche in zona triodo.

Allora il transistor si trova in linearità. È cosı̀ possibile calcolare la corrente IDS .

5

vo

vi

Figura 5: Inverter NMOS: realizzazione circuitale

IDS = βn (VGS − VT n )VDS = βn (VDD − VT n )(VDD − IDS R)

IDS =

βn (VDD − VT n )VDD

4.3 · 10−3

=

= 562µA

βn (VDD − Vtn )R + 1

7.64

vo = VDD − IDS R = 5 − 4.3 = 0.7V

In realtà gli inverter NMOS vengono realizzati sostituendo alla resistenza di

pull-up un transistor PMOS come mostrato in figura 5.

6