Il transistor

•

•

•

dispositivo a semiconduttore con almeno 3 elettrodi che sfrutta le

proprietà della giunzione p-n.

inventato da Bardeen, Brattain and Shockley, ai Bell Laboratories,

nel 1948 Premio Nobel nel 1956

strutture diverse per diverse applicazioni

•

estrema miniaturizzazione sviluppo di nuove applicazioni (memorie ad

alta densità, computer veloci, computer sempre + piccoli

•

può essere schematizzato come un regolatore o generatore di corrente o

di tensione

può svolgere sia la funzione di switch (commutatore o interruttore) che

quella di amplificatore

esistono strutture diverse elaborate per diverse applicazioni

si possono individuare 2 grandi categorie di transistor in base al verso di

scorrimento della corrente rispetto alla giunzione:

– transistor bipolari a giunzione (BJT) – corrente perpendicolare alla

giunzione

– transistor ad effetto di campo (JFET o MOSFET) – corrente parallela

alla giunzione

•

•

•

Transistor Bipolare a giunzione (BJT)

p

n

n

p

p

n

emettitore

(drogaggio elevato)

collettore (drogaggio intermedio)

base (drogaggio basso)

spessore stretto

due diverse configurazioni: pnp oppure npn

base = elettrodo di controllo (switch)

piccola variazione della corrente di base rapido cambiamento nell’apparato

Il verso della corrente (convenzionalmente la direzione dei portatori di carica

positivi) è indicato dalla freccia nel terminale dell’emettitore.

Simboli convenzionali per i BJT

C

C

IC

B

IB

IC

B

IB

IE

IE

E

npn

E

pnp

due giunzioni p-n che condividono uno strato di semiconduttore intermedio drogato

due diodi contrapposti: emettitore- base

base - collettore

E

n

B

+

- - +

+

- - +

+

- - +

+

- - +

C

p

EB

BC

n

in assenza di polarizzazione esterna

EB

BC

campo elettrico

EB

distribuzione della carica elettrica

BC

potenziale elettrico

•

•

•

•

•

se polarizziamo direttamente (forward) la giunzione emettitore-base gli

elettroni (le lacune) che sono portatori maggioritari, passano nella base

dove diventano portatori minoritari. npn pnp

qui la polarizzazione inversa (reverse) della giunzione base-collettore

trascina gli elettroni (le lacune) che sono minoritari, verso il collettore,

dove sono nuovamente portatori maggioritari e rappresentano la

componente prevalente della corrente di collettore.

a causa dello spessore sottile della base pochi elettroni (le lacune) si

ricombinano con le lacune (gli elettroni) della base e in gran parte

raggiungono l’altra giunzione, cioè il collettore. A questo punto il campo

elettrico dovuto alla polarizzazione inversa accelera gli elettroni (le

lacune) nella regione di collettore.

questo significa che la corrente di collettore sarà poco diversa da quella

di emettitore e si avrà

IB = I E - IC

la corrente di base IB rimpiazza le lacune (gli elettroni) della base che si

sono ricombinati con gli elettroni (le lacune) dall’emettitore e

rappresenta un frazione piccola della corrente di emettitore.

• Possiamo descrivere il comportamento del transistor (consideriamo

per esempio un npn) anche da un altro punto di vista

• la corrente che attraversa la giunzione EB è costituita quasi

esclusivamente da elettroni che dall’emettitore arrivano nella base.

Le lacune che fanno il percorso inverso sono poche perché

l’emettitore è molto più drogato della base.

• gli elettroni nella base hanno una bassa probabilità di ricombinarsi

con le lacune perché la loro lunghezza di diffusione è maggiore

dello spessore della base.

• se indichiamo con (1- a) la probabilità di cattura di un elettrone da

parte di una lacuna nella base ( con a ≈1) un elettrone ha una

probabilità a~1 di raggiungere la giunzione BC e di attraversarla,

essendo un portatore minoritario.

• quando un elettrone viene catturato da una lacuna della base, la

batteria che alimenta la base provvede a rimpiazzare la carica libera

perduta tramite la corrente di base. Poiché la ricombinazione ha una

probabilità di (1- a), anche la corrente di base si potrà scrivere come

IB ~ (1- a) IE

corrente di collettore: IC (è la corrente che scorre effettivamente nel transistor)

due contributi:

1 - elettroni che, immessi dall’emettitore nella base, riescono a passare nel circuito

di collettore : I’C ~ a IE

2 – corrente inversa del diodo BC, Io, dovuta alla polarizzazione inversa

IC = I’C+ Io = a IE + Io

IB + IC = IE IC = Io + aIE = Io + aIB +aIC

IC = [a/(1-a)] IB + [1/(1-a)] Io

a/(1-a) = b del transistor ~ 10 ÷ 102

IC = b IB + [1/(1-a)] Io b IB

ATTENZIONE!!!

Io è molto piccolo ma è moltiplicato per un fattore ~ b ~ 10 ÷ 102

Io aumenta molto con la temperatura non può essere sempre trascurato.

In conclusione:

quando il transistor è in zona attiva (giunzione BE diretta; giunzione BC inversa)

IC = b IB

IE=IC+IB = IC + IC/ b IC

b:

- può variare molto da un transistor all’altro anche se i transistor sono

nominalmente uguali;

- varia con il “punto di lavoro”, cioè con le tensioni applicate al transistor

- varia con la temperatura

Il parametro b viene indicato con il simbolo hFE (se ci si riferisce a grandezze

variabili si usano pedici minuscoli hfe) e rappresenta il guadagno in corrente del

transistor.

Caratteristiche di uscita del transistor

descrivono la dipendenza della corrente di collettore dalla differenza di potenziale

tra collettore ed emettitore VCE

famiglia di curve corrispondenti a diversi valori della IB

3 regioni distinte:

a) zona attiva

b) zona di saturazione

c) zona di interdizione

transistor in zona attiva (VBE>Vg, VC>VB): amplificatore di corrente

piccola corrente iniettata in base controlla una corrente molto maggiore che,

in un transistor npn, attraversa il transistor nel verso C-B-E

in zona attiva la giunzione BE è polarizzata direttamente

VBE ~ 0.6 V ~Vg

nel circuito della figura: VBE=VB-RbIB

Supponiamo che VB = 2V e Rb = 28 kW

IB =[ (2 - 0.6)/28]mA = 0.05 mA

Se hFE = b = 100

Vo

~

IC = 5 mA e IE = 5.05 mA

Se VCE = 10 V, RC =1 kW la tensione sul collettore è

configurazione ad

emettitore comune

Vo = VCE –IC RC=10 -5 = 5V

Aggiungiamo in serie a VB una tensione variabile (<VB), per es. sinusoidale di ampiezza 0.5 V.

Le variazioni corrispondenti saranno:

IB1 = (2.5 -0.6)/(28 103) = 0.068 mA IC1=6.8 mA, Vo1 = (10-6.8) V = 3.2 V

IB2 = (1.5 -0.6)/(28 103) = 0.032 mA IC2=3.2 mA, Vo2 = (10-3.2) V = 6.8 V

cioè DVo = 3.6 V

DVi = 0.5 –(-0.5) = 1V il guadagno in tensione è |GV| = |DVo/DVi|=3.6

N.B.: amplificatore invertente : aumento del segnale in ingresso diminuzione

del segnale in uscita GV < 0

transistor in saturazione

giunzioni BE e BC polarizzate direttamente

VC ~ VE ~ Vg

se VCE ~ 0 anche Vo ~ 0

transistor interdetto

giunzioni BE e BC polarizzate inversamente : VBE <Vg

la corrente nel circuito è quasi nulla no caduta

potenziale ai capi di RC e quindi Vo = VCE

Vo

configurazione ad

emettitore comune

circuiti digitali

il transistor viene fatto lavorare nello stato di interdizione (Vo ~VC) e di

saturazione (Vo ~ 0V) associati allo stato logico 1 e 0 rispettivamente.

un transistor può essere adoperato

• come elemento di un circuito logico facendolo lavorare nello stato di

saturazione (VCE = 0) o di interdizione.

Infine:

perché le curve caratteristiche nella zona attiva

non sono rette orizzontali ma sono inclinate?

zona attiva : BE polarizzata direttamente

a è la frazione di elettroni che dall’emettitore

passa nel collettore, dopo avere attraversato la

base (a ~ 1, poiché la base è poco drogata ed è

stretta) b= a/(1-a) molto grande.

Riducendo ulteriormente la larghezza della base, la probabilità che un elettrone venga

catturato da una lacuna nella base, (1-a), diminuirà ulteriormente, a aumenterà e così b.

Aumentando la polarizzazione inversa della giunzione BC si allarga la zona di svuotamento

del diodo BC e diminuisce la larghezza effettiva della base.

Cioè diminuisce la probabilità che un elettrone venga catturato nella base (1-a) diminuisce

a aumenta e aumenta b

se a passa da 0.995 a 0.996 (+ 1‰), b varia da 199 a 249 (+ 25 %)

In conclusione: per IB costante il guadagno del transistor aumenta aumentando VCE le rette

non sono orizzontali ma inclinate

Analogia idraulica per il transistor

Transistor ad effetto di campo

Junction Field Effect Transistor (JFET)

Metal-Oxide-Semiconductor Field Effect

Transistor (MOSFET)

•

Dispositivi a semiconduttore a 3 terminali di facile fabbricazione e meno

ingombranti dei BJT

•

densità di componenti > 100000 MOSFET/chip

•

possono svolgere la funzione di resistenza o condensatore (collegamento

opportuno)

•

si possono progettare sistemi elettronici interamente composti da MOSFET

•

utilizzo nei VLSI

•

si può interpretare il FET come uno switch elettronico che può trovarsi in uno

stato on oppure off

•

sotto questo aspetto il FET corrisponde ad un singolo bit, cioè ad una unità

binaria di informazione

•

•

•

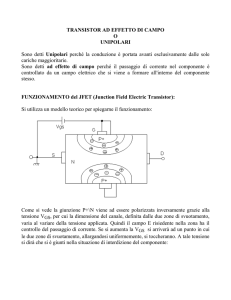

•

impiego di un campo elettrico per controllare la corrente che scorre nel

dispositivo

cristallo di semiconduttore drogato p o n (canale o body)

la corrente - dovuta solo ai portatori maggioritari - scorre tra due terminali:

sorgente (source) e pozzo (drain)

sul terzo elettrodo (gate) viene applicato un campo elettrico (potenziale) che

modifica la conducibilità del canale e quindi la corrente

Junction Field Effect Transistor (JFET)

barretta di SC a debole drogaggio n - impianto di due zone fortemente drogate p+

elettrodi metallici :

n+

Gate = elettrodo di controllo

Source

tra questi due elettrodi scorre la corrente (parallela alla giunzione)

canale p

Drain

modulata da un opportuno

potenziale

sul

gate.

Source

n+

Drain

NB : Esiste anche il JFET a canale p con l’impianto di due zone a drogaggio n+

Gate

p+

Source

Gate

canale n

p+

Drain

Che succede se aumentiamo il modulo di VGS (<0) con VDS =0?

La zona di svuotamento nel canale si allarga

e per un certo valore di VGS = VP il

canale si chiude completamente,

S

D

cioè non ci sono più cariche libere disponibili.

G

S

G

D

P

Si dice che il canale è strozzato e il valore

di VGS per cui ciò avviene è detto tensione

di pinchoff VP.

La tensione di pinchoff è pari alla ddp tra il gate ed il punto P dove il canale si

chiude completamente.

E’ possibile ottenere lo stesso effetto di strozzamento del canale anche se VGS =0

luogo dei punti di pinchoff

VGS=0

VDS

VGS=0

Aumentando VDS la ddp tra gate e canale

aumenta in modo asimmetrico, con un

G

valore maggiore verso il D

zona di

svuotamento deformata.

S

V

P

D

Continuando ad aumentare VDS si

raggiunge lo strozzamento.

VGS=0

Il punto P si trova ad un potenziale

tale per cui VGP = VP = tensione di pinchoff. G

Poiché VGS =0, VSP = VGP = VP, mentre VDP 0

quindi VDS = |VP|

S

|VP| si può definire come il valore minimo

di VDS che, per VGS =0, causa il pinchoff.

Per VDS>|VP|, IDS rimane costante

(=IDSS= corrente di saturazione).

Se VGS ≠ 0,il pinchoff si verifica per valori di VDS inferiori.

VDS

D

Aumentando VDS si osserva che la ddp tra il punto P e il source rimane uguale

a VP mentre si origina una ddp tra drain e P pari a VDS-|VP|, grazie alla quale

gli elettroni che raggiungono il punto P proseguono verso il drain.

La ddp per cui inizia la saturazione è data da V’DS VGS -VP

In questa relazione troviamo i comportamenti che abbiamo descritto finora:

per VGS = VP V’DS = 0 che produce IDS = 0 qualunque sia VDS

per VGS = 0 V’DS = VP

Anche il JFET (come il BJT) può essere usato come amplificatore nella zona

di saturazione.

Si controlla una corrente con un segnale di tensione (nel BJT si controlla una

corrente con un’altra corrente più piccola).

zone di funzionamento del JFET

costante legge di Ohm

1. zona ohmica: VDS è piccola e il canale è ancora aperto.

|VP|

VGS=0

IDS = Kp [2(VGS-VP)VDS –V2DS] Kp [2(VGS-VP)VDS]

con 0 < VDS≤(VGS-VP)

Kp =

IDSS/V2P

per VDS<<|VP|

2. zona di saturazione: VDS>(VGS –VP), IDS costante.

IDS=Kp(VGS-VP)2 dove VP ≤VGS ≤0

Il luogo dei punti di pinchoff (separazione tra zona

ohmica e di saturazione) si ottiene ponendo VGS = VDS +VP

IDS = KpV2DS = eq.parabola

3. zona di interdizione: VGS < VP (con VP<0).

In questa zona IDS =0.

4. zona di breakdown: VDS è così elevata da causare un brusco aumento della corrente ed

eventualmente la rottura del transistor.

Metal-Oxide-Semiconductor Field EffectTransistor

(MOSFET)

• Il MOSFET è un dispositivo a effetto di campo che utilizza un

elettrodo metallico separato da un canale di semiconduttore tramite

uno strato di ossido (isolante) (struttura metallo-ossidosemiconduttore)

• Applicando una ddp tra gate e substrato del semiconduttore (body),

attraverso lo strato di ossido, si controllano le caratteristiche del

canale.

• Esistono 2 tipi di MOSFET

– ad arricchimento

– a svuotamento

MOSFET a canale n ad arricchimento (n channel enhancement – NMOS)

2 regioni n+ in un substrato di tipo p

superficie superiore ricoperta di Ossido di Silicio, a parte 2 contatti metallici

(Al) per le zone n+ (Source e Drain). Il Gate si trova sullo strato di Ossido,

sulla zona inferiore c’e’un quarto elettrodo di Substrato.

Normalmente S e Substrato sono tenuti insieme. Il G è ad un potenziale positivo

rispetto a S, come pure il D.

In assenza di potenziali esterni alcuni

elettroni migrano dalle zone n+ verso p.

Applichiamo VG > VS(=Vsub) gli elettroni

vengono attirati nella zona tra D e S

creando un canale di conduzione.

Applicando una VDS si avrà una corrente

IDS da D a S.

Tutto ciò avviene se VGS ≥ Vt

(tensione di soglia).

Il comportamento del MOSFET per

VDS piccola è analogo a quello del JFET in

zona ohmica.

1. zona ohmica (VDS ≤VGS-Vt):

IDS = Kp [2(VGS-Vt)VDS –V2DS]

2. zona di saturazione (VDS ≥ VGS-Vt):

IDS = Kp (VGS-Vt)2

per VGS=0, IDS= Kp Vt2 = IDSS=

corrente di saturazione (≈ nA)

Esiste il MOSFET a canale p ad arricchimento

nel quale tutti i segni e le polarizzazioni sono

invertiti, ma ha un funzionamento del tutto

analogo.

IDS, mA

Aumentare il valore di VDS equivale a

diminuire la ddp tra D e G in prossimità

del D il canale si deforma e si restringe

vicino al D.

Quando VDS è tale per cui VDG<Vt

(VDG = VGS –VDS ≤ Vt) si ha una situazione di

pinchoff analoga a quella vista nel JFET.

IDS diventa indipendente da VDS

zona di saturazione del MOSFET

Aumentando ulteriormente VDS si raggiunge

la zona di breakdown (10÷ 100 V).

VGS= 6 V

400

VGS= 5.5 V

VGS= 5 V

VGS= 4.5 V

VGS= 4 V

300

200

100

0

0

1

SB

p

2

3

4

S GG (+)

(metallo)

n

5

D

D(+)

-- -- -- -- -- - - n

p

---

substrato

substrato

n p

VDS,V

MOSFET a canale n a svuotamento

E’ identico al transistor NMOS appena visto,

ma esiste già un canale n di conduzione

tra le regioni n+.

Quindi anche in assenza di tensione sul G

ci sarà conduzione.

• Se il G ha un potenziale negativo rispetto

al S ( e al substrato, che sono collegati)

gli elettroni nella zona n vengono respinti

si formerà una zona di svuotamento

e quindi si avrà un restringimento del canale

modo di svuotamento

• Se G ha un potenziale positivo, altri elettroni

saranno attratti verso lo strato di ossido e si

avrà un allargamento del canale ed un aumento

della conduttanza

modo di arricchimento

Supponiamo di operare in modo di svuotamento (VG < 0)

Aumentando VDS si incontrerà una prima zona ohmica, seguita anche in questo

caso da una zona di saturazione dovuta allo stesso effetto di strozzamento già

visto in precedenza.

Vp è il valore minimo di VDSche causa la saturazione quando VGS=0 ( ed è il

valore di VGS che causa il pinchoff quando VDS=0).

La curva caratteristica di questo MOSFET è:

Saturazione: VDS tale per cui

VGD = VGS –VDS = VP cioè VDS = VGS-VP

1. zona ohmica (0 <VDS ≤VGS-Vp):

IDS = Kp [2(VGS-Vp)VDS –V2DS]

2. zona di saturazione (VDS ≥ VGS-Vp):

IDS = Kp (VGS-Vp)2

NMOS

PMOS

dispositivi CMOS

+VDD

Q2

carico

PMOS

vi

+

vo

pilota

NMOS

Q1

PMOS e NMOS entrambi ad arricchimento

connessi in serie

terminali D (Drain) collegati in serie

tensione di uscita dal nodo dei D

Gate comune. Al G viene applicato il segnale di

ingresso.

la tensione di ingresso può variare da

V(0) = 0 a V(1) = VDD

Se vi <VT NMOS in interdizione

PMOS in conduzione

vo

PMOS

NMOS

tensione di ingresso è bassa

tensione di uscita è alta ed è pari a VDD

per vi =0 si ha VGS1 = 0 Q1 è interdetto

VGS2 = -VDD Q2 è acceso, ma la corrente è nulla

VDS2 =0 e vo= VDD

vi = V(0) vo = V(1)

+VDD

Q2

carico

PMOS

vi

+

vo

-

poiché D e S dei due transistor sono in serie nel

canale del NMOS non passa mai corrente

utilizzato in applicazioni digitali

pilota NMOS al quale è connesso un PMOS come carico.

Supponiamo che la tensione di soglia sia la stessa ed

uguale a VDD/2.

Ricordate che NMOS conduce se VGs >0

e PMOS conduce se VGs< 0

pilota

NMOS

Q1

per vi = VDD = VGS1 Q1 è acceso

VGS2 = 0 Q2 è spento

la corrente è nulla

e quindi vo= 0

vi = V(1) vo = V(0)

Se vi >VT NMOS in conduzione

PMOS in interdizione

+

PMOS

vo

-

NMOS

tensione di ingresso alta

tensione di uscita è bassa

Un circuito di questo tipo rappresenta un invertitore, cioè una porta logica NOT