ESAME DI MATURITA’ TECNICA INDUSTRIALE

Sessione Ordinaria: 1986

Seconda Prova Scritta: tema di ELETTRONICA GENERALE

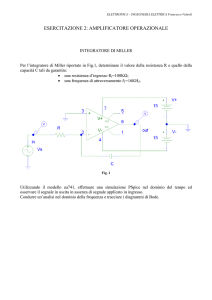

ESERCIZIO 1

Nello schema in Fig.86-1, l'amplificatore operazionale, supposto ideale, è alimentato con tensione duale : ± 15 V.

R = 39 kΩ; hFE = 100; C = 100 nF; VBEsat = 0,7 V; RB = 8,2 kΩ; VCEsat = 0 V.

Il candidato determini:

1) la relazione che lega il segnale di uscita Vo(t) al segnale di ingresso VA(t) nell'ipotesi che VB (t) sia uguale a zero e la tensione ai capi del

condensatore C sia nulla all'istante di applicazione di VA(t);

2) il diagramma temporale del segnale di uscita Vo(t) nell'ipotesi che all'ingresso A sia applicato un segnale a gradino di ampiezza EA = 10 V,

all'ingresso B un segnale VB (t) sempre uguale a zero e il condensatore C sia inizialmente scarico;

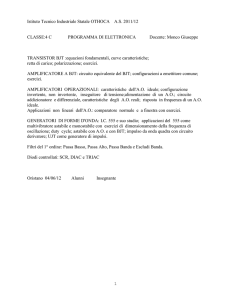

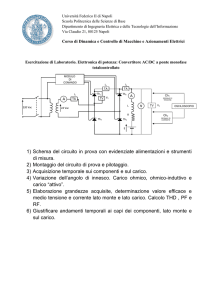

3) il diagramma temporale del segnale di uscita Vo (t) nell'ipotesi che all'ingresso A sia applicato un segnale a gradino di ampiezza EA = 10 V nello

stesso istante in cui all'ingresso B è applicato un segnale impulsivo avente le caratteristiche della Fig. 86-2 e che il condensatore C sia

inizialmente scarico.

ESERCIZIO 2

Il candidato realizzi un circuito logico che permetta di effettuare la somma di due numeri binari da un bit ciascuno e che presenti, oltre all’uscita

somma, anche quella di riporto.

Sfruttando il circuito ottenuto, il candidato realizzi un sommatore completo per numeri a 4 bit.

fig. 86-1

fig. 86-2

Traccia di soluzione ⋅

ESERCIZIO 1

1) Analisi del testo

2) Schema a blocchi complessivo

3) Scelta delle soluzioni tecniche

4) Studio approfondito dei blocchi

Punto 1 – poiché viene ipotizzato che VB = 0, il BJT è interdetto e il

circuito si riconduce ad un integratore non invertente (che,

considerando la saturazione dell’amp.op., equivale a un filtro passaalto);

Punto 2 – si richiede l’applicazione di un ingresso a gradino al circuito

del punto 1 (le ipotesi sono le stesse); poiché è un integratore, si

utilizzano i metodi delle L-trasformate per l’analisi dell’uscita;

Punto 3 – durante il livello basso del segnale VB (VB = 0), il circuito

coincide con quello analizzato nei punti 1 e 2; quando VB è a livello alto,

il BJT satura e, poiché è dato VCEsat = 0 V, il condensatore C viene

cortocircuitato.

Coincide con il circuito dato

Si ipotizza l’amp.op. ideale; i valori dati per il BJT permettono di

determinare la corrente IC = hFE IB.

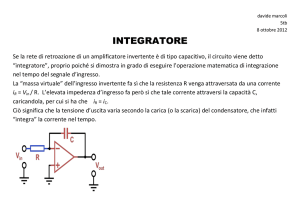

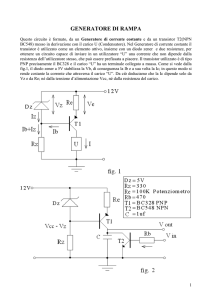

Punto 1 – In fig. 86-3 è riportato il circuito utilizzabile per la soluzione dei

punti 1 e 2. Per individuare il comportamento di filtro (integratore non

invertente), si ricavano separatamente i potenziali v- e v+, eguagliandoli

e ricavando l’uscita:

al morsetto invertente: v- = vo / 2;

al morsetto non invertente: si ricava l’equilibrio delle correnti al

v + vo

v+ = A

punto v+, da cui risulta:

2 + sRC ;

2

v = vA ⋅

osservando che v- = v+, si ricava: o

sRC , che

conferma il comportamento di integratore non invertente

attribuito al circuito.

Punto 2 – Il gradino d’ingresso, L-trasformato, fornisce: VA = 10/s;

-

fig. 86-3

l’uscita è:

Vo =

20

s 2 RC (in L-trasformata).

20

v (t ) =

⋅t

Antitrasformando: o

(rampa lineare).

RC

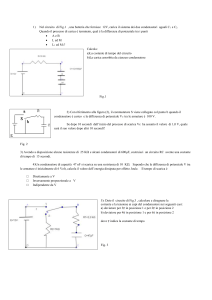

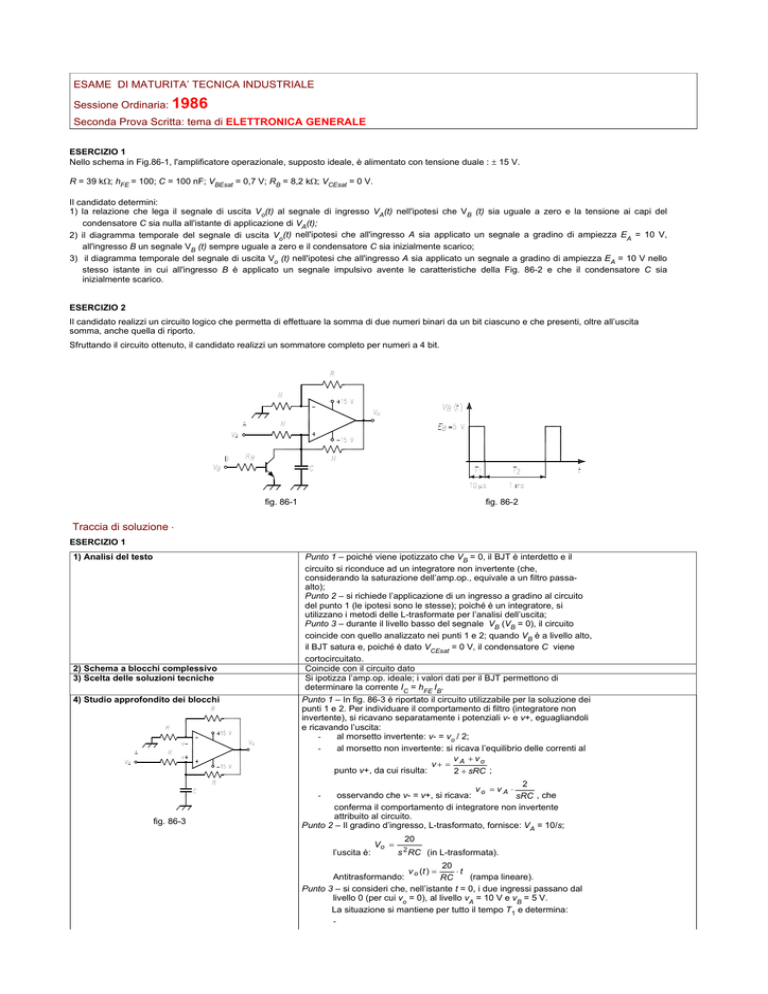

Punto 3 – si consideri che, nell’istante t = 0, i due ingressi passano dal

livello 0 (per cui vo = 0), al livello vA = 10 V e vB = 5 V.

La situazione si mantiene per tutto il tempo T1 e determina:

-

la saturazione del BJT, con VCEsat = 0 V, per cui il

condensatore, cortocircuitato, si mantiene scarico;

-

fig. 86-4

la tensione d’uscita rimane vo = 0.

Terminato il tempo T1 e per tutto il tempo T2, il BJT interdice e la

tensione d’uscita vale, come già individuato:

2E A

⋅t

v o (t ) =

, ovvero sale con legge lineare.

RC

Al successivo fronte di salita di vB il BJT satura di nuovo, ma il

condensatore si deve scaricare e lo fa con legge lineare.

Al termine, vo torna a zero e il ciclo riprende, come descitto in

fig. 86-4.

ESERCIZIO 2

1) Analisi del testo

2) Schema a blocchi complessivo

3) Scelta delle soluzioni tecniche

4) Studio approfondito dei blocchi

Viene richiesto di realizzare un semisommatore (Vol. 1, par.5.6.1), per

poi utilizzarlo nella realizzazione di un sommatore completo (Vol. 1,

par.5.6.1), al fine di ottenere il riporto.

Si analizza la struttura del semisommatore, poi del sommatore

completo. Infine, ponendo in serie 4 sommatori completi a un bit, si

ottiene un sommatore a 4 bit

Si possono utilizzare integrati di tipo TTL (7483 – 4-Bit full adder)

Si suggerisce di ricavare l’implementazione del semisommatore e del

sommatore completo, a partire dalla tabella di verità.