Relazione.

Esito delle simulazioni degli schematici discussi nella parte teorica che

sfruttano i BJT

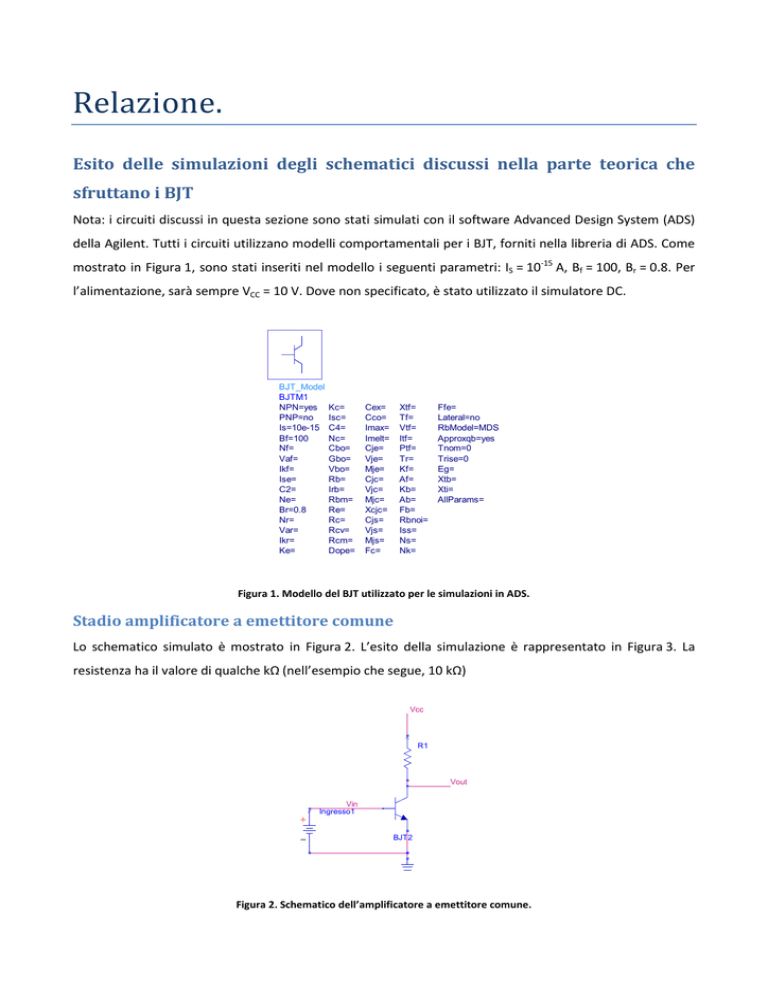

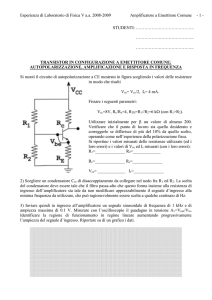

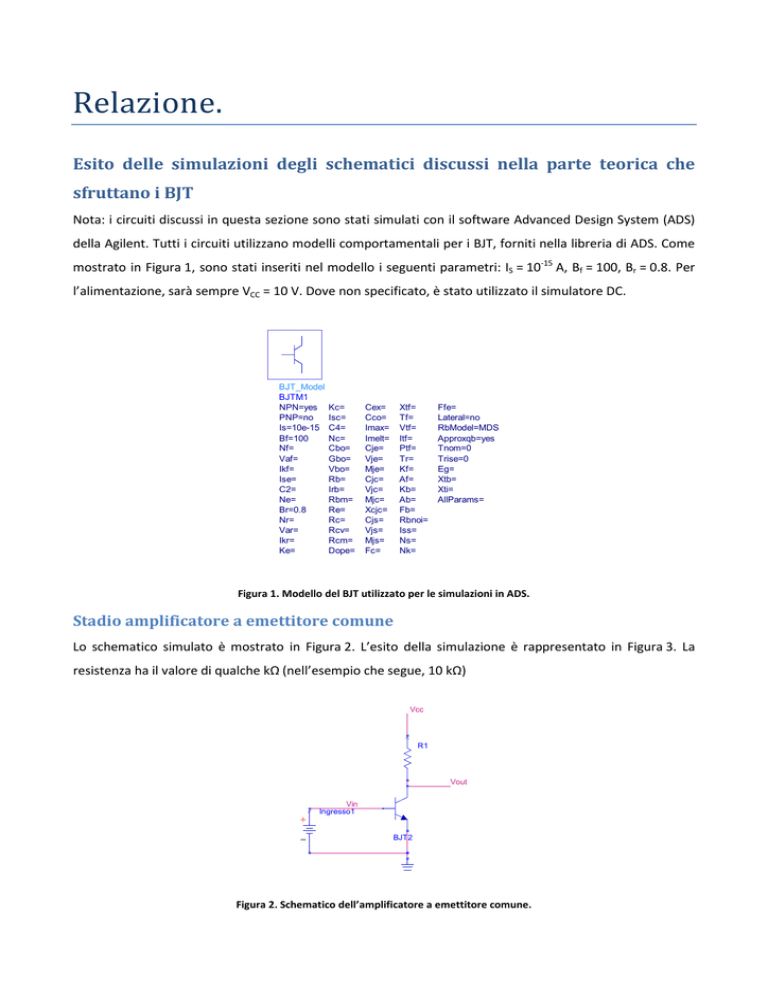

Nota: i circuiti discussi in questa sezione sono stati simulati con il software Advanced Design System (ADS)

della Agilent. Tutti i circuiti utilizzano modelli comportamentali per i BJT, forniti nella libreria di ADS. Come

mostrato in Figura 1, sono stati inseriti nel modello i seguenti parametri: IS = 10-15 A, Bf = 100, Br = 0.8. Per

l’alimentazione, sarà sempre VCC = 10 V. Dove non specificato, è stato utilizzato il simulatore DC.

BJT_Model

BJTM1

NPN=yes

PNP=no

Is=10e-15

Bf=100

Nf=

Vaf=

Ikf=

Ise=

C2=

Ne=

Br=0.8

Nr=

Var=

Ikr=

Ke=

Kc=

Isc=

C4=

Nc=

Cbo=

Gbo=

Vbo=

Rb=

Irb=

Rbm=

Re=

Rc=

Rcv=

Rcm=

Dope=

Xtf=

Tf=

Vtf=

Itf=

Ptf=

Tr=

Kf=

Af=

Kb=

Ab=

Fb=

Rbnoi=

Iss=

Ns=

Nk=

Cex=

Cco=

Imax=

Imelt=

Cje=

Vje=

Mje=

Cjc=

Vjc=

Mjc=

Xcjc=

Cjs=

Vjs=

Mjs=

Fc=

Ffe=

Lateral=no

RbModel=MDS

Approxqb=yes

Tnom=0

Trise=0

Eg=

Xtb=

Xti=

AllParams=

Figura 1. Modello del BJT utilizzato per le simulazioni in ADS.

Stadio amplificatore a emettitore comune

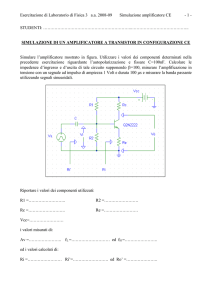

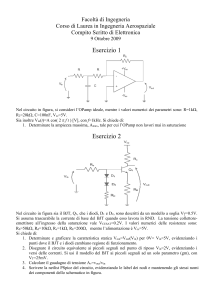

Lo schematico simulato è mostrato in Figura 2. L’esito della simulazione è rappresentato in Figura 3. La

resistenza ha il valore di qualche kΩ (nell’esempio che segue, 10 kΩ)

Vcc

R1

Vout

Vin

Ingresso1

BJT2

Figura 2. Schematico dell’amplificatore a emettitore comune.

Figura 3. Esito della simulazione.

Quello che si vede da Figura 3 è che in saturazione l’uscita non è costante, ma aumenta leggermente

all’aumentare dell’ingresso. Il comportamento in regione lineare, dove il circuito è utilizzato effettivamente

per amplificare, è prossimo a quello atteso, come mostra Figura 4.

Figura 4. Caratteristica d’uscita: dettaglio in regione lineare.

Quello che si vede da Figura 4 è che, se il BJT è polarizzato con una tensione di ingresso nell’intervallo

rappresentato sulle ascisse, un piccolo segnale sinusoidale sovrapposto a tale bias subisce una notevole

amplificazione.

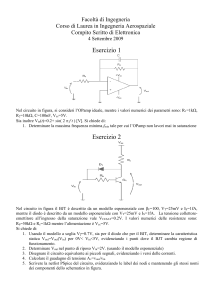

Stadio amplificatore a emettitore comune a doppio carico

Lo schematico simulato è quello in Figura 5. Figura 6 mostra l’uscita del circuito se le due resistenze valgono

10 kΩ. Come si può notare, la pendenza in regione lineare è pari al rapporto tra resistenza di collettore RC e

resistenza di emettitore RE invertito di segno, ovvero, -1.

Aumentando RE di un fattore 10 si ha una riduzione dello stesso fattore della pendenza nella regione

lineare, come mostra Figura 7.

Vcc

R

Vout

Vin

BJT1

Ingresso

R1

Figura 5. Schematico dello stadio amplificatore a emettitore comune con doppio carico.

Figura 6. Risposta dello stadio amplificatore a emettitore comune con doppio carico.

Figura 7. Modulazione del guadagno dello stadio amplificatore agendo sul rapporto tra RC e RE.

Stadio amplificatore con collettore comune

Lo schematico è mostrato in Figura 8. L’uscita è mostrata in Figura 9: l’andamento è molto prossimo a

quello atteso.

Vcc

Vin

Ingresso BJT1

Vout

R1

Figura 8. Schematico dello stadio amplificatore a collettore comune.

Figura 9. Risposta dello stadio amplificatore a collettore comune.

Stadio amplificatore con base comune

Schematico e risposta sono mostrati rispettivamente in Figura 10 e Figura 11.

Vout

Vcc

Vin

R1

Ingresso

BJT1

Figura 10. Schematico dello stadio amplificatore a base comune.

Figura 11. Risposta dello stadio amplificatore a base comune.

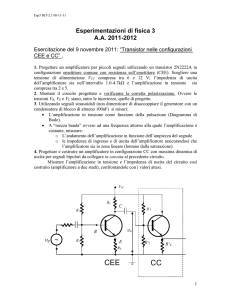

Invertitore RTL

Schematico e risposta sono rappresentati in Figura 12 e Figura 13. Si è supposto: RE = RB = 10 kΩ.

Vcc

R1

Vout

Vin

Ingresso

R2

BJT1

Figura 12. Schematico dell’invertitore RTL.

Figura 13. Risposta dell’inverter logico.

NOR RTL

Lo schematico del NOR RTL, in accordo alla teoria, sfrutta la cascata di due inverter RTL ed è mostrato in

Figura 14. Ciascun inverter è esattamente lo stesso di Figura 12. Per poterne verificare il corretto

comportamento e il rispetto della tabella della verità, è necessario effettuare un’analisi transient (non DC),

facendo variare gli ingressi nel tempo, in modo che assumano le quattro possibili configurazioni. L’uscita del

NOR sarà alta solo in un caso: quando entrambi gli ingressi sono bassi. Figura 15 mostra che effettivamente

il circuito di Figura 14 si comporta da NOR. Derivare un OR a partire da tale configurazione è banale: sarà

sufficiente mettere in cascata al NOR un inverter RTL che abbia come ingresso l’uscita del NOR (vedasi

Figura 16 e Figura 17 per il relativo schematico e simulazione rispettivamente).

Vcc

R1

Vout

Vin1

SRC3

Vin2

SRC4

R3

t

BJT2

R2

t

BJT1

Figura 14. Schematico del NOR RTL.

Figura 15. Esito della simulazione transient del NOR RTL: a sinistra sono rappresentati i due ingressi, a destra l’uscita.

Vcc

Vcc

R5

R1

VoutOR

VoutOR

R4

Vin1

SRC3

t

R3

BJT2

Vin2

SRC4

BJT3

R2

t

BJT1

Figura 16. Schematico dell’OR RTL.

Figura 17. Esito della simulazione transient dell’OR RTL: a sinistra sono rappresentati i due ingressi, a destra l’uscita.

Esercizio: stadio amplificatore a collettore comune a doppio carico con BJT pnp

Schematico ed uscita sono proposti in Figura 18 e Figura 19 rispettivamente.

Vcc

R2

Vin

Ingresso

BJT1

Vout

R1

Figura 18. Schematico dello stadio amplificatore a collettore comune con doppio carico basato su BJT pnp.

Figura 19. Uscita dello stadio amplificatore a collettore comune con doppio carico basato su BJT pnp.

Esercizio: rappresentazione della caratteristica ingresso-uscita

Il circuito in esame è rappresentato in Figura 20, mentre Figura 21 ne mostra la caratteristica d’uscita al

variare dell’ingresso. Si noti che per il modello del diodo Zener è stata assunta una IS = 10-15 A e una

tensione di Zener BV = 7 V. Il BJT è ancora di tipo pnp.

Vcc

R2

Vin

Ingresso

BJT1

Vout

DIODE1

R1

Figura 20. Schematico del circuito in esame.

Figura 21. Risposta del circuito in Figura 20.