Università di Bologna, Facoltà di Ingegneria

Corso di Laurea in Ingegneria Elettronica

Esercitazioni di E LETTRONICA L-C

Anno Accademico 2001/2002

Esercitazione N. 3

31 Maggio 2002

Questa esercitazione prevede la progettazione e la simulazione di un oscillatore (quasi) sinusoidale

che utilizza un amplificatore a controllo automatico di guadagno (AGC).

Il lavoro di laboratorio svolto precedentemente ha messo in evidenza come per realizzare oscillatori che producono forme d’onda a basso contenuto armonico (poco distorte) è indispensabile utilizzare

filtri molto selettivi oppure fare operare l’elemento attivo (cioè l’amplificatore) lontano dalla regione

di saturazione, dove la sua non-linearità è meno marcata. È anche stato osservato che per soddisfare

quest’ultima condizione spesso si giunge a dimensionamenti critici, in cui la robustezza dell’oscillatore alla variazione dei parametri dei dispositivi non è soddisfacente. In particolare, si rischia che

piccolissime variazioni dei parametri provochino ampie fluttuazioni dell’ampiezza dei segnali, il che

è indesiderabile.

Problemi di questa natura possono essere risolti introducendo ulteriori meccanismi di retroazione

per controllare l’ampiezza dell’oscillazione. A titolo di esempio, in questa prova viene utilizzato

un elemento attivo a controllo automatico di guadagno, in cui la pendenza della caratteristica statica

nella regione di lavoro viene adattata continuamente al fine di ottenere un segnale di uscita di ampiezza

prefissata.

Obiettivi dell’esercitazione:

1. Verificare i concetti appresi a lezione sul progetto di oscillatori. In particolare, nel sistema oggetto di questa prova è indispensabile introdurre opportune approssimazioni per poter applicare

le metodologie di analisi note.

2. Affrontare le problematiche di progetto relative a blocchi circuitali quali amplificatori a

guadagno controllabile elettronicamente e rivelatori di cresta.

3. Realizzare un controllo automatico di guadagno (che può essere utile nel progetto di oscillatori,

ma anche in una varietà di problemi di signal processing).

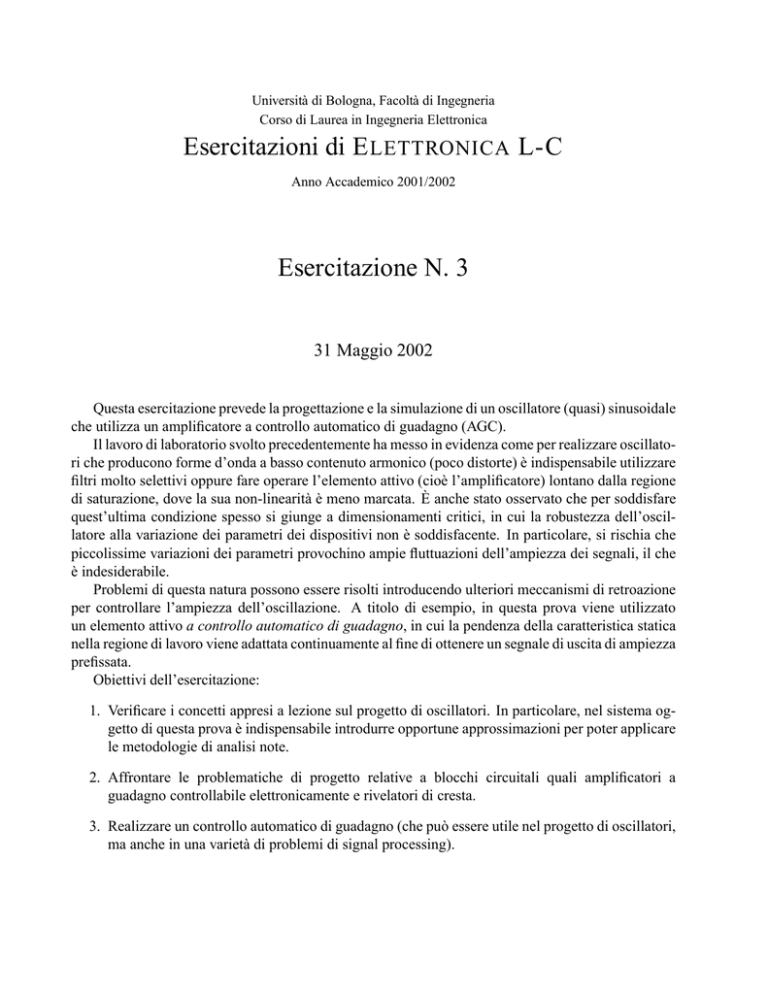

Progetto dell’oscillatore

Lo schema a blocchi del sistema oggetto della prova viene fornito alla figura seguente:

FILTRO BP

Amplificatore controllato

non lineare e

non reattivo

Vx (t)

Vy (t)

vy (t) = k f(vx (t))

k

(imposizione

dell’ampiezza

desiderata

dell’oscillazione)

Vref

Circuito di

controllo

del guadagno

(la costante "k" e’

rappresentata da una

corrente di polarizzazione

dell’amplificatore)

Vy (t)

Verr

+

Σ

FILTRO LP

−

vA (t)

vM (t)

Rilevatore

di cresta

Figura 1: Schema a blocchi equivalente di un oscillatore quasi sinusoidale con AGC.

Nel seguito, verranno realizzati individualmente i vari blocchi e poi si provvederà a comporli per

simulare il sistema complessivo.

Progetto dell’amplificatore controllato elettronicamente

Occorre progettare un amplificatore il cui guadagno possa essere variato con continuità soddisfacendo

i seguenti requisiti:

1. Il guadagno deve poter essere variato agendo su di una grandezza elettrica (per esempio una tensione/corrente di polarizzazione) e non i parametri di un componente (per esempio la resistenza

di un resistore). In questo modo si realizza un circuito il cui guadagno può essere modificato

da un altro circuito;

2. Il legame tra il guadagno ed il parametro che lo controlla deve per quanto possibile essere

continuo e lineare;

3. L’azione sul parametro che controlla il guadagno deve avere un effetto piccolo o addirittura

nullo sulla tensione di uscita a riposo dell’amplificatore.

La cella differenziale (figura 2) si presta a realizzare un sistema di questo tipo. Infatti, il guadagno

è direttamente proporzionale alla corrente di polarizzazione

e, per la è (quasi)

indipendente dalla .

Per poter utilizzare la cella amplificatrice nell’anello a controllo automatico di guadagno, occorre

avere un segnale di uscita di almeno qualche Volt di ampiezza, in modo che il rivelatore di cresta possa

operare correttamente. Dunque, bisogna progettare la cella in modo tale che possa fornire tensioni

di uscita ampie, pur rimanendo lontano dalla saturazione. A tal fine si impone come specifica di

2

Vcc = 5V

N1

Q3

Q4

Ibias

Vout

N2

Vin

Q1

Q2

E

Rc

I0

Figura 2: Amplificatore a guadagno controllabile elettronicamente.

progetto un guadagno nominale più grande di quello utilizzato nelle esercitazioni precedenti (

). Come nelle esercitazioni precedenti, si assume che l’amplificatore sia caricato da un filtro con

impedenza di ingresso di alla pulsazione di risonanza.

1. Stabilito che si hanno transistor con !"" ed effetto Early trascurabile, che la temperatura

%$"&

può essere assunta pari a # ( ('*) +-,/. ) e che si vuole controllare il guadagno

modificando intorno al valore nominale di 0,21 , si dimensioni la cella in maniera che in

presenza del carico (assunto in condizioni di risonanza) siano soddisfatti i seguenti requisiti:

(a) con 3

4 la tensione di uscita sia 5

4+6. ;

(b) il guadagno sia pari a 5

.

2. Si verifichi con Spice che il guadagno è controllabile elettronicamente, effettuando opportune

8

0,21 ,

,71 e

:9,21 .

analisi AC per per 3. Per gli stessi valori di , si traccino le caratteristiche statiche dell’amplificatore. Si verifichi

che il il punto di riposo che corrisponde a ;<=

> non varia in maniera significativa al variare

8

di .

4. Con le stesse caratteristiche statiche, si controlli la possibilità di avere tensioni in uscita

comprese tra 6. e ?0. senza che l’amplificatore si avvicini troppo alle regioni di saturazione.

Progetto del filtro passa-banda

La figura 3 mostra lo schema del filtro passa banda da adottare, che è lo stesso delle esercitazioni

precedenti.

Rispetto alle esercitazioni precedenti, bisogna ora dimensionare il filtro in modo che abbia

un’attenuazione più forte. Infatti, si vuole che l’attenuazione sia uguale al guadagno nominale

dell’amplificatore.

5. Si dimensionino @BA , @C , D5A e EFA in modo da soddisfare i seguenti requisiti:

3

Vin

Vout

L1

R1

C1

R2

Figura 3: Schema del filtro passa banda.

(a) Frequenza di risonanza G

"HJIK ;

(b) Impedenza di ingresso alla frequenza di risonanza ;

(c) Fattore di merito LM

>+ .

(d) Attenuazione alla frequenza di risonanza pari a AONQP R0SUT CWVYXZ[ P .

Si ricordi a questo proposito che la forma canonica di un filtro passa banda del second’ordine

è:

\^]Z_%`

g

>ba;cedFf 3j

h(i g j

hki gml

i n

6. Si effettuino le analisi Spice AC necessarie a verificare il soddisfacimento dei requisiti di

progetto.

Progetto del rivelatore di cresta

Il circuito in figura 5 realizza un rivelatore di inviluppo a singola semionda (rivelatore di cresta).

Vin

D

Vout

R

C

Figura 4: Circuito rilevatore di cresta, realizzato a componenti discreti.

Si assuma @o

0HJ .

7. Si dimensioni E in maniera tale che per un segnale di ingresso sinusoidale di ampiezza

qpO+-. , offset Jpr+6. e frequenza G HJIK si abbia un ripple in uscita inferiore all’1–2 %

"

dell’ampiezza dell’oscillazione.

8. Si verifichi la correttezza del dimensionamento di E

simulazione in transitorio.

4

ed il funzionamento del circuito con una

9. Sempre nell’analisi in transitorio, si tracci l’andamento della corrente di ingresso del circuito.

10. Si ripeta l’analisi in transitorio inserendo un resistore da HJ tra la sorgente ed il rivelatore di

cresta. Il comportamento della tensione di uscita cambia?

11. Si ripeta l’analisi in transitorio caricando il rivelatore con un resistore da

comportamento della tensione di uscita cambia?

0HJ .

Il

12. Alla luce degli ultimi tre risultati, si dica perché è opportuno circondare il rivelatore di cresta

con due buffer, come mostrato alla figura seguente:

−

D

−

+

Vin

Vout

+

R

C

Figura 5: Circuito rilevatore di cresta, con ingresso e uscita bufferizzati.

13. Si realizzino i buffer ad operazionale, utilizzando uno dei noti modelli dell’OpAmp, ad

esempio:

.SUBCKT OPAMP INP INN OUT PARAMS: VUMP=10 VUMN=-10 AD=100K

EOA OUT 0 VALUE={MAX(MIN(AD*V(INP,INN),VUMP),VUMN)}

.ENDS

Progetto del circuito di condizionamento del segnale all’uscita del rivelatore di

cresta

Si faccia riferimento allo schema a blocchi mostrato all’inizio. Il circuito di condizionamento del

segnale di uscita del rivelatore di cresta deve applicare un filtraggio passa basso per ottenere s che

è un’indicazione lentamente variabile dell’ampiezza del segnale e poi, da questa, deve ricavare una

tensione di errore ;teuvuw

4;utyx{z|s .

Un’operazione di questo genere può essere realizzata con lo schema in figura 6.

VM

VA

RF

Verr

EF

Verr=Vref-VA

CF

Figura 6: Circuito di condizionamento del segnale all’uscita del rivelatore di cresta.

5

Si noti che l’operazione di differenza potrebbe venire realizzata con un amplificatore differenziale

ad operazionali, piuttosto che con il generatore comandato ideale mostrato in figura. Purtroppo l’introduzione dell’operazionale e delle relative resistenze porterebbe poi ad avere un numero di componenti

eccessivo per la simulazione con la versione evaluation di PSPICE.

0HJ , si dimensioni la capacità per avere una frequenza di taglio pari a

14. Posto @}

(cioè molto più piccola della frequenza di oscillazione).

HJIFK

15. Si facciano le necessarie verifiche con un’analisi AC e Spice per controllare la correttezza del

dimensionamento.

Generazione della corrente di controllo per l’amplificatore a guadagno

controllato

Per chiudere l’anello di controllo automatico di guadagno, occorre generare una corrente proporzionale alla tensione di errore, da applicare al nodo di emettitore della cella differenziale, come mostrato

alla figura seguente:

Vin

Q1

Q2

I’0

I controllo

gC < 0

g C.Verr

I 0= 10mA

Figura 7: Conversione della tensione di errore nella corrente di controllo della cella differenziale.

Si assume inizialmente un valore di transconduttanza ~ per il generatore comandato pari a

- N .

Chiusura degli anelli di retroazione

Definiti i vari blocchi funzionali si tratta ora di simulare il circuito completo, comprensivo dei due

anelli di retroazione. Si ponga utrx

(pO?-. e si effettuino le analisi in transitorio necessarie a

rispondere ai seguenti quesiti:

16. Si determini la tensione di uscita del circuito filtrante s , quando il sistema è a regime.

17. Si determini l’ampiezza delle oscillazioni all’uscita della cella differenziale (segnale k ) e si vej

rifichi che è circa uguale a ;utrx (z/+6. , dove ( è la tensione di soglia del diodo che compare

nel rivelatore di cresta e i +-. sono il valore di riposo della tensione all’uscita dell’amplificatore.

18. Si verifichi la THD del segnale all’uscita dell’amplificatore e si controlli che è soddisfacente.

6

19. Si provi a variare qualche parametro del sistema di 3 e si verifichi che il sistema è robusto

per quanto riguarda la sua capacità di oscillare e l’ampiezza delle forme d’onda.

$

20. Si porti utyx a prima a (p0. e poi a rp 6. . Si verifichi che il circuito continua a produrre

j

(z+6. . Entro quale intervallo di valori deve stare utyx perché

oscillazioni di ampiezza ;utrx

il circuito operi correttamente?

21. Si provi a simulare il circuito in transitorio con una utyx che varia lentamente nel tempo e si

verifichi che l’oscillatore traccia correttamente la ; con l’ampiezza delle proprie forme d’onda.

22. Si determini se esistono valori della transconduttanza ~" che conducono il sistema a smettere

di comportarsi come un oscillatore sinusoidale.

Controllo effettuato mediante amplificatore push-pull a transistor MOS (facoltativo)

Senza ricorrere ad un generatore comandato, è possibile ottenere direttamente la corrente

partire dalla tensione di errore ;teuvu utilizzando lo schema seguente, visto a lezione:

Q1

Ou< a

Vdd

Q2

M1

I’0

Verr

I controllo

I0

M2

Vee

$

$

C

Posto che i transistor sono caratterizzati da ('(

(p , ('q4

}zqp , 0;1 N . , C

?0;1 N .

e che D

0;, ,

23. Si determinino analiticamente i valori da attribuire a , gZg , ¡ e per avere

ru< )o , quando tmuvuw

4-. .

¢£O¤¦¥Z§U¨O¤¦© © ¤

(b) «ª­¬ ¨y¨ )

-

N per ;teuvu3

>0. .

(a)

]

`

24. Si utilizzi un’analisi DC per verificare che la caratteristica ru ;teuvu non sia troppo dissimile da quella ottenuta con il generatore ideale nella sezione precedente, almeno in un intorno

di ;teuvu

4-. .

25. Si simuli l’intero oscillatore in transitorio, utilizzando questa soluzione per controllare il

guadagno della coppia differenziale.

7

A cura di: Ing. A. Leonardi,

Ing. S. Callegari.

NETLIST

Test oscillatore quasi sinusoidale con agc

* Giusto per avere VT=25mV, il che semplifica i conti

.temp 17

.options tnom=17

* Modelli dei dispositivi impiegati

.model TRNPN NPN BF=200

.model TRPNP PNP BF=200

.model DIODE D

* Un modello di amplificatore operazionale

.subckt opamp inp inn out params: ad=100K vump=10 vumn=-10

E1 out 0 value={min(max(ad*v(inp,inn),vumn),vump)}

.ends

* tensioni di alimentazione

vcc cc 0 dc 10

vee ee 0 dc -1

* riferimento ampiezza segnale (vref è l’ampiezza che voglio avere

* tolgo una tensione di soglia, perchè anche il rivelatore di picco

* lo fa)

vref ref 0 dc 7.5

dref ref refi DIODE

rref refi 0 500k

* Amplificatore differenziale a guadagno controllato elettricamente

* il guadagno è proporzionale a ggain e vale 100 quando la corrente

* su ggain è 10mA ed il sistema ha un carico di 500 Ohm.

Q1 c1 x e TRNPN

Q2 yi 0 e TRNPN

Q3 c1 c1 cc TRPNP

Q4 yi c1 cc TRPNP

ggain e 0 value={10m-(v(zz)-v(refi))*10m}

Ibias 0 yi DC 5m

RL yi 0 1000

* Il carico è costituito dal parallelo della resistenza RL e dell’impedenza di

* ingresso del filtro posto a valle (il filtro è dimensionato per avere Zin=10

* alla pulsazione di risonanza)

Vcnn1 yi y DC 0

* Filtro passabanda: f0=100kHz, Q=5, attenuazione=100, Zin=1000 alla freq. di

8

* risonanza

r1 y 1 990

l1 1 2 7.9578m

c1 2 xi 318.31p

r2 xi 0 10

vcnn2 xi x DC 0

* Rivelatore di picco. L’uscita è bufferata.

rp1 y 3 1

dp1 3 z DIODE

cp1 z 0 100p

rp2 z 0 1meg

xbuff1 z o1 o1 opamp params: vumn=0

* L’uscita del rivelatore di picco viene filtrata con un filtro passa

* basso con frequenza di taglio molto bassa rispetto a quella dell’

* oscillatore (ft=1kHz) in questo modo si ottiene la dinamica "lenta"

* dell’agc

rp3 o1 zz 1meg

cp2 zz 0 159p

* La tensione di uscita del filtro controlla il blocco amplificatore

.probe

.tran 0.5u 1m 0 0.1u

.end

9