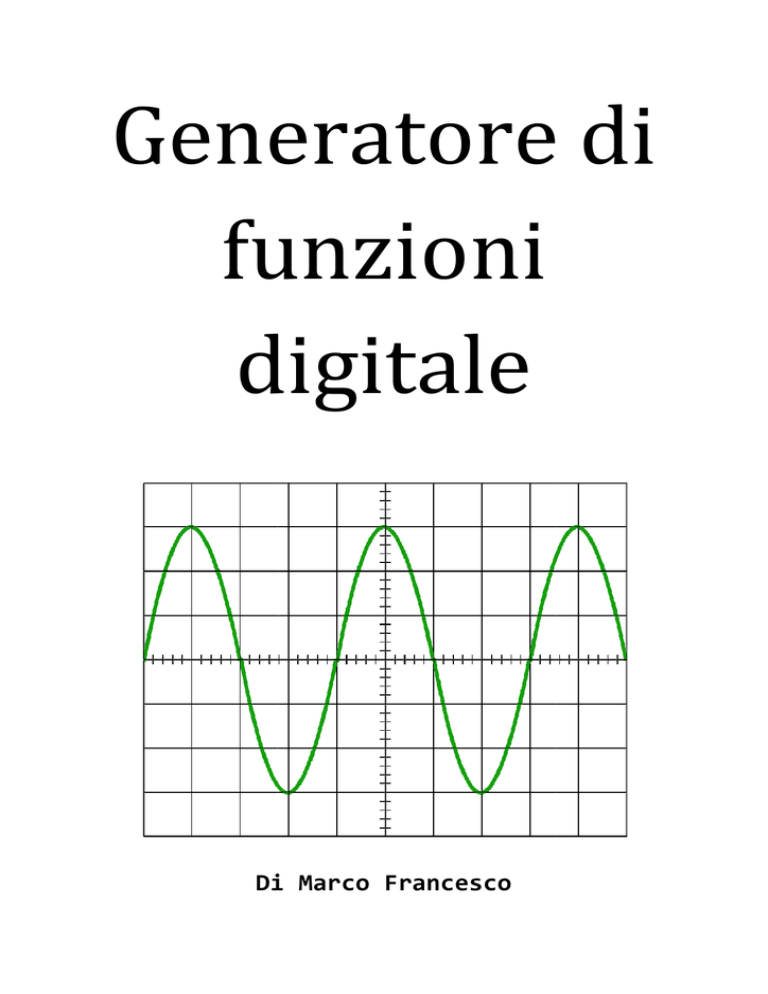

Generatore di

funzioni

digitale

Di Marco Francesco

Istituto Tecnico Industriale Statale

“Alessandro Volta”

Palermo

Progetto di un generatore di

funzioni digitale programmabile

Anno scolastico 2008/2009

Classe 5B

Di Marco Francesco

Indice:

1. Introduzione

2. Specifiche di progetto

3. Analisi progettuale

4. Generatore di clock

5. Contatore

6. Eprom

7. DAC

8. Condizionamento segnale

9. Alimentatore

10. Realizzazione pratica

11. Schemi e fotografie

pag.2

pag.3

pag.3

pag.5

pag.9

pag.12

pag.16

pag.19

pag.21

pag.24

pag.26

1

Introduzione

Lo studio della risposta dei circuiti elettronici necessita dell’utilizzo di un

generatore di funzioni che possa sollecitare l’ingresso di un circuito con diverse

forme d’onda, con frequenze e ampiezze regolabili in un elevato range.

I primi generatori di funzioni, di tipo analogico, basavano il loro funzionamento

su diversi oscillatori sinusoidali che, grazie a complessi circuiti di

sincronizzazione e controllo di frequenza e ampiezza, riproducevano forme

d’onda più o meno complesse (segnale rettangolare, a dente di sega,

triangolare, etc).

Tali circuiti andavano incontro a numerose problematiche, soprattutto per

quanto riguarda la stabilità dei parametri impostati (frequenza, ampiezza, duty

cycle) in funzione del tempo, della temperatura o di altre variabili che possono

influire la risposta di un qualsiasi componente elettronico.

Con l’avvento delle prime tecnologie digitali, i generatori di funzioni divennero

ben presto molto più precisi e personalizzabili. L’utilizzo di memorie digitali

come per la memorizzazione del valore istantaneo da mandare in uscita, portò

numerosi vantaggi: un numero più alto di segnali generabili, possibilità di

creare forme d’onda molto complesse, maggiore immunità ai disturbi, etc.

2

Specifiche del progetto

Si è scelto di voler progettare un semplice generatore di funzioni che faccia uso

di logiche di tipo digitale per la generazione delle forme d’onda. Il dispositivo

deve avere le seguenti caratteristiche:

• Generazione di 16 segnali

• Ampiezza di uscita regolabile tra ± 1 ÷ 10v; con offset di ± 10v

• Frequenza del segnale 0.1 ÷ 1000 Hz

Analisi progettuale

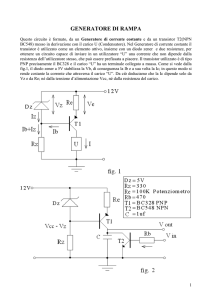

Il dispositivo da progettare genera le forme d’onda analogiche in base a una

tabella di valori digitali. Un generatore di clock pilota un contatore binario che

permette lo scorrimento di locazioni di memoria dove è memorizzato il valore

esadecimale istantaneo di diversi campioni del segnali da riprodurre, tali dati

vengono quindi trasferiti sequenzialmente a un convertitore D/A, che provvede

a generare un segnale analogico proporzionale al valore binario ricevuto. Il

segnale analogico generato viene quindi condizionato tramite un amplificatore

operazionale, per adattare il suo livello in valori rispettanti le specifiche di

progetto. Un secondo op-amp aggiunge un offset al segnale risultante. In fig.1 è

mostrato

lo

schema

a

blocchi

del

circuito

da

realizzare.

Fig. 1: Schema a blocchi dell’intero sistema

3

Come possiamo notare dalla fig.1, l’accuratezza dell’intero dispositivo dipende

principalmente dalla quantità di locazioni di memoria disponibili e dal numero

di bit usati per ogni campione. Dato che le specifiche non impongono vincoli

sull’accuratezza del segnale ricostruito in uscita, la risoluzione del DAC può

essere anche molto modesta per rispettare dei criteri di economicità; in

commercio si trovano a prezzo irrisorio memorie e DAC con capaci di lavorare

con 8 bit, più che sufficienti per il semplice uso a cui è destinato il generatore di

funzioni in una realizzazione didattica.

Viene quindi scelto un convertitore con 8 bit di ingresso, e una memoria

organizzata in 4K x 8bit, ovvero 4096 parole da 8 bit. In tal modo a ciascuna

delle 16 forme d’onda saranno assegnate 256 parole che convertite tramite il

DAC costituiscono 256 campioni per periodo. Per ottenere un corretto

indirizzamento devono essere collegati alle 8 linee meno significative di

ingresso in memoria i segnali provenienti da un contatore modulo 256. Le

restanti 4 linee verranno collegate a un selettore binario a 4bit, ovvero a 16

posizioni, tale selettore servirà per scegliere quale forma d’onda mandare in

uscita. La frequenza del segnale all’uscita del dispositivo dipenderà quindi

direttamente dalla frequenza del segnale di clock generato da un

multivibratore astabile; dato che per ogni periodo vengono letti 256 campioni

di segnale, la frequenza del segnale di clock dovrà essere 256 volte maggiore

rispetto alla frequenza del segnale che desideriamo in uscita.

Allo schema di fig.1 si dovrà quindi aggiungere un alimentatore stabilizzato che

fornisca i rail di alimentazione a tutte le parti del circuito.

Per comprendere meglio il funzionamento delle varie parti che compongono il

generatore è stata fatta un approfondita analisi di ognuno dei blocchi che

compone il sistema mettendo in evidenza le scelte progettuali e le soluzioni

circuitali.

4

Generatore di clock

Il generatore di clock è un dispositivo che genera un segnale di tipo periodico

che viene utilizzato per scandire ad intervalli regolari la successione delle

operazioni in larga parte dei circuiti di tipo digitale. Nel caso del progetto in

esame viene usato come generatore della base dei tempi per il funzionamento

dell’intero generatore di funzioni. Tale segnale consiste in un onda quadra con

duty cycle del 50%, e periodo variabile in un ampio range di frequenze. Viene

generato tramite un multivibratore astabile, un dispositivo che presenta un

funzionamento a scatto,

che spontaneamente passa per due condizioni

simmetriche di funzionamento con una precisa tempistica.

La soluzione circuitale scelta è basata sul comparatore LM311, di fig. 2, che

presenta due caratteristiche che lo rendono ideale per il nostro circuito:

• Bassa impedenza di uscita, realizzata con la soluzione circuitale

dell’open-drain, che permette un diretto interfacciamento a logiche di

tipo TTL o CMOS

• Condensatore di tempistica connesso tra un punto e la massa, per poter

più facilmente utilizzare capacità multiple commutate e quindi cambiare

facilmente il range di frequenze generate

Per il progetto in questione, è necessario di un generatore di clock che

consenta di variare la frequenza in un ampio range di valori, da 25.6 Hz a

256KHz. Il periodo di oscillazione potrà facilmente essere modificato mediante

l’inserimento di quattro valori di capacità e di un potenziometro resistivo. Un

selettore rotativo a quattro posizioni permetterà di selezionare la decade di

frequenza desiderata, mentre il potenziometro regolerà i valori entro la decade

scelta.

5

Fig. 2:: Schema elettrico del generatore di clock

Proseguiamo ora con un attenta analisi del circuito proposto. La rete di

reazione positiva fa dipendere la tensione di ingresso non invertente V+ dalla

tensione di uscita V0. L’LM311 è un comparatore di tensione, la sua uscita varia

in funzione degli ingressi secondo la seguente legge:

La V0 al livello basso è circa 0, poiché rappresenta la tensione Vce di saturazione

del transistor che pilota l’uscita del comparatore.

comparatore. Al livello alto, V0 dipende

dalla caduta di tensione ai capi di R3. Questa d.d.p., che risulta indesiderata, è

causata dalla corrente che scorre su R6, e dalla corrente che carica il

condensatore. Per minimizzare gli effetti dovuti a questa caduta di tensione,

t

ed

ottenere un fronte di salita ripido e compatibile con il blocco digitale successivo

(contatore modulo 256), occorre che la corrente di carica del condensatore sia

piccola, e che la tensione sulla R3 si riduca velocemente,

locemente, in modo tale che V0 al

livello alto sia quasi 5v. Si assumono i seguenti valori:

6

R3 = 330Ω; R4 = R5 = 22KΩ; R6 = 33KΩ. Con questi valori la V0 arriva a 4.9v,

ovvero molto prossima a 5v.

R1 ed R2 vanno dimensionati in base alla frequenza desiderata per il segnale di

uscita. Per mantenere piccola la corrente che scorre sul condensatore, R1 non

deve avere valore troppo basso. Le costanti di carica e di scarica sono:

;

Le soglie imposte tramite R4, R5 ed R6, fanno caricare ciclicamente la capacità

tra 1.8v e 3.1v. Dalla relazione:

Otteniamo che 0.5 e che 0.5 ; il periodo sarà quindi uguale a:

0.5 2 2

A seconda del valore assunto dal potenziometro R2, il periodo avrà come valori

limite:

0.5 2 2

;

0.5 2 Che rappresentano i valori estremi di ogni decade di frequenza. Pertanto si

deduce che:

10 "

10 5

Se Tmin = 3.7µs (frequenza massima, pari a 270KHz), se poniamo C = 1nF, si ha

che

2R1 + R3 = 7.4KΩ, quindi R1=3.5KΩ. Per semplicità si sceglie la coppia di

valori commerciali R1 = 3.3KΩ, R2 = 47KΩ.

7

Fig. 3: Il processo di carica e scarica della capacità

Vc

3.1v

1.8v

5v

Vo

8

Contatore

Il circuito digitale che segue il generatore di clock è un contatore binario a 8 bit

modulo 256 ottenuto mediante il collegamento in cascata di due contatori a 4

bit modulo 16,, montato come in fig.4. Le 8 linee d’uscita del contatore

piloteranno

oteranno le linee indirizzi A0 : A7 della EPROM. Il contatore è una rete

sequenziale in grado incrementare il valore binario presente in uscita ogni qual

volta incontra un impulso di clock. In generale, qualunque sia il dispositivo

utilizzato per il conteggio, deve esistere un sufficiente intervallo di tempo tra

due impulsi successivi perché il contatore riesca a registrarli correttamente;

cor

questo tempo minimo si chiama risoluzione del sistema e determina la

massima frequenza di lavoro. Il modulo di un contatore è il numero di

configurazioni differenti che egli consente di ottenere; ad esempio, un

contatore binario a 3 bit consente

consent di ottenere 23 configurazioni diverse, per cui

si dice che è modulo 8. In generale M = 2n, in cui n è il numero di bit.

Un contatore si avvale di diverse unità di memoria semplici ad un bit, chiamate

flip-flop,

flop, collegate l’una in cascata all’altra.

Fig. 4:: Schema elettrico di un contatore modulo 256

9

I contatori possono distinguersi in sincroni e asincroni, ciò in relazione alla

modalità di acquisizione ed elaborazione del dato.

Nei

contatori

asincroni

l’impulso

di

conteggio

non

è

inviato

contemporaneamente a tutti i flip-flop e quindi questi non possono commutare

simultaneamente. Considerando la disposizione in cascata dei flip-flop, segue

che l’uscita di ciascuno genera l’impulso di comando del flip-flop successivo. Si

parla, per questo motivo di contatori asincroni di tipo serie. Questo modo di

funzionamento produce la configurazione d’uscita con un tempo di ritardo

dipendente dal numero di flip-flop in cascata che hanno commutato. Tale

ritardo limita pesantemente il valore massimo della frequenza di conteggio; di

contro questo contatore presenta una notevole semplicità circuitale.

Nei contatori sincroni invece l’impulso di conteggio è inviato in modo

contemporaneo a tutti i flip-flop permettendone la commutazione simultanea;

i vari flip-flop hanno quindi la stessa priorità, e si parla per questo di contatori

di tipo parallelo. Il ritardo di commutazione di questo contatore è dovuto

quindi al tempo di commutazione di un singolo flip-flop, quindi la massima

frequenza di conteggio è maggiore di quella ammessa per i contatori asincroni.

Essendo il nostro blocco di conteggio costituito da due contatori modulo 16

perfettamente identici sarà sufficiente analizzare il funzionamento di uno, in

quanto rispecchierà il principio di funzionamento di conteggio del blocco.

Fig. 5: Schema interno di un 74LS393

10

In fig.5 possiamo osservare lo schema funzionale di un 74LS393, che contiene

al suo interno quattro flip-flop di tipo JK.Il segnale di clock proveniente dal

blocco precedente viene applicato all’incresso CP del primo flip-flop. Ad ogni

impulso di clock, in corrispondenza di uno dei due fronti del segnale, il primo

flip-flop varia la sua uscita invertendone lo stato logico. Abbiamo quindi

ottenuto un segnale in uscita di frequenza dimezzata rispetto al segnale di

comando. Collegando l’uscita di questo flip-flop all’ingresso del seguente,

otteniamo il risultato desiderato. In fig.6 possiamo vedere lo schema dei vari

segnali generati in funzione del tempo.

Fig. 6: Diagramma tempistiche delle uscite di un 74LS393

11

Eprom

La EPROM, acronimo di Erasable Programmable Read Only Memory, è una

memoria di sola lettura cancellabile tramite un esposizione ai raggi ultravioletti.

Si tratta di un evoluzione della PROM, che una volta programmata non poteva

più essere cancellata; la EPROM invece può essere totalmente cancellata (per

un numero limitato di volte) e riprogrammata a piacimento. Sono quindi

utilizzabili anche nel caso si preveda una modifica del loro contenuto.

Le EPROM sono realizzate in tecnologia MOS, il principio di funzionamento

delle EPROM infatti si basa su un particolare transistor detto FAMOS (Flooting

Gate Avalance Injection MOS) di cui se ne mostra la costruzione fisica in fig.7

Fig. 7: Struttura interna di un FAMOS e relativo simbolo elettrico

Lo scopo del progetto è quello di costruire un generatore di funzioni che possa

fornire forme d’onda complesse utilizzando tecniche digitali secondo il

principio di funzionamento dei generatori di funzioni arbitrarie (AFG). Questo

tipo di generatori implica l’utilizzo di una memoria ad alta velocità all’interno

della quale deve essere preventivamente caricata una sequenza di valori

numerici che definisce la forma, il periodo ed il contenuto armonico delle

funzioni desiderate. Ogni cella di memoria conterrà un valore numerico

(espresso in bit) che insieme ai valori contenuti nelle altre celle di una ben

12

definita area di memoria dovrà riprodurre la forma del segnale in questione. I

segnali analogici saranno allora costituiti da campioni, ottenibili tramite una

conversione digitale-analogica, la cui ampiezza sarà proporzionale al valore

numerico contenuto nelle rispettive celle.

L’accuratezza con la quale sarà possibile ricostruire il segnale dipenderà dal

numero di campioni che lo definiscono, quindi dal numero di celle di memoria e

in definitiva dalla capacità della memoria stessa. Per quanto i segnali in uscita al

generatore non presentino andamento perfettamente continuo, gli AFG

permettono di ottenere qualsiasi segnale desiderato purché esprimibile

attraverso una formula matematica. Per questo motivo, e per la stabilità del

segnale ottenuto, in molte applicazioni i generatori a tecnica digitale

sostituiscono i classici generatori a tecnica analogica.

Scelta della memoria

La realizzazione del generatore di funzioni programmabile necessita di una

memoria che sia in grado di memorizzare parole corrispondenti a campioni dei

segnali da generare per renderli successivamente disponibili in sequenza,

indirizzando in modo incrementale le successive celle di memoria. Considerato

che un generatore di forme d’onda deve essere una apparecchiatura

trasportabile e che sarebbe, comunque, impensabile tenerlo continuamente

alimentato, la scelta della memoria ricade su di un tipo non volatile. Scartata la

possibilità di scegliere memorie RAM aventi buoni tempi di accesso, bisogna

trovare una memoria di tipo ROM o SAM altrettanto veloce come le già citate

memorie volatili. Tra le specifiche del progetto, infatti, è richiesta una

frequenza massima selezionabile di 1KHz a cui corrisponde un periodo di 1ms;

considerato ciò bisogna scegliere una memoria che abbia tempi d’accesso

molto minori del periodo del segnale da generare. A questo punto si possono

escludere dalla nostra scelta anche le memorie SAM, i quali tempi i accesso,

13

oltre ad essere dipendenti dalla posizione del dato in memoria, sono compresi

tra il microsecondo ed il centinaio di microsecondi. Tra le memorie di tipo ROM

si è scelto di utilizzare una EPROM, infatti, si sono scartate le PROM poiché si è

considerata la necessità di cambiare col tempo le forme d’onda da generare

adeguandosi alle necessità del momento. Così si è scelta una EPROM 2732A a

32Kbit di capacità; le specifiche non richiedevano d'altronde particolare

precisione nei segnali di uscita, migliorabile, da questo punto di vista, da una

EPROM a capacità più elevata che potesse immagazzinare al proprio interno un

numero di campioni maggiori in un periodo. La soluzione scelta è risultata

comunque la più economica e sicuramente la più pratica.

L’EPROM 2732A, è una memoria con capacità di 32Kbit. Tali bit sono organizzati

in 4K (4096) parole ciascuna di lunghezza 8 bit. Sebbene sia realizzata in

tecnologia NMOS, tutti i piedini supportano lo standard TTL.

Fig. 8: Schema a blocchi interno della EPROM 2732A

La 2732A si presenta in un

contenitore a 24 pin e lavora

correttamente in un range di

temperatura compreso tra 0 e

70°C. In fig.8 si mostra lo schema

funzionale dell’integrato nel quale

si osserva la presenza di 12 linee

di indirizzo A0……A11 per la selezione dei 4096 byte, 8 linee dati di uscita

Q1……Q8 e due linee di controllo: G/Vpp per abilitare le linee di uscita e E per

l’abilitazione dell’integrato.

14

Organizzazione della memoria

Si è scelto di sfruttare la EPROM 2732° utilizzando 16 locazioni da 256 byte

ciascuna a cui corrispondono 16 diversi segnali.

se

Nella fig.9 viene mostrato come

si è suddivisa la memoria per poter accogliere i 16 segnali:

Fig. 9: Mappa della memoria

15

Convertitore digitale-analogico

Il DAC (Digital Analog Converter) è un circuito integrato capace di convertire un

segnale di tipo digitale in un altro di tipo analogico, proporzionale ad esso. Lo

schema a blocchi di un DAC è mostrato in fig.10. Un importante distinzione da

fare a priori è quindi quella tra segnale digitale e segnale analogico.

Fig. 10: Schema funzionale di un DAC

E considerato segnale digitale quello la cui forma d’onda presenta, almeno

idealmente, transizioni nette tra valori distinti (bit), mentre i segnali che

possono assumere qualsiasi valore sono detti analogici. Per quanto riguarda i

segnali digitali, al livello di tensione basso viene attribuito valore logico 0,

mentre a quello alto si è dato valore logico 1. Le transizioni non sono

comunque continue ma si alterano secondo l’informazione che contengono,

costituita da un determinato numero di bit a durata costante. L’insieme di un

determinato numero di bit viene detto “parola”, ed ha un contenuto

informatico che il DAC dovrà convertire in analogico. È ovvio che con n bit si

possono rappresentare 2n informazioni. Fatta distinzione tra i due tipi di

segnale, è importante comprendere perché è preferibile, a volte, lavorare con

16

segnali digitali rispetto ai segnali analogici. L’elaborazione puramente analogica

soffre di notevoli limitazioni riguardanti il rumore, la variazione dei parametri

circuitali nel tempo, l’influenza delle condizioni ambientali. Per ovviare a tali

problemi, si utilizzano quindi segnali di tipo digitale, i quali sono leggibili anche

se la loro forma d’onda risulta distorta; con ciò non è detto che comunque i

segnali digitali non presentano problemi. Un sistema digitale non è in grado di

elaborare il segnale in maniera continua dato che il loro funzionamento

dipende da un segnale di clock e quindi ogni operazione può avvenire soltanto

in istanti di tempo ben definiti dal segnale di clock.

Come già detto, un segnale analogico può assumere infiniti valori, mentre la

sua rappresentazione digitale può assumere soltanto un numero limitato di

valori, detti discreti. Il processo di quantizzazione si occupa di associare ad un

determinato range di valori analogici una corrispettiva approssimazione

digitale. Una parola composta da un numero più elevato di bit permette

un’approssimazione minore ed una conseguente riduzione dell’errore di

quantizzazione. Un numero di bit maggiore porta quindi all’aumentare della

risoluzione di conversione di un DAC.

L’introduzione del DAC nel circuito del generatore di funzioni, è utile per poter

convertire i segnali digitali uscenti dalla EPROM, espressi in codice binario, in

un segnale analogico che segue l’andamento del segnale desiderato. Utilizzato

per tale proposito è il DAC 0800 il quale ha una scarsa risoluzione, infatti

dispone di solo 8 ingressi digitali, che permettono di avere in uscita solo 28

valori, ovvero 256 livelli di tensione, ognuno dei quali rappresenterà un

possibile valore istantaneo della forma d’onda in uscita. Se avessimo voluto una

migliore risoluzione avremmo dovuto utilizzare un DAC con un maggior numero

di ingressi, una EPROM che lavora ad un numero di bit maggiore, un contatore

a modulo più elevato.

17

In fig.11 è mostrato lo schema a blocchi del DAC 0800 dove sono ben visibili la

rete a scala R2R e le uscite di corrente.

Fig. 11: Schema a blocchi del DAC 0800

Fig. 12: Schema elettrico di collegamento del blocco DAC.

Come

si

può

vedere

dallo

schema elettrico di fig.12, VRdeve essere posta a massa in

modo

che

l’uscita

di

tale

comparatore dia una tensione di

saturazione massima utile per

polarizzare direttamente le basi

dei transistor utilizzati come

deviatori,

che

vengono

comandati dallo stato dei bit in

ingresso.

18

Condizionamento segnale di uscita

La scelta dell’utilizzo di due amplificatori operazionali per il condizionamento

del segnale di uscita, non è stata particolarmente difficile, in quanto uno dei

vantaggi che si ottiene impiegando un amplificatore operazionale è quello di

avere a disposizione dentro un piccolo involucro una catena di transistor

amplificatori già elettricamente collegati fra loro con resistenze di

polarizzazione e condensatori di disaccoppiamento, che, se venisse realizzato

con componenti discreti richiederebbe spazi notevoli. Inoltre, un amplificatore

operazionale può essere utilizzato per amplificare segnali sia alternati che

continui; altra caratteristica fondamentale risiede nell’impedenza di uscita

bassissima che permette un accoppiamento perfetto con qualsiasi tipo di

circuito a valle senza ottenere attenuazioni.

Nel nostro progetto utilizziamo un TL082, un integrato che in un semplice case

DIP-8 integra al suo interno due amplificatori operazionali, che possiedono uno

slew-rate elevato che permette di garantire delle rapide commutazioni quando

il segnale si uscita raggiunge velocemente un valore limite.

Il principale vantaggio che presenta un amplificatore operazionale è quello di

poterlo reazionare molto facilmente senza

pericoli che si creino delle

autoscillazioni e di poterlo adattare ad un determinato guadagno modificando

semplicemente una resistenza, indipendentemente dalla tensione di

alimentazione.

La rete di reazione che è necessaria all’amplificatore è molto semplice, in

quanto si tratta, nella configurazione più semplice, di sole due resistenze.

Dalla retroazione dipendono:

•

il guadagno di tensione che, una volta fissato non subisce più alcuna

variazione anche alimentando l’amplificatore con tensioni diverse, tale

guadagno è anche insensibile a variazioni di temperatura

19

• l’impedenza di ingresso che è possibile modificare realizzando così uno

stadio ad alta

lta impedenza a seconda delle esigenze

• la rispostaa in frequenza dell’amplificatore, in quanto è possibile realizzare

con estrema facilità filtri passa alto, passa basso, passa banda,

integratori,

derivatori,

sommatori,

amplificatori

logaritmici,

semplicemente

nte con l’aggiunta di pochi componenti esterni

Il TL082 è un dispositivo composto da due amplificatori operazionali con input

i

differenziale a JFET,, ad alta velocità ed a basso costo, con una regolazione

interna della tensione di offset di ingresso.

ingresso La funzione

ione del primo amplificatore

è quella di sottrarre alla corrente entrate nel DAC (poiché negata), una corrente

offset di 1mA, in modo che nell’anello di reazione passi una corrente

alternativa tra +1mA e -1mA.

1mA. Esso ha anche il compito di convertire tale

corrente

rrente in una tensione di ampiezza regolabile attraverso il potenziometro R15.

Fig. 13:: Schema elettrico del circuito di condizionamento

20

Il secondo amplificatore svolge la funzione di sommatore invertente in quanto

inverte la tensione uscente dal primo amplificatore ed in più somma ad essa

una tensione di offset compresa tra ± 10v. La tensione di offset viene regolata

attraverso una rete composta dalle resistenze R17 e R19, dal potenziometro R18 e

dal deviatore Sw3, che permette di inserire o meno la tensione di offset. Questa

tensione viene ricavata tramite il partitore composto da R17, R18 e R19.

21

Alimentatore

Ogni circuito elettrico necessita di una adeguata alimentazione. I vari circuiti

proposti nelle pagine precedenti richiedono diversi rail di alimentazione:

Integrato Alimentazione

LM 311

5v

74LS393

5v

2732A

5v

DAC 0800

± 12v

TL 082

± 12v

Si rende quindi necessario progettare un alimentatore stabilizzato capace di

fornire una tensione duale di 12v e una tensione positiva di 5v.

L’energia viene prelevata dalla rete elettrica nazionale, quindi avremo una

tensione alternata sinusoidale, di valore efficace 230v, e frequenza 50Hz.

Come possiamo vedere in fig.14 viene utilizzato un trasformatore con un

secondario provvisto di presa centrale, capace di fornire due tensioni alternate

in fase, ognuna di ampiezza 15v efficaci.

Fig. 14: Schema elettrico alimentatore stabilizzato

I quattro diodi posti all’uscita del trasformatore hanno il compito di raddrizzare

la tensione sinusoidale trasformandola in un segnale unipolare semisinusoidale. Tale segnale, inadatto a pilotare direttamente i dispositivi di

stabilizzazione, viene trasformato in un due rail tensione continua dalle

capacità elettrolitiche da 470µF. I tre integrati utilizzati sono stabilizzatori

22

lineari di tensione, che provvedono a creare una tensione continua con

bassissimo ripple, che non cambia il suo valore in base al carico applicato. Il

7812 provvede a fornire in uscita una tensione positiva di 12v, il rail negativo

complementare viene fornito invece dal 7912. Il 7805 fornisce invece la

tensione di +5v, utile al funzionamento del generatore di clock, del contatore,

della EPROM e del led indicante l’accensione del dispositivo. Le capacità

ceramiche da 100nF presenti tra l’ingresso di ogni stabilizzatore e la massa

servono a prevenire eventuali oscillazioni interne degli stabilizzatori.

Il led è collegato alla tensione di 5v tramite una resistenza limitatrice da 330Ω,

posta in serie allo stesso, con lo scopo di far scorrere una corrente di circa

10mA nel diodo, più che sufficienti per una chiara indicazione dello stato.

23

Realizzazione pratica

Vista la complessità del circuito, la realizzazione dell’intero progetto in un'unica

scheda sarebbe stata di difficile realizzazione pratica in quanto si sarebbero

dovute usare basette presensibilizzate a doppia faccia, con

con tutti i problemi che

ne conseguono.

Si è scelto quindi di realizzare il circuito come in fig.15, in maniera modulare,

realizzando 5 schede separate. Osservando gli schemi elettrici si è notato che è

possibile realizzare:

1. una scheda per il generatore di clock

2. una scheda che racchiude il contatore modulo 256, la EPROM e il DAC

3. una scheda per il circuito di condizionamento

4. una scheda per l’alimentatore

5. una scheda di bus

Fig. 15:: Progetto realizzazione pratica generatore di funzioni

24

Le schede 1 – 2 – 3 – 4, verranno montate in verticale sulla scheda 5, tramite

dei connettori a 12 pin. La scheda bus è semplicemente realizzata tramite 4

connettori collegati l’un l’altro in parallelo. In fig.16 è mostrata la funzione di

ogni pin. Per ragioni estetiche e funzionali si è scelto di utilizzare una

dimensione standard per le quattro schede, come mostrato in fig.17. Nei punti

A – B – C verranno posti i comandi presenti in ogni scheda, secondo la tabella in

fig.18, al fine di avere le manopole allineate nel pannello frontale. La presa BNC

viene collocata nella scheda 4 (alimentatore)

Fig. 16: Piedinatura connettore Fig. 17: Dimensione scheda 1 – 2 – 3 – 4

Fig. 18: Posizione controlli

Controllo

Scheda

1

2

3

4

A

B

C

Selezione

frequenza

Selezione

funzione

Regolazione

ampiezza

−

Regolazione

frequenza

−

−

Regolazione

offset

Offset

ON/OFF

Led

−

BNC

25

Schemi elettrici e fotografie

Nelle pagine seguenti verranno mostrati gli schemi elettrici finali di ciascuna

delle cinque schede che compongono il circuito

1.

Scheda “Generatore di clock”

26

2.

Scheda “Contatore + memoria + DAC”

27

3.

Scheda “Condizionamento”

28

4.

Scheda “Alimentatore”

29

5.

Scheda “Bus”

30