Circuiti statici, dinamici e circuiti sequenziali.

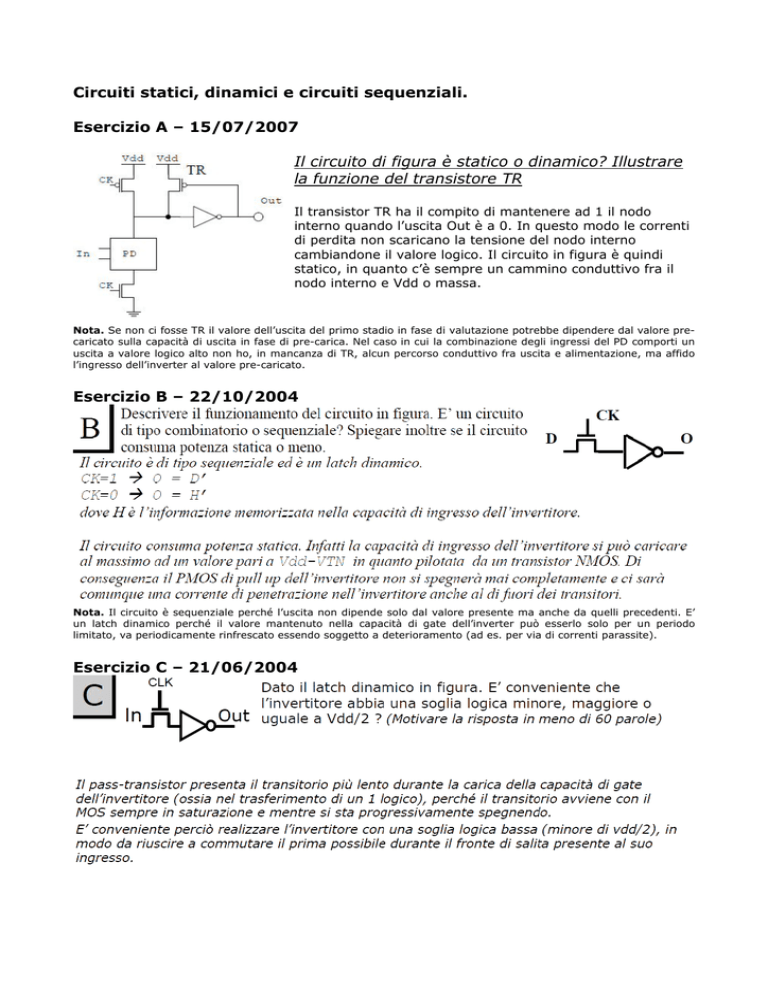

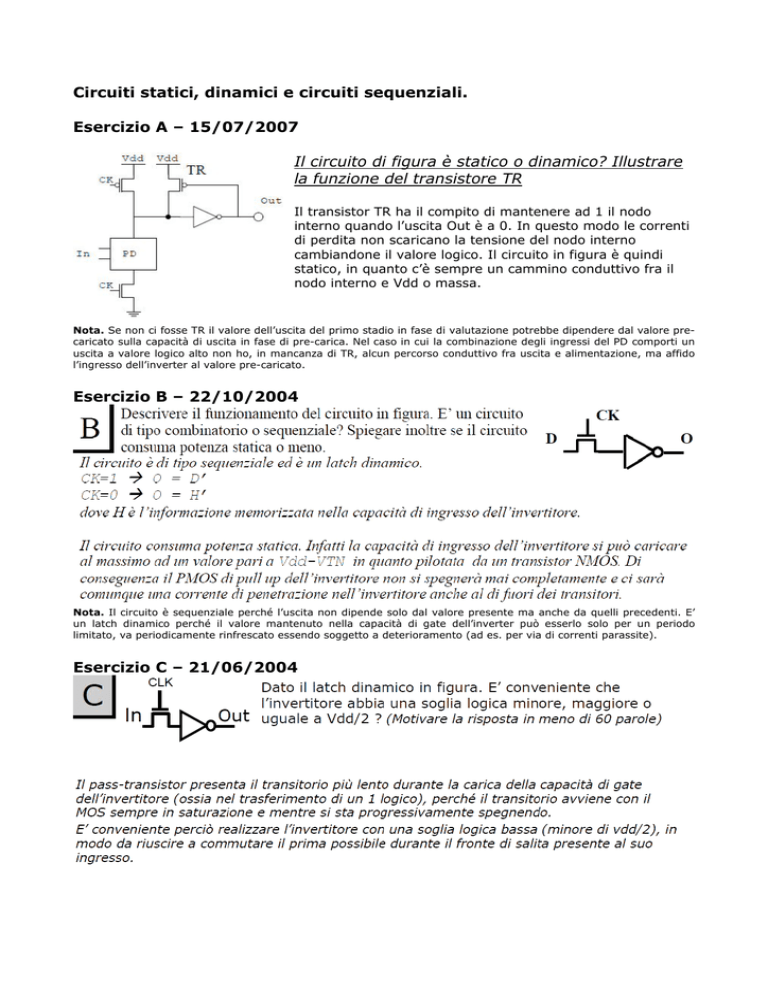

Esercizio A – 15/07/2007

Il circuito di figura è statico o dinamico? Illustrare

la funzione del transistore TR

Il transistor TR ha il compito di mantenere ad 1 il nodo

interno quando l’uscita Out è a 0. In questo modo le correnti

di perdita non scaricano la tensione del nodo interno

cambiandone il valore logico. Il circuito in figura è quindi

statico, in quanto c’è sempre un cammino conduttivo fra il

nodo interno e Vdd o massa.

Nota. Se non ci fosse TR il valore dell’uscita del primo stadio in fase di valutazione potrebbe dipendere dal valore precaricato sulla capacità di uscita in fase di pre-carica. Nel caso in cui la combinazione degli ingressi del PD comporti un

uscita a valore logico alto non ho, in mancanza di TR, alcun percorso conduttivo fra uscita e alimentazione, ma affido

l’ingresso dell’inverter al valore pre-caricato.

Esercizio B – 22/10/2004

Nota. Il circuito è sequenziale perché l’uscita non dipende solo dal valore presente ma anche da quelli precedenti. E’

un latch dinamico perché il valore mantenuto nella capacità di gate dell’inverter può esserlo solo per un periodo

limitato, va periodicamente rinfrescato essendo soggetto a deterioramento (ad es. per via di correnti parassite).

Esercizio C – 21/06/2004

Esercizio L – 21/10/2005

1) Supponendo che il valore iniziale di O sia “0”,

tracciare la forma d’onda di O,X,Y

2) Se Sninv = 2, Spinv = 2 calcolare il tempo

necessario perché un fronte 0->1 e 1->0 sul

nodo X si propaghi sul nodo Y (si trascurino le

capacità di D e S dei pass-transistor)

3) Il circuito di uscita è sequenziale, statico o

dinamico?

4) Tracciare le forme d’onda in O,X,Y se i due

pass-transistor vengono invertiti

Rispondiamo alla 1 e alla 4

I

X

Y

2

2)

O

Calcolo la capacità di carico del primo inverter che, viste le semplificazioni suggerite dal testo,

consiste nella sola capacità di ingresso del secondo invertitore:

fF

Cy = Cox ⋅ L2min ⋅ ( Sp + Sn) = 3,45

⋅ 0,35 2 μm 2 ⋅ 4 = 1,69 fF

μm 2

2 ⋅ 1,69 ⋅ 10 −15

⋅ 0,62 = 1,0478 ⋅ 10 −11 = 10,478 p sec

−6

100 ⋅ 10 ⋅ 2

2 ⋅ 1,69 ⋅ 10 −15

tr =

⋅ 0,62 = 20,956 p sec

50 ⋅ 10 −6 ⋅ 2

tf =

3) Il circuito è sequenziale e statico. E’ sequenziale poiché la sua uscita dipende non solo dallo

stato degli ingressi nell'istante considerato ma anche da quello che erano gli ingressi e le uscite

negli istanti precedenti quello considerato. In pratica il circuito sequenziale ricorda quello che è

avvenuto nel circuito negli istanti precedenti.

E’ statico poiché l’anello dei due invertitori è rigenerativo, cioè garantisce che quando i nodi X ed I

sono isolati da ingresso e uscita, il valore sulla capacità a tali nodi mantenga il valore corretto grazie

alla retroazione e non si deteriori. Dunque il valore immagazzinato non richiede almeno idealmente

di essere rinfrescato.

Partitore di carica

Esercizio B – Luglio 2008

Selezionare la tensione finale a cui si porta il nodo corrispondente

all’interruttore a seguito della chiusura dell’interruttore stesso

V1(0)=3V

CX=0.1fF

V2(0)=-1V

CY=10fF

V3=1V

Q = C X V1 (0 − ) + CY (V2 (0 − ) − V3 ) = −19,7 fC

Q = CxV (0 + ) + CY (V (0 + ) − V3 )

→ V (0 + ) =

Q + CY V3

= −0,96V

(C X + CY )

Esercizio B – Luglio 2007

Selezionare la tensione finale a cui si porta il nodo X a seguito della chiusura

dell’interruttore

Esercizio B 12/01/2005

Esercizio B del 9/7/2007

I valori a destra e sinistra V4Cz e V5Cy si elidono. Inoltre in seguito alla chiusura degli interruttori

ho potuto usare a destra dell’equazione V3(0+)=V2(0+)=Vx(0+). Resta perciò:

V3 (0 − )C Z + V X (0 + )C X + V2 (0 − )CY 4V ⋅ 2 fF + 1 ⋅ 3 fF + 4V ⋅ 1 fF 15V ⋅ fF

+

V X (0 ) =

=

=

= 2,5V

C Z + C X + CY

6 fF

6 fF

Esercizio d’esame

Si assuma CFG=50fF e la capacità di gate del transistore pari a CG=100fF.

1) Si calcoli il valore limite della tensione Vx in corrispondenza di un valore d’ingresso VI=0

necessario per garantire che il dispositivo resti sotto soglia per valori di tensione in ingresso VI

qualsiasi nell’intervallo [0;3,3]V.

2) Si calcoli il valore della tensione Vx quando VI=0 necessario per garantire l’accensione del

dispositivo per VI=1,0V.

3) Assumendo per il transistore W=0,5μm, L=0,35 μm, BL pre-caricata a VL(t0-)=3,3V, Vx(t0-)=0,

VI(t0-)=0, si calcoli la corrente IDS(t0+) a seguito di un fronte istantaneo di VI da 0 a 3,3V al tempo

t=0

4) Nelle condizioni del punto 3, si calcoli la durata al 90% del transitorio di scarica della linea BL,

se CL=1pF

Soluzione.

Il circuito in figura funziona come un transistore a floating gate il cui comportamento viene

modellato con un partitore capacitivo. VI è la tensione di controllo del gate con cui normalmente

accendo il transistore. Di solito se VI =Vdd=3,3V l’nMOS si accende. Nel floating gate inserisco

della carica negativa per inibire l’accensione. Quanta? Ecco cosa significa il primo quesito… quanta

carica metto ovvero a che tensione devo mettere Vx in condizioni di riposo, tale che quando poi

mando una tensione in ingresso non nulla VI il dispositivo comunque resti spento.

1) Per VI=0V Vxi? Sapendo che per VI Є[0;3,3]V il dispositivo voglio resti OFF, ovvero sul gate ci

deve essere una tensione inferiore alla soglia, ovvero ai capi di CG deve essere Vgs=Vxf-0<Vtn

(con i indico iniziale ovvero all’istante in cui VI=0V, con f indico finale ovvero quando VI varia

nell’intervallo [0;3,3]V).

Uso le formule per la distribuzione della carica.

(V Xi − VIi )C FG + V Xi CG = (V Xf − VIf )C FG + V Xf CG

Da cui, applicando la condizione iniziale VI=0V e raccogliendo

(C FG + CG )VXi = (CFG + CG )VXf − VIf C FG

Ora pongo la condizione Vxf<Vtn mettendomi nella situazione limite di accensione per trovare un

valore massimo di Vx che rispetti la condizione. Per cui pongo Vxf=Vtn=0,7V e mi metto anche nel

caso peggiore in cui la tensione in ingresso sia al valore massimo nel range di valori che può

acquisire, quindi VIf=3,3V da cui

VXi =

(C FG + CG )VXf − VIf C FG

(C FG + CG )

=

150 fF ⋅ 0,7V − 3,3V ⋅ 50 fF

= −0,4V

150 fF

Se voglio conoscere quanta carica mettere sul floating gate corrispondente a questo valore massimo

di tensione per non fare accendere il transistor la posso ora calcolare:

Q = (VXi − VIi )CFG + VXiCG = (CFG + CG )VXi = −0,4V ⋅ 150 fF =

= −60 fC

2) Desidero che ci sia accensione per VI =1,0V, ovvero che per tale Vi, che indicheremo come VIf,

valga la condizione VXf≥Vtn=0,7V. Come prima perciò uso l’espressione

(V Xi − VIi )C FG + V Xi CG = (V Xf − VIf )C FG + V Xf CG

Sostituisco VXf =0,7V, VIf =1,0V eVIi=0V e ottengo:

V Xi =

100 fF ⋅ 0,7V − 0,3V ⋅ 50 fF

= 0,37V

150 fF

3) Uso di nuovo l’uguaglianza della carica prima e dopo il fronte di salita. Svolgendo i calcoli:

VI (t0+ )C FG

3,3V ⋅ 50 fF

VX (t ) =

=

= 1,1V

(C FG + CG )

150 fF

+

0

Per tale valore vale che il mos è acceso e in saturazione infatti:

V X (t 0+ ) = 1,1 > VTN = 0,7

Vgs − Vtn > Vds ?

<

Vx − VTN = 0,3V < 3,3V

Da cui:

I DSsat =

β n' W

2 L

(Vgs − Vtn) 2 = 100

μA 1 0,5μm

(0,4) 2 V 2 = 11,42μA = 0,1mA

V 2 2 0,35μm

Esercizio L 07/2009

C

A

O

A

B

Con riferimento al circuito in figura

1) Si determini il valore logico dell’uscita O per tutti i valori logici degli ingressi (A,B,C). Si usi il

simbolo H per configurazioni in cui l’uscita risulta flottante (in caso ve ne siano).

2) Utilizzando valori di resistenze equivalenti RPU= 45KΩ (relativo a ciascun NMOS in pull up) e

RPD=25KΩ (per ciascun NMOS in pull down), e assumendo CO=100fF, si determini il ritardo di

caso peggiore.

3) Si calcolino le tensioni di uscita per tutti i valori degli ingressi, fatta eccezione per quelli in cui

l’uscita risulta flottante (si trascuri l’effetto Body)

4) Il circuito ha un comportamento sequenziale? Statico o dinamico?

Soluzione a 1 e 3

Quando A = 1 l’uscita O è connessa con massa. E poiché il pass-transistor nMos è bravo a portare

gli zeri, la tensione a regime è nulla. Quando A’=1 ovvero A=0 ci possono essere due situazioni. La

prima è C=1. In tal caso O è connessa a B e quindi O assume il valore di B. In particolare, se B=0 la

tensione su CO è nulla. Se B=1, dal momento che gli nMos non portano bene gli 1 logici la tensione

arriva solo a Vdd-Vtn. Infine sempre per A=0, ci può essere anche il caso C=0. In tal caso il nodo

di uscita è flottante e il valore della tensione ai suoi capi non è determinabile. In sintesi:

A

B

C

O

Tensioni in uscita

0

0

1

0

0V

0

1

1

1

VDD – VTN = 2,6V

0

0

H

(Varia nel tempo)

1

0

0V

Soluzione a 2

Il caso peggiore è il transitorio di salita attraverso 2 nMOS in serie A=0 B=1 C=1 - vedi (i). Infatti

in questo caso moltiplico per un fattore 2 la RPU (che è maggiore della RPD). Gli altri transitori

possibili sono la scarica attraverso il ramo sinistro (un nMOS) – vedi (ii) e quella attraverso il ramo

destro (2 nMOS) – vedi (iii). Entrambi risultano più lenti.

t90% = CO REQ ln 10

(i )t90% = CO 2 RPU ln 10 ≈ 20,7ns

(ii )t90% = CO RPD ln 10 ≈ 5,75ns

(iii )t90% = CO 2 RPD ln 10 ≈ 11,5ns

Soluzione a 4.

Il circuito è sequenziale, in quanto permette di convogliare e successivamente conservare carica sul

nodo O. In particolare si comporta come un latch, in cui: Il segnale A ha la funzione di “clear”. Se

alto, cortocircuita la capacità a massa. Se basso, la isola da massa e abilita il ramo destro del latch.

•

Il segnale B è l’ingresso.

•

Il segnale C agisce da clock. Se basso, il latch è opaco; se alto, il latch è trasparente.

Il circuito è dinamico perché l’informazione risiede sotto forma di carica in un nodo flottante ad alta

impedenza. Il nodo è soggetto a perdite e il contenuto informativo degrada nel tempo.

Nota bene.

Le porte logiche a pass-transistor non possono essere messe in cascata connettendo l’uscita di una

porta logica all’ingresso della successiva, qualora tale ingesso sia il terminale di gate di un transistor.

Nella situazione a, l’uscita del pass transistor M1 è l’ingresso del pass-transistore M2. L’escursione

di tale ingresso X è limitata fra 0 e Vdd-Vtn1. Questo ha conseguenza a catena su M2 che essendo un

nMOS anch’esso porta male gli 1 logici e quindi Y potrà variare al massimo fra 0 e la tensione del

nodo X meno la sua soglia ovvero al massimo Vdd-Vtn1-Vtn2 (o se Vtn1=Vtn2=Vtn fra 0 e Vdd-2Vtn).

Nella situazione B, nel caso peggiore, l’ingresso logico alto viene propagato su X con

deterioramento del segnale (X €[0, Vdd-Vtn1]). X però questa volta finisce sul drain di M2 ma questo

non provoca un deterioramento a catena. Infatti M2 è pilotato da C, che consideriamo abbia

un’escursione piena [0, Vdd]. M2 quindi si spegne quando Vgs= Vdd-Vtn2. Se Vtn1=Vtn2 o Vtn1>Vtn2

(quindi Vdd-Vtn1< Vdd-Vtn2) M2 riesce a copiare Vdd-Vtn1. Se Vtn1 < Vtn2 (quindi Vdd-Vtn1> Vdd-Vtn2)

Vy = Vdd-Vtn2.

Analoghi ragionamenti possono esser fatti per il transistore PMOS usato in catena di pass-transistor.