Logica Combinatoria

Lucidi del Corso di Circuiti Integrati

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

Logica combinatoria

Un blocco di logica puramente combinatoria è

un blocco con N variabili di ingresso e M

variabili di uscita che sono funzione (booleana)

degli ingressi presenti in un certo istante.

Ad ogni istante le uscite dipendono solo dagli

ingressi in quell’istante e NON dalla storia

passata del circuito

x1

x2

y1

y2

xN

12 Ottobre 2012

yM

CI - Logica Combinatoria

Massimo Barbaro

Stili di progetto

Logica statica: l’uscita è sempre connessa

all’alimentazione o alla massa (es. static CMOS,

pseudo-NMOS, pass transistor). Esiste cioè sempre un

percorso diretto a bassa impedenza fra una delle

alimentazioni ed il nodo di uscita.

Logica dinamica: il nodo di uscita non è sempre

connesso ad una delle alimentazioni e il dato viene

temporaneamente immagazzinato in forma di carica

su una capacità (es. np, domino)

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Logica combinatoria

CMOS statico

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

Logica statica CMOS

Dall’inverter CMOS è facile ottenere porte

logiche più complesse con gli stessi vantaggi del

singolo inverter:

VOH=VDD , VOL=0

Nessuna dissipazione di potenza statica

Ampi margini di rumore

Tempi di salita e discesa confrontabili

opportune regole di progetto)

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

(con

Esempi di gate CMOS

A

B

B

A

Z=?

B

Z=?

A

12 Ottobre 2012

A

CI - Logica Combinatoria

B

Massimo Barbaro

Logica statica CMOS

Come si capisce la funzione logica implementata da un circuito a

transistor?

■ Si considera ogni possibile combinazione di ingresso, ossia ogni riga

della tabella di verità.

■ Per ogni combinazione di sostituisce

■ ad ogni NMOS:

■ un circuito APERTO se l’ingresso è 0

■ un circuito CHIUSO se l’ingresso è 1

■ ad ogni PMOS:

■ un circuito CHIUSO se l’ingresso è 0

■ un circuito APERTO se l’ingresso è 1

■ Si verifica, dal circuito risultante, se l’uscita è connessa a massa (0)

oppure a VDD (1)

■ Si riporta il valore logico nella tabella della verità

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Porta NAND(1)

PMOS accesi, NMOS spenti

1

A

B

M3

M4

A

B

Z

0

0

1

0

1

1

1

0

1

1

1

0

3

Z

B

M2

A

M1

Z

2

12 Ottobre 2012

CI - Logica Combinatoria

Z è disconesso

da massa e

connesso a VDD

dunque l’uscita è

un 1 logico

Massimo Barbaro

Porta NAND (2)

M2 e M3 accesi, M1 e M4 spenti

1

A

B

M3

M4

A

B

Z

0

0

1

0

1

1

1

0

1

1

1

0

3

Z

B

M2

A

M1

Z

2

12 Ottobre 2012

CI - Logica Combinatoria

Z è disconesso

da massa e

connesso a VDD

dunque l’uscita è

un 1 logico

Massimo Barbaro

Porta NAND (3)

M2 e M3 accesi, M1 e M4 spenti

1

A

B

M3

M4

A

B

Z

0

0

1

0

1

1

1

0

1

1

1

0

3

Z

B

M2

A

M1

Z

2

12 Ottobre 2012

CI - Logica Combinatoria

Z è disconesso

da VDD e

connesso a

massa dunque

l’uscita è uno 0

logico

Massimo Barbaro

Porta NAND

La porta in figura è una

NAND perché l’uscita è

uguale a 0 solo se A e B

sono entrambi 1 (quando

i 2 NMOS del PDN sono

entrambi in conduzione). In

tale condizione il PUN è

sicuramente interdetto

Se anche uno solo fra A e

B è pari a 0 il percorso

verso massa si interdice e

si chiude uno dei due

percorsi verso VDD (PUN)

quindi l’uscita e 1

12 Ottobre 2012

A

CI - Logica Combinatoria

B

Z=(AB)’

A

B

Massimo Barbaro

Porta NOR

La porta in figura è una NOR

perché l’uscita è uguale a 1

solo se A e B sono

entrambi 0 (quando i 2

PMOS del PUN sono

entrambi in conduzione). In

tale condizione il PDN è

sicuramente interdetto

Se anche uno solo fra A e B

è pari a 1 il percorso verso

VDD si interdice e si chiude

uno dei due percorsi verso

massa (PDN) quindi l’uscita

e0

12 Ottobre 2012

CI - Logica Combinatoria

B

A

Z=(A+B)’

A

B

Massimo Barbaro

Logica statica CMOS

Una generica porta CMOS ha la struttura:

x1

x2

x3

PUN

F(x1,x2,x3)

x1

x2

x3

12 Ottobre 2012

PDN

CI - Logica Combinatoria

Massimo Barbaro

Caratteristiche logica CMOS

PUN (Pull-Up Network): è una rete di interruttori

PMOS che connettono l’uscita a VDD in

corrispondenza delle combinazioni di ingresso per

cui la funzione è F(…)=1

PDN (Pull-Down Network): è una rete di

interruttori NMOS che connettono l’uscita a 0 in

corrispondenza delle combinazioni di ingresso per

cui la funzione è F(…)=0

Le due reti sono complementari, ossia quando è

aperta una l’altra è chiusa e viceversa. Questo

evita che ci siano percorsi diretti fra alimentazione

e massa.

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Interruttori NMOS

Y

Y

A

A

B

B

X

X

Y=X SE A=1 E B=1 (A•B)

12 Ottobre 2012

Y=X SE A=1 O B=1 (A+B)

CI - Logica Combinatoria

Massimo Barbaro

Interruttori PMOS

Y

Y

A

A

B

B

X

X

Y=X se A=0 E B=0 (A’•B’)

12 Ottobre 2012

Y=X se A=0 O B=0 (A’+B’)

CI - Logica Combinatoria

Massimo Barbaro

Generica porta CMOS

Una generica porta CMOS può essere implementata

partendo dall’espressione algebrica o dalla tabella di

verità. La PDN deve essere tale da chiudere il percorso

a massa per le righe in cui F(…)=0 e la PUN tale da

chiudere il percorso a VDD per quelle in cui F(…)=1

Per la dualità delle due reti (teorema di DeMorgan) ogni

volta che i transistor sono in serie nella PDN sono in

parallelo nella PUN e viceversa

Si può sempre partire dall’implementazione della sola

PDN per poi ricavare la PUN oppure viceversa

Non tutte le funzioni sono direttamente implementabili, in

particolar modo le porte CMOS sono sempre invertenti

(per fare una AND è necessario implementare una

NAND con un inverter in cascata)

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Implementazione di una porta CMOS

PUN: F=G’(x1,x2,x3,+,•) = G(x1’,x2’,x3’ ,•,+)

x1

x2

x3

PUN

La PUN è funzione di soli segnali

negati perché è composta da switch

PMOS (si ottiene per DeMorgan

dalla PDN)

F(x1,x2,x3)

x1

x2

x3

PDN

Quando G (solo funzione di

AND e OR e dei segnali NON

negati) è vera la PDN

cortocircuita l’uscita a massa

PDN: G(x1,x2,x3,+,•) => F=G’

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Implementazione di una porta CMOS

Realizzando la PDN si è in grado di implementare (sono

NMOS) una qualsiasi funzione G di soli operatori AND e

OR

(es.

Quando G=1 l’uscita è connessa a massa quindi F=0

allora:

PDN: G(x1,x2,…,xN,+,•)

G=AB+CD+F(A+B) )

F(x1,x2,…,xN)=G’(x1,x2,…,xN,+,•)

(es. F=[AB+CD+F(A+B)]’)

Il PUN invece implementa direttamente la funzione

(connette l’uscita a 1) ma può contenere solo operatori

NOR e NAND (quelli implementabili con switch PMOS)

F(x1’,x2’,…,xN’ ,+,•)= F’(x1,x2,…,xN, •,+)=

Dualità del PDN e PUN

=G(x1,x2,…,xN, •,+)

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Esempio

Z=[A(B+C)+D]’

D

Funzione negata

di sole OR e AND

B

A

C

Z’=A(B+C)+D=G

A

D

Implementabile con un PDN

B

(le OR sono NMOS in parallelo,

le AND sono NMOS in serie)

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

C

Esempio

Z=(A’+B’C’)D’

D

Funzione di sole

OR e AND di

segnali negati

B

A

C

Implementabile con un PUN

(le OR di segnali negati sono

PMOS

in

parallelo,

le AND di segnali negati sono

PMOS in serie)

12 Ottobre 2012

CI - Logica Combinatoria

A

D

B

Massimo Barbaro

C

Procedura di sintesi (1)

■ Si considera la forma della funzione:

■ Se si tratta di un funzione NEGATA di sole variabili

NON negate ( Z = F(x1,x2,…,xN,+,•)’ ):

■ Si implementa una PDN

■ Se si tratta di un funzione NON NEGATA di sole

variabili negate ( Z = F(x1’,x2’,…,xN’,+,•) ): :

■ Si implementa una PUN

■ Scelto il tipo di rete da realizzare si passa alla sua

implementazione per mezzo di transistor (interruttori)

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Procedura di sintesi (2)

■ Per la realizzazione di una PDN (PUN)

■ Si parte dall’operatore logico a precedenza minore (tenendo

conto delle parentesi)

■ Se si tratta di una OR bisogna scegliere fra due possibili

strade quindi si crea una biforcazione con due percorsi in

parallelo

■ Se si tratta di una AND bisogna invece chiudere il percorso

solo quando entrambe le condizioni sono vere quindi si

mettono i rispettivi transistor in serie

■ Si procede allo stesso modo passando via via agli operatori a

maggiore precedenza

■ Realizzata la rete PDN (PUN) per dualità si realizza la rete

complementare PUN (PDN), mettendo in parallelo i blocchi che erano

in serie e mettendo in serie ciò che era in parallelo.

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Procedura di sintesi (3)

Tornando

all’esempio:

Z=[A●(B+C)+D]’

(2) Seleziono il primo

operatore da applicare.

E’ una disgiunzione

quindi

lo

realizzo

creando un bivio tra 2

possibili percorsi.

A ●(B+C)

(5) Per un blocco

corrispondente a

più variabili ripeto

la

procedura

dall’inizio

12 Ottobre 2012

D

(1) Implemento una

PDN

perché

devo

portare l’uscita a 0.

(3)

Disgiunzione:

ramificazione del circuito

che si divide nei due

percorsi corrispondenti

alle due possibili opzioni.

(4) Se un blocco contiene

una

sola

variabile

corrisponde

ad

un

transistor con il gate

pilotato dalla variabile.

CI - Logica Combinatoria

Massimo Barbaro

Procedura di sintesi (4)

(6) Ripeto la procedura per il

sottoblocco rimanente.

A●(B+C)

(7) Seleziono il primo

operatore da applicare.

E’ una AND quindi

corrisponde

a

due

percorsi che devono

essere

chiusi

contemporaneamente

(serie).

A

D

(8) Se un blocco contiene

una sola variabile quello

corrisponde

ad

un

transistor.

B+C

(9)

Per

un

blocco

corrispondente a più

variabili

ripeto

la

procedura dall’inizio

12 Ottobre 2012

(10) Procedo con i blocchi rimanenti. Se

in un blocco ci sono più variabili ma un

solo tipo di operatore (come nel caso in

esempio) si sostituisce direttamente con

un parallelo (se l’operatore è la OR) o

serie (se l’operatore è la AND) di tanti

transistor quante sono le variabili.

CI - Logica Combinatoria

Massimo Barbaro

Procedura di sintesi (5)

Z=[A●(B+C)+D]’

(11) Si procede adesso, PER DUALITA’,

alla realizzazione della PUN.

Applico De Morgan

A

D

Z = [A●(B+C)+D]’=

Z = [A●(B+C)]’●D’=

Z = [A’+(B+C)’]●D’=

Z = [A’+B’●C’]●D’

B

C

12 Ottobre 2012

(12) Come si vede, tutti gli operatori AND

sono diventati OR e viceversa. La forma

finale è quella di una PUN perché

funzione NON NEGATA di variabili

negate.

CI - Logica Combinatoria

Massimo Barbaro

Esempio

Z=AB

Funzione (non negata) di sole OR e AND: non è

implementabile né con un PUN né con un PDN

A

B

A

Ecco perché è preferibile

implementare

una

generica funzione con sole

NAND e NOR

12 Ottobre 2012

Z1=(AB)’

B

CI - Logica Combinatoria

Massimo Barbaro

Z=AB

AOI

Implementazione diretta di 2 livelli di logica con

un solo blocco CMOS statico:

Z=(AB+CD)’

And-Or-Invert

A

B

C

D

Z

L’implementazione diretta usa solo 8

transistor anzi che i 2(4+2)+4+2=18 (2

NAND + INVERTER e 1 NOR +

INVERTER) di una implementazione

puramente logica

12 Ottobre 2012

CI - Logica Combinatoria

A

C

B

D

Massimo Barbaro

OAI

Implementazione diretta di 2 livelli di logica con

un solo blocco CMOS statico:

F=[(A+B)(C+D)]’

A

C

B

D

Z

Or-And-Invert

12 Ottobre 2012

CI - Logica Combinatoria

A

B

C

D

Massimo Barbaro

Dimensionamento

Un’opportuna tecnica di dimensionamento

consente di avere caratteristiche statiche e

dinamiche ottimali

In particolare è desiderabile avere delle

caratteristiche di trasferimento simmetriche e dei

tempi di propagazione confrontabili nelle due

possibili commutazioni (HL e LH)

Bisogna chiedersi da cosa dipendono i tempi di

propagazione

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Tempi di propagazione

Come nel caso del singolo inverter, anche per una generica porta

CMOS è possibile calcolare i tempi di propagazione facendo

riferimento ad un modello semplificato con una capacità di carico CL

fra uscita e massa e delle resistenze equivalenti che rappresentino i

MOS

Per ottenere la capacità CL che conterrà i contributi di tutte le

capacità parassite nei vari nodi si sfruttano le tecniche viste per

l’inverter (l’uso del teorema di Miller per trasformare le capacità

gate/drain in capacità drain/massa)

La capacità di carico ottenuta deve poi essere caricata o scaricata

dalla rete di pull-up o pull-down che si è attivata

Si fa riferimento al caso peggiore (worst case) ossia a quelle

commutazioni che implicano la presenza di un solo percorso

conduttivo per la carica o scarica della capacità

Si calcola il transistor equivalente (sfruttando serie e paralleli)

corrispondente al percorso attivato e poi si applica la formula per

calcolare il tempo di propagazione classico dell’inverter

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Serie e parallelo di MOS

Nel seguito faremo le ipotesi semplificative (solo

parzialmente vere a causa dell’effetto body ed altri effetti

del secondo ordine):

K MOS in serie con W=W0 e L=Lmin sono equivalenti ad un

MOS di lunghezza L=KLmin e W=W0 o ad un MOS con L=Lmin

e W=W0/K (K volte più resistivo)

K MOS in paralello di larghezza W=W0 sono equivalenti ad un

solo MOS con W=KW0 (K volte più conduttivo)

2

1

1

1

2

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

2

Modello del primo ordine

In un modello del primo ordine si può pensare

che tutti i MOS in serie (o parallelo) lungo un

percorso si combinino in un solo MOS

equivalente di W/L opportuna, avente quindi una

certa resistenza equivalente (Req)

La capacità equivalente sarà la somma della

capacità parassite presenti su tutti i nodi

attraversati dal percorso di scarica (Ceq)

Identificate resistenza e capacità equivalente si

può calcolare il tempo di propagazione con la

solita formula:

tp=0.69ReqCeq

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

MOS in serie

W

W

L

L

Questo ovviamente a patto

che le larghezze siano le

stesse altrimenti avremo in

serie due canali differenti

quindi non si potrebbe

equiparare la struttura ad un

singolo MOS.

W

2L

12 Ottobre 2012

Il nodo in comune è

equipotenziale

(silicio

fortemente drogato, quasi

metallico), quindi è come se i

2 canali fossero esattamente

uno dopo l’altro ossia se ci

fosse un unico transistor ma

lungo il doppio.

CI - Logica Combinatoria

Massimo Barbaro

MOS in parallelo

Pista di metallo: corto circuito

Allo stesso potenziale : come un cortocircuito

W

L

W

L

2W

L

12 Ottobre 2012

Se:

■ i source e i drain sono cortocircuitati

tra loro e

■ i gate sono allo stesso potenziale

(come se fossero cortocircuitati)

Allora è come se i due MOS fossero

affiancati fra loro.

In tal caso sarebbero equivalenti ad un

singolo MOS di larghezad oppia.

Questo ovviamente a patto che le

lunghezze siano le stesse altrimenti

avremo in parallelo due canali

differenti, quindi non si potrebbe

equiparare la struttura ad un singolo

MOS.

CI - Logica Combinatoria

Massimo Barbaro

Esempio: NAND a 2 ingressi: tpHL

A

Calcolo di tpHL

B

B

Z=(AB)’

A

R2

R1

CL

Ceq =C1 + CL

C1

Req =R1 + R2 = 2RN

Si considera la somma di tutte di le

resistenze attraversate e la somma della

capacità di tutti i nodi che devono essere

scaricati (compresi i nodi interni)

12 Ottobre 2012

CI - Logica Combinatoria

tpHL =0.69Req Ceq

Massimo Barbaro

Esempio: NAND a 2 ingressi: tpLH

A

Calcolo di tpLH

B

B

Z=(AB)’

R3

CL

Ceq = CL

A

Si considera la somma di tutte di le

resistenze attraversate e la somma della

capacità di tutti i nodi che devono essere

scaricati (compresi i nodi interni)

12 Ottobre 2012

Req = R3 = RP

CI - Logica Combinatoria

tpLH =0.69Req Ceq

Massimo Barbaro

Dimensionamento

Allora per fare in modo di equalizzare i tempi di salita e discesa (di

caso peggiore) bisogna fare in modo che ciascun percorso di salita

(costituito da PMOS) abbia la stessa resistenza equivalente di

ciascun percorso di discesa (costituito da NMOS).

Bisogna equalizzare ciascun percorso singolarmente perché il caso

peggiore è quello in cui un solo percorso è attivo. Ovviamente se

più percorsi fossero attivi contemporaneamente il tempo di

propagazione sarebbe minore ma è necessario prevedere che il

circuito funzioni correttamente nella situazione più svantaggiosa.

Ricordando che la resistenza equivalente è data dalla somma delle

singole resistenze e che ogni resistenza è inversamente

proporzionale a kn (kp) bisognerà equalizzare sia il k degli NMOS a

quello di un NMOS singolo a dimensione minima (basta agire sulle

W) che quello dei PMOS (in questo caso per dimensionare bisogna

anche tenere conto della diversa mobilità dei PMOS).

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Calcolo di Ron

La

Ron

è

sicuramente

inversamente

proporzionale alla W ed alla mobilità del

transistor (visto che la ID compare al

denominatore)

Perciò a parità di W la Ron di un pmos è circa 2

volte quella di un nmos

Per avere un pmos ed un nmos con Ron circa

equivalenti

bisogna

dimensionare,

come

nell’inverter, Wp=2Wn in modo da compensare

con la Wp la minore mobilità delle lacune

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Tempo di propagazione

Come visto nell’esempio per fare in modo che i

tempi della commutazione HL e LH siano uguali

è necessario dimensionare i PMOS e gli NMOS

in modo che 2Rn=Rp

Per fare questo è necessario dimensionare gli

NMOS con W=2 in modo che la loro serie sia

equivalente ad un NMOS di W=1

A questo punto è necessario dimensionare i

PMOS con W=2 in modo che siano equivalenti

ad un NMOS con W=1

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Dimensionamento ottimo

Il dimensionamento finale è

Bisogna avere sempre in mente A

il caso peggiore (worst-case).

In questo esempio i due NMOS

sono sempre in serie, mentre i

PMOS

possono

condurre

singolarmente

o

contemporaneamente.

Ovviamente se capita che i due

PMOS siano entrambi accesi il

tempo di propagazione sarà

ulteriormente minore

12 Ottobre 2012

CI - Logica Combinatoria

2

B

2

Z=(AB)’

B

A

2

2

Massimo Barbaro

Dimensionamento ottimo

In generale si fa in modo che ciascun

percorso di NMOS verso massa sia

equivalente ad un NMOS con W=1 e

che ciascun percorso di PMOS verso

l’alimentazione sia equivalente ad un

PMOS con W=2 (che è poi equivalente

ad un NMOS con W=1).

Il rapporto di 2 fra PMOS e NMOS non

è esatto (il rapporto fra le mobilità degli

NMOS e dei PMOS è leggermente

maggiore) ma è utile per rendere i

tempi

abbastanza

simili

senza

occupare troppa area.

12 Ottobre 2012

CI - Logica Combinatoria

D

4

B

A

8

4

C

8

A

D

2

1

Massimo Barbaro

B

2

C

2

Tempo di propagazione: modello di Elmore

Un modello più raffinato per il calcolo del tempo di

propagazione dovrà tenere conto che le resistenze, in

realtà, non si sommano linearmente.

Quello che, al primo ordine, può essere ricondotto ad un

circuito compatto è, in realtà, un circuito distribuito.

Infatti, alcuni dei transistor si trovano nel percorso di

scarica di certi capacitori e non di altri.

E’ necessario, per tenere conto di questo fatto, ricorrere

al modello di Elmore

Terremo conto solo di situazioni in cui commuta un

solo segnale per volta, sia perché è altamente

improbabile

che

2

segnali

commutino

contemporaneamente, sia per ragioni di semplicità.

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Modello di Elmore

Si applica ad una rete di resistenze e capacità se:

Si tratta di un albero (una rete senza anelli chiusi)

Tutti i capacitori hanno un terminale a massa

Esiste un solo ingresso

R1

Ingresso

s

1

R2

R3

3

C3

C1

In tale situazione il modello di

Elmore consente di calcolare la

costante di tempo (RC) per la

propagazione di un segnale fra

l’unico nodo di ingresso ed il

generico nodo i-esimo.

12 Ottobre 2012

CI - Logica Combinatoria

2

R4

4

C2

Massimo Barbaro

C4

Modello di Elmore

La costante di tempo che descrive l’evoluzione

della tensione al nodo i-esimo in corrispondenza

di una variazione all’ingresso è:

N

Di Ck Rik

k 1

Dove il termine Rik rappresenta la resistenza dovuta al percorso condiviso

fra la sorgente s e ciascuno dei due nodi i e k. Mentre Ck è la capacità

associata al nodo k.

Rik R j R j percorsi(s i) percorsi(s k )

Nel caso della rete precedente, ad esempio, la resistenza condivisa dai nodi 2 e 4 e dai

nodi 3 e 4 è data da:

R42 R43 R1 R2

Dunque:

D 4 C1R1 C2 R1 R2 C3 R1 R2 C4 R1 R2 R4

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Modello di Elmore

Intuitivamente, il modello di Elmore si può comprendere

dal seguente ragionamento (qualitativo):

R1

1

R2

R3

3

C3

C1

2

R4

4

C2

12 Ottobre 2012

C4

Perché la capacità C3 ha effetto

sulla costante di tempo di C4?

Per il fatto che, se C3 commuta

contemporaneamente a C4, la

sua corrente di carica (o scarica)

deve per forza passare attraverso

la resistenza R2.

La corrente che scorre in R2,

dunque, non è interamente

disponibile per la commutazione

del nodo 4 ma viene in parte

utilizzata dal nodo 3.

Questo limita la velocità con cui

può commutare il nodo 4.

CI - Logica Combinatoria

Massimo Barbaro

Modello di Elmore: logica combinatoria

Le conseguenze nel caso del calcolo del tempo di propagazione di una

porta CMOS consistono nel modo in cui si calcolerà la costante di tempo

equivalente ReqCeq

N

t pHL( LH ) 0.69 Ck Rik

k 1

La sommatoria è estesa a tutti i

nodi che si scaricano (tutti i

nodi connessi verso massa).

Per la commutazione HL il percorso da prendere in considerazione è

quello fra il nodo di uscita (il nodo i-esimo del modello di Elmore) e la

massa (la sorgente s del modello).

Per la commutazione LH il percorso è fra l’uscita e la VDD (che diventa la

sorgente s)

Su tale percorso saranno presenti tante resistenze quanti sono i MOS da

attraversare ed una capacità per ogni nodo.

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Modello di Elmore: NAND 2 ingressi

Commutazione HL

Consideriamo sempre

una sola commutazione

alla volta.

Non sono possibili due

commutazioni

contemporanee.

Ci sono 2 possibili casi di commutazione:

a) A : 0 -> 1

B=1

(commuta A)

b) A = 1

B : 0 -> 1

(commuta B)

A questi due casi corrispondo diverse configurazioni

degli intetturrori durante la scarica.

A

M3

B

A

B

M4

Z=(AB)’

M2

M1

12 Ottobre 2012

Caso a)

M3 si spegne, M4 resta spento.

M1 si accende, M2 è acceso.

Caso b)

M3 resta spento, M4 si spegne.

M1 è acceso, M2 si accende.

CI - Logica Combinatoria

Massimo Barbaro

Modello di Elmore: NAND (HL)

Commutazione HL

b)

a)

Z

Z

R2

R1

CL

R1

C1

La rete si riduce a questa

perché i due PMOS sono spenti

(resistenza infinita) ed i 2 nodi

(corrispondenti a C1 e CL)

devono

entrambi

essere

scaricati.

12 Ottobre 2012

CL

R2

XC

1

C1 è già scarica!

La rete si riduce a questa

perché i due PMOS sono spenti

(resistenza infinita), mentre C1

è già scarica perché il transistor

M1 era già acceso ed aveva già

scaricato il nodo 1.

CI - Logica Combinatoria

Massimo Barbaro

Modello di Elmore: NAND (HL)

Commutazione HL

Applicando il modello di Elmore alla rete:

N

percorso

di scarica

k 1

Z

CL

R2

R1

t pHL 0.69 Ck Rik

a)

Esteso a TUTTI i nodi della rete

C1

t pHL 0.69R1C1 R1 R2 CL

0.69R1 C1 CL R2CL

Se il dimensionamento è ottimo e R1=R2=Rn

t pHL 0.69R1 C1 2CL

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Modello di Elmore: NAND (HL)

Commutazione HL

Applicando il modello di Elmore alla rete:

N

percorso

di scarica

t pHL 0.69 Ck Rik

b)

Z

k 1

CL

R2

R1

XC

t pHL 0.69CL R1 R2

1

C1 è già scarica!

12 Ottobre 2012

C1 è già scarica (cortocircuitata fra

massa e massa) quindi non fa parte

della rete di Elmore.

CI - Logica Combinatoria

Massimo Barbaro

Modello di Elmore: NAND (LH)

Commutazione LH

Consideriamo sempre

una sola commutazione

alla volta.

Non sono possibili due

commutazioni

contemporanee.

Ci sono 2 possibili casi di commutazione:

a) A : 1 -> 0 B = 1

(commuta A)

b) A = 1

B : 1 -> 0

(commuta B)

A questi due casi corrispondo diverse configurazioni

degli intetturrori durante la scarica.

A

M3

B

A

B

M4

Z=(AB)’

M2

M1

12 Ottobre 2012

Caso a)

M3 si accende, M4 resta spento.

M1 si spegne, M2 è acceso.

Caso b)

M3 resta spento, M4 si accende.

M1 è acceso, M2 si spegne.

CI - Logica Combinatoria

Massimo Barbaro

Modello di Elmore: NAND (LH)

Commutazione LH

a)

R3

R4

Z

CL

R2

Z

C1 è sconnessa

dal percorso di

carica!

R1

C1

La rete si riduce a questa perché i

due M1 e M4 sono spenti (resistenza

infinita) ed i 2 nodi (corrispondenti a

C1 e CL) devono entrambi essere

caricati.

12 Ottobre 2012

b)

CL

C1

La rete si riduce a questa perché i M3

e M2 sono spenti dunque la capacità

parassita C1 è disconnessa dal

percorso di carica e NON influisce sul

tempo di propagazione.

CI - Logica Combinatoria

Massimo Barbaro

Modello di Elmore: NAND (LH)

Commutazione LH

Applicando il modello di Elmore alla rete:

N

t p 0.69 Ck Rik

a)

percorso di carica

R3

Z

CL

R2

Esteso a TUTTI i nodi della rete

k 1

t pHL 0.69R3C1 R3CL

0.69R3 C1 CL

C1

Questo perché nel tener conto di C1 bisogna considerare il percorso

resistivo che il CL e C1 hanno in comune nel percorso di carica, ossia

della sola resistenza R3 (a differenza di quanto succede nel caso HL).

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Modello di Elmore: NAND (LH)

Commutazione LH

Applicando il modello di Elmore alla rete:

b)

N

percorso di carica

R4

Z

CL

R1

C1

C1 è sconnessa

dal percorso di

carica!

12 Ottobre 2012

t p 0.69 Ck Rik

k 1

t pHL 0.69R4CL

C1 non è nel percorso di carica di CL

quindi non fa parte della rete di Elmore

che ci interessa!

CI - Logica Combinatoria

Massimo Barbaro

Modello di Elmore: considerazioni

Come si vede dal risultato ottenuto, le resistenze associate a

ciascun MOS non si sommano semplicemente, ma vengono pesate

più o meno a seconda che si trovino più vicine alla massa

(all’alimentazione) o meno.

I MOS più vicini alla sorgente (cioè alla massa o all’alimentazione),

infatti, devono essere attraversati dalla corrente di scarica (o carica)

di tutti i nodi intermedi e quindi limitano maggiormente il tempo di

commutazione.

Da questo punto di vista, il MOS più critico è quello più in basso

(nelle HL) o in alto (nelle LH) che nella sommatoria delle resistenze

di Elmore compare in ogni termine.

Inoltre, anche se sto calcolando il tempo di propagazione LH (HL)

non ci si può dimenticare delle capacità parassite della PDN (PUN)

che potrebbero comunque avere un effetto e trovarsi sul percorso di

carica (scarica).

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Modello di Elmore: generalizzazione

x1

x2

xN

…

J percorsi di carica

F(x1,x2,…,xN)

Fra i vari percorsi di

scarica

(carica)

si

identifica quello di caso

peggiore, ovvero quello

a cui corrispondono le

massime capacità e

resistenza equivalenti.

A tale percorso si applica

il modello di Elmore per

ricavare la costante di

tempo e dunque il tempo

di propagazione.

…

x1

x2

xN

J+K=2N percorsi

K percorsi di scarica

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Caso peggiore

Fra i percorsi quale è quello di CASO PEGGIORE?

Quello a cui corrispondono:

■ Maggior numero di transistor (resistenze) coinvolti

■ Maggior numero di nodi (capacità) coinvolti

Evidentemente possono esistere più percorsi di caso

peggiore equivalenti fra loro e basterà calcolarne uno solo.

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Tempo di propagazione: riassunto

1

Si identificano il percorso di carica e di scarica di caso peggiore

2

Si calcola la Req di ciascun MOS su tale percorso

3

Si calcolano le Ci associate a ciascun nodo del percorso

4

Si calcola la costante di Elmore D associata al percorso mediante

la formula:

HL ( LH ) C1 R1 C2 R1 R

... CL R1 R2 ... RN

5

Si calcola il tempo di propagazione con l’approssimazione del

primo ordine:

t pHL( LH ) 0.69 HL ( LH )

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Fan-In e Fan-Out

Porte CMOS con elevato fan-in diventano rapidamente

poco pratiche.

Infatti il numero totale di MOS è pari a 2N (con N

numero di ingressi) quindi all’aumentare degli ingressi

aumenta rapidamente l’area

All’aumentare degli ingressi aumentano anche i

transistor in serie e quindi la porta diventa più lenta (Ron

più grandi). Questo fenomeno è solo in parte risolvibile

con la tecnica di dimensionamento vista, dato che

all’aumentare della W dei mos aumentano anche le

capacità parassite e quindi CL quindi ad un certo punto

non si ha più miglioramento di tp (il gate si fa da carico)

Anche gli elevati fan-out riducono la velocità della porta

(ogni gate connesso significa due transistor di carico, il

pmos e lo nmos)

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Fan-in elevati:tecniche di progettazione

In caso di elevato fan-in è possibile ricorrere a

tecniche di progettazione per aumentare la

velocità dei gate:

Aumentare la W dei transistor per compensare

l’elevata capacità di carico (è una soluzione

insufficiente perché all’aumentare di W aumentano

anche le capacità parassite e quindi il carico)

Usare un dimensionamento progressivo, ossia fare

più conduttivi quei transistor che pilotano i carichi

più elevati dovendo pilotare un numero maggiore di

capacità parassite

Riordinare i mos in modo che quelli pilotati dai

segnali più critici siano connessi ai nodi con minori

capacità parassite

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Fan-In: dimensionamento progressivo

I transistor più vicini alla massa devono pilotare

capacità via via più grandi (la somma di CL e di

tutti i nodi parassiti intermedi)

CL

Si dimensiona MN a dimensione

minima, poi gli altri via via più larghi

WN-1=WN(CL+CpN-1)/CL

…

Cp2

M2

Cp1

W1=WN(CL+CpN-1 +…+Cp1)/CL

12 Ottobre 2012

MN

CI - Logica Combinatoria

M1

Massimo Barbaro

Fan-In: riordinamento

Se un segnale è particolarmente critico in

genere è quello che arriva per ultimo (quando gli

altri hanno già commutato)

In tale situazione è preferibile usare

il segnale critico per pilotare il

transistor MN che è il più vicino a CL

e quindi “vede” la sola CL se gli altri

hanno già commutato.

Se invece si usasse il segnale

critico per pilotare M1 la capacità

“vista”

sarebbe

Ctot=CL+CpN-1+…+Cp1

12 Ottobre 2012

CI - Logica Combinatoria

CL

MN

Cp2

M2

Cp1

M1

Massimo Barbaro

Logica CMOS: riassunto

L’escursione fra i simboli 0 e 1 è la massima

possibile (VDD)

Nessuna dissipazione di potenza statica

Tempi di propagazione confrontabili

Una porta a N ingressi ha 2N transistor (N nmos

e N pmos)

Ad ogni ingresso sono connessi sempre 2 mos

(1 nmos e 1 pmos)

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Logica Combinatoria

Pseudo-NMOS

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

Limiti del CMOS

Il principale limite della logica CMOS è il numero

di mos (sempre pari a 2N) utilizzati che la rende

poco pratica per porte con elevato fan-in. Inoltre

in ingresso presenta sempre i gate di 2 mos (p e

n) quindi un carico almeno doppio del minimo

concepibile

(trascurando

i

diversi

dimensionamenti del p e del n)

Per questo motivo sono state concepite logiche

alternative che barattano alcune caratteristiche

CMOS in cambio di un minore ingombro e

maggiore velocità

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Logica pseudo-NMOS

La logica pseudo-NMOS implementa la sola rete PDN e

sostituisce la PUN con un solo mos (un PMOS sempre

acceso) che si incarica di portare a VDD l’uscita ogni

volta che la PDN è aperta

F(x1,x2,...,xN)

x1

x2

12 Ottobre 2012

...

xN

PDN

CI - Logica Combinatoria

Massimo Barbaro

Pseudo-NMOS : funzionamento

L’analisi del circuito di massima è molto semplice e si basa su

quanto detto per la logica combinatoria CMOS statica con la sola

differenza che la rete di pull-up (PUN) è sostituita da un transistor

SEMPRE acceso (il PMOS con il gate connesso a massa).

Per riconoscere la funzione impementata, dunque, bisogna

verificare la sola PDN:

Per ogni combinazione per cui la PDN risulta accesa (ossia in cui c’è

almeno un percorso chiuso verso massa) l’uscita sarà bassa (questo

a patto che il PMOS venga opportunamente dimensionato, come

vedremo in seguito).

Per ogni combinazione per cui la PDN risulta spenta (nessun

percorso verso massa), il nodo di uscita sarà cortocircuitato a VDD

dal PMOS e dunque l’uscita sarà alta.

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Pseudo-NMOS: funzionamento

Per una combinazione x1, x2, ... xN per cui nessun percorso della PDN

è chiuso verso massa l’intera PDN è un circuito aperto, dunque:

Il PMOS è sicuramente acceso,

dunque equivalente a un resistenza

F(x1,x2,...,x3)

F(x1,x2,x3)=VDD

xN

...

x1

x2

12 Ottobre 2012

PDN

La PDN è spenta dunque

un circuito aperto

CI - Logica Combinatoria

L’uscita

è

cortocircuitata a VDD dunque

è alta.

Massimo Barbaro

Pseudo-NMOS: funzionamento

Per una combinazione x1, x2, ... xN per cui almeno un percorso della

PDN è chiuso verso massa, l’intera PDN è una resistenza, dunque:

Il PMOS è sicuramente acceso,

dunque equivalente a un resistenza

F(x1,x2,...,x3)

F(x1,x2,x3)=?

xN

...

x1

x2

12 Ottobre 2012

PDN

La PDN è accesa dunque

una resistenza

CI - Logica Combinatoria

Quanto vale l’uscita?

Dipende dal valore delle

due resistenze (perché

dipende dal partitore

resistivo).

Massimo Barbaro

Pseudo-NMOS: funzionamento

Quanto vale l’uscita in caso di PDN accesa?

Rp

Ip

VRp= Rp Ip

Le resistenze sono in serie, dunque sono

equivalenti ad una resistenza pari alla loro

somma. La caduta di potenziale ai capi della

serie delle due resistenze è pari a VDD.

VDD= (Rp+Rn)In

I p= I n

In

Rn

VRn= Rn In

In= VDD/(Rp+Rn)

Sostituiamo il valore ottenuto nell’espressione di

VRn:

La corrente che scorre nelle due

resistenze è la stessa (il carico NON

assorbe corrente perché è il gate di

un MOS).

12 Ottobre 2012

Da questo ricaviamo la corrente:

VOUT = VRp= VDDRn/(Rp+Rn)

Se la resistenza equivalente della PDN (Rn) è

molto più piccola di quella del PMOS tale valore

tende a zero e dunque l’uscita è bassa.

CI - Logica Combinatoria

Massimo Barbaro

Pseudo-NMOS: VOL

Il ragionamento svolto è però solo qualitativo perché in realtà i transistor MOS

non sono delle semplici resistenze ma hanno una caratteristica fortemente

non-lineare. Bisogna tenere conto di questo se si vuole conoscere il valore

esatto della tensione di uscita bassa che NON può essere pari a 0.

Per potere scrivere le equazioni corrette applichiamo il solito ragionamento

svolto anche per l’inverter CMOS e per la logica statica CMOS ed osserviamo

che (come visto nella slide precedente), la corrente del PMOS deve essere

UGUALE alla corrente del NMOS (lo NMOS equivalente alla PDN). Questo

perché non esiste alcun altro percorso possibile per la corrente, quindi tutta la

corrente che scorre nel PMOS deve fluire verso massa attraverso la PDN.

Per potere procedere dobbiamo conoscere le condizioni di conduzione dei

due transistor (cutoff, triodo o saturazione).

Osserviamo che si desidera ottenere una porta logica con un buon margine di

rumore, dunque si vuole che la VOL sia la più bassa possibile.

In tali condizioni, poiché la VOL coincide con la VDS del NMOS equivalente,

tale transistor sarà ragionevolmente in triodo. Per la stessa ragione, la VSD

del PMOS sarà invece molto grande e dunque avremo ragionevolmente un

PMOS in saturazione.

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Pseudo-NMOS: VOL

Come arriviamo a scrivere l’equazione per ricavare VOL?

Ip

VSDp=VDD-VOL

VOL

VDD

12 Ottobre 2012

In

VDSn=VOL

CI - Logica Combinatoria

Se la VOL deve essere

piccola, lo NMOS tende ad

andare in triodo ed il

PMOS in saturazione.

Facciamo questa ipotesi

che sarà verificata se

otterremo un valore di VOL

inferiore a VDSATn.

Massimo Barbaro

Pseudo-NMOS: VOL

Siccome stiamo calcolando VOL l’ingresso sarà chiaramente alto.

Scriviamo l’equazione della corrente del PMOS che è in saturazione e ha la

VSG pari a VDD e la VSD pari a VDD-VOL.

Scriviamo l’equazione della corrente del NMOS che è in triodo e ha la VGS

pari a VDD e la VDS pari a VOL.

Uguagliamo le due correnti e ipotizziamo VTn=|VTp|

Saturazione

Triodo

keq ,n VDD VTn VOL

VOL VDD VTn

12 Ottobre 2012

keq ,n

2

VOL

VDD VTn

2

2

VDSATp

k pVDSATp VDD VTn

2

VDSATp

2

VDSATp VDD VTp

keq ,n

2

kp

CI - Logica Combinatoria

Massimo Barbaro

Pseudo-NMOS: VOL

Supponendo di volere avere il valore più basso possibile VOL2 sarà

trascurabile rispetto a VOL e si ottiene quindi:

VOL

VDSATp

k pVDSATp VDD VTp

2

keq ,n VDD VTn

Se si considera inoltre che, tipicamente VTn VTnp e che VDSATp<<VDD-VTp

l’espressione si semplifica ulteriormente in:

VOL

12 Ottobre 2012

p

Wp

n

VDSATp

Lp

Weqn

Ln

CI - Logica Combinatoria

Massimo Barbaro

Pseudo-NMOS: VOL

Osservando la cosa dal punto di vista grafico, rappresentiamo le due correnti

(del PMOS e del NMOS) su uno stesso grafico (funzione di VOUT). Il valore

della tensione di uscita corrisponde al punto di intersezione fra le curve (il

punto in cui le due correnti sono uguali).

NMOS (molto conduttivo

IDn , IDp

perché grande W/L)

Vin=VDD

PMOS (poco conduttivo

perché piccolo W/L)

Al diminuire del W/L del PMOS la curva si

schiaccia verso il basso ed il punto di

intersezione si sposta a sinistra.

VOL

12 Ottobre 2012

Vout

CI - Logica Combinatoria

Massimo Barbaro

VOL : considerazioni

La diminuzione della VOL comporta una diminuzione del

rapporto di forma del PMOS rispetto al NMOS

equivalente.

Tale riduzione di può ottenere sia facendo lo NMOS più

conduttivo (più largo), sia riducendo la conduttività del

PMOS ossia NON facendolo a lunghezza minima

La maggiore controindicazione della diminuzione di VOL è

data dal fatto che, richiedendo una minore conduttività per

il PMOS, causa anche un aumento del tempo di

propagazione LH

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Consumo di potenza statico

Quando l’uscita è pari a VOL entrambi i transistor sono accesi e

scorre corrente (anche staticamente) fra alimentazione e massa.

Il consumo di potenza statica associata è dato dal prodotto della

corrente (che coincide con la corrente di saturazione del PMOS) per

l’alimentazione

La riduzione di VOL comporta la riduzione della corrente di

saturazione del PMOS, il che comporta anche una diminuzione

della potenza dissipata. La controindicazione è l’aumento del tempo

di propagazione LH (determinato proprio dalla corrente di

saturazione del PMOS).

PSTAT

VDSATp

VDD k p VDSATp VDD VTp

2

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Tempo di propagazione

I tempi di propagazione HL e LH sono differenti:

tpHL è determinato dalla rete PDN e può essere valutato col

solito metodo (metodo di Elmore)

HL 0.69 Ci Rik

Da notare che, in realtà, il tempo di propagazione è leggermente

più alto perché, dato che il PMOS è sempre acceso, la scarica è

ostacolata dalla corrente di saturazione del PMOS

tpLH è determinato dal transistor PMOS di pull-up che carica la

CL con una corrente circa costante (la corrente di saturazione

del pmos). Si applica ancora il metodo di Elmore.

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Esempio: NAND

La rete PDN porta a 0 l’uscita

solo se A e B sono entrambi 1,

in tutti gli altri casi l’uscita è

portata a 1 dal pmos di pull-up

F=(AB)’

A

B

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Pseudo-NMOS: caratteristiche

E’ una logica a rapporto, dove cioè il rapporto

fra le dimensioni dei transistor determina le

caratteristiche statiche (VOL)

Il PMOS di pull-up ha specifiche contraddittorie:

dovrebbe essere poco conduttivo (kp<<keq,n) per

minimizzare VOL e il consumo di potenza statico

ma dovrebbe anche essere molto conduttivo per

minimizzare il tempo di propagazione LH

(caricare rapidamente CL)

E’ comunque una logica statica perché l’uscita è

sempre connessa a VDD o 0

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Vantaggi delle logiche pseudo-NMOS

Osservando che:

Il numero totale di transistor è N+1 (con N numero di ingressi)

Ogni porta pseudo-NMOS, avendo come carico un’altra porta

pseudo-NMOS, dovrà pilotare un solo transistor (poiché non

c’è la PUN, bisogna pilotare il solo transistor della PDN)

Risulta che:

E’ minore il numero di capacità parassite interno alla porta

logica e dunque è minore il numero di nodi che portano un

contributo nella formula di Elmore.

E’ minore il valore della capacità di carico (dato che bisogna

pilotare solo un NMOS e non la coppia PMOS-NMOS)

Dunque è minore il tempo di propagazione

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Svantaggi della logica pseudo-NMOS

Osservando che:

La PUN è sempre accesa dunque quando l’uscita deve essere

bassa (ossia quando si accende anche la PDN) esiste un

percorso diretto fra alimentazione e massa.

L’uscita bassa NON è pari a zero ma dipende dal rapporto fra

le dimensioni del PMOS e degli NMOS

Risulta che:

Si ha dissipazione di potenza statica

Si ha una riduzione del minore margine di rumore (in caso di

uscita bassa). Infatti per uscita bassa il PMOS e la PDN

conducono entrambi, quindi VOL0

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Logica Combinatoria

Logiche dinamiche

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

Logiche dinamiche

Le logiche dinamiche sono logiche in cui le

uscite non sono sempre connesse ad una delle

alimentazioni

L’informazione

viene

temporaneamente

immagazzinata sotto forma di carica elettrica su

un capacitore

In genere sono logiche temporizzate, in cui cioè

si alternano fasi di valutazione della funzione

logica e di memorizzazione sulle capacità

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Concetto di base (n)

F(x1,x2,x3)

CL

x1

x2

x3

PDN

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Concetto di base (n): precarica

PRECARICA

F(x1,x2,x3)

x1

x2

x3

12 Ottobre 2012

CL

PDN

CI - Logica Combinatoria

=0

Il PMOS è acceso e

cortocircuita l’uscita a

VDD.

Lo NMOS è spento ed

interdice il percorso

verso massa.

Il capacitore si carica

a VDD.

Massimo Barbaro

Concetto di base (n): valutazione

VALUTAZIONE

F(x1,x2,x3)

CL

x1

x2

x3

12 Ottobre 2012

PDN

CI - Logica Combinatoria

=1

Il PMOS è spento ed

interdice il percorso

verso VDD.

Lo NMOS è acceso ed

abilita il percorso verso

massa.

Se la combinazione di

ingresso è tale da

chiudere un percorso

nella PDN il capacitore

si scarica verso massa.

Massimo Barbaro

Concetto base

Quando il segnale (detto segnale di clock) è

basso la PDN è disabilitata (lo NMOS apre il

percorso a massa) ed il PMOS carica la CL in

uscita a VDD

Quando è alto il PMOS si interdice e la PDN è

abilitata, quindi l’uscita potrà andare a 0 (se

PDN si chiude) o restare a 1 (altrimenti)

Il funzionamento è quindi sincronizzato dal

segnale e le operazioni sono divise in 2 fasi

Precarica (=0)

Valutazione (=1)

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Concetto di base (p)

La stessa cosa si può

fare con una PUN. Le

fasi

saranno

ovviamente invertite.

x1

x2

x3

PUN

F(x1,x2,x3)

12 Ottobre 2012

CL

CI - Logica Combinatoria

Massimo Barbaro

Caratteristiche

Sono necessari solo N+2 transistor

Ogni ingresso vede il carico di un solo MOS.

Non è una logica a rapporto.

Non c’è dissipazione di potenza statica (il percorso

statico fra VDD e massa è sempre interdetto).

La PDN (o PUN) può essere realizzata come nel caso

del CMOS statico (quindi implementa solo funzioni

invertenti).

E’ più veloce e compatta dell’equivalente CMOS statico

(meno capacitori parassiti e minor carico dovuto alla

presenza di un solo gate anzi che due).

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Prestazione statiche

Il maggiore problema delle logiche dinamiche è

l’immunità al rumore.

Poiché la commutazione dipende da soli

transistor NMOS si può dire che VM, VIL e VIH

coincidono con VT (tensione di soglia)

Questo rende i margini di rumore molto bassi

Inoltre il fatto che l’uscita alta sia immagazzinata

come carica su una capacità rende il circuito

molto sensibile a disturbi (accoppiamenti

capacitivi).

La presenza di correnti di leakage può scaricare

inavvertitamente l’uscita alta.

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Soglia logica

VDD

VTH

NMOS acceso

0

VIN

F(x1,x2,x3)

CL

Visto che il PMOS è

spento

l’uscita

è

disconnessa da VDD.

Basta

allora

che,

all’aumentare di VIN, si

crei

un

percorso

conduttivo verso massa,

ossia che lo NMOS si

accenda anche di poco

(VIN appena al di sopra

della tensione di soglia

VTH) perché l’uscita vada

a 0.

Inverter dinamico

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Prestazioni dinamiche

Il tempo di propagazione LH è zero! Questo

perché la fase di precarica pone già a 1 l’uscita

prima ancora della valutazione

In

realtà

bisognerebbe

tenere

conto

dell’incidenza della precarica nel tempo totale di

valutazione. In molti progetti però questa fase

può essere fatta coincidere con fasi in cui

comunque la logica non dovrebbe funzionare

(ad esempio in un processore, mentre avviene

la decodifica dell’istruzione) e quindi è realistico

pensare che la precarica non incida sul ritardo

totale.

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Cause di rumore

Le correnti di perdita (leakage) attraverso la PDN

possono scaricare l’uscita quando deve essere alta

diminuendo l’affidabiltà del circuito

Clock feedthrough: il segnale di clock () varia

rapidamente quindi può, per accoppiamento capacitivo,

deteriore il segnale alto immagazzinato sulla capacità

Charge sharing: se anche il percorso a massa attraverso

la PDN non si chiude può capitare che qualche segnale

di ingresso intermedio si chiuda mettendo CL in parallelo

con altre capacità e diminuendo il valore alto

immagazzinato

In generale il segnale di uscita più sensibile ai disturbi è

quello alto perché è memorizzato sulla capacità senza

percorsi a bassa impedenza verso VDD

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Leakage

IDp

Z

IDn

A

IS

Inverter dinamico

12 Ottobre 2012

Le correnti di leakage sono dovute alla presenza

dei diodi parassiti associati alle diffusioni di drain

del PMOS e degli NMOS ed alla correnti di

sottosoglia.

Tali correnti tendono a scaricare (caricare nel

caso di IDp) il capacitore.

A seconda di quale corrente prevale, l’uscita

tenderà a scaricarsi (o caricarsi) in un tempo

ragionevolmente lungo.

Sarà necessario ripartire con una nuova fase di

precarica/valutazione prima che la scarica

(carica) porti la tensione di uscita al di sotto della

soglia logica del circuito successivo.

Questo impone un limite inferiore alla frequenza

di funzionamento del circuito dinamico (minima

frequenza di funzionamento).

CI - Logica Combinatoria

Massimo Barbaro

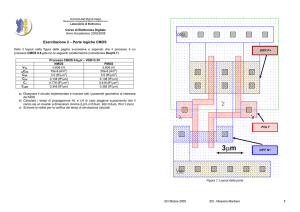

Charge sharing

A

Z

CL

B

Ca

Se durante la fase di precarica A e B sono entrambi bassi, il PMOS sarà in

grado di caricare il solo capacitore CL (Ca è isolato a causa del NMOS

spento).

Se durante la fase di valutazione (con il PMOS spento) B rimane basso

(quindi interdice il percorso verso massa, imponendo che l’uscita resti alta)

ma A diventa alto, il capacitore Ca viene messo in parallelo con CL ed i due

capacitori devono quindi condividere la stessa carica elettrica che si

redistribuisce su entrambi.

Per la conservazione della carica elettrica, la carica presente in CL prima

della commutazione di A (Q0= CL VDD) deve ora essere presente sul

capacitore totale dato dalla somma dei due (sono in parallelo). Poiché la

carica è la stessa, ma il capacitore è diverso, deve essere cambiata la

tensione:

Q1 = (CL + Ca) VOUT

Q1 = Q0

=>

VOUT = CL / (CL + Ca) VDD

(nota bene che questo è vero solo se il valore così calcolato è inferiore a VDD di almeno una

soglia, altrimenti lo NMOS pilotato da B si spegnerebbe e non sarebbe più vero che i due

capacitori sono esattamente in parallelo)

Questo impone un minimo valore del rapporto fra i due capacitori per

garantire che VOUT non scenda sotto la soglia logica del circuito seguente.

Ovviamente, più complessa è la porta logica, maggiore è il numero di

tranistor, quindi maggiore la capacità complessiva Ca, dunque più difficile

evitare il problema del charge sharing.

Porta NAND dinamica

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Logiche dinamiche in cascata (1)

Mettere due blocchi in cascata può comportare problemi

di distruzione del segnale

x1

x2

x3

OUT1

PDN x4

OUT2

PDN

x5

12 Ottobre 2012

CI - Logica Combinatoria

Se in corrispondenza degli

ingressi deve essere OUT1=0

(e OUT2=1) possono verificarsi

problemi.

Infatti all’inizio della valutazione

OUT1=1

(precarica).

Tale

valore

potrebbe

fare

commutare OUT2 a 0 se la

PDN1 non è abbastanza veloce

nello scaricare OUT1

Massimo Barbaro

Logiche dinamiche in cascata (2)

Esempio

OUT1 = (AB)’

OUT2 = ( OUT1 + C)’ = ( (AB)’ + C)’

OUT1

Questo circuito ha dei

potenziali problemi per

alcune combinazioni in

cui l’uscita deve essere

alta.

OUT2

A

C

B

12 Ottobre 2012

CI - Logica Combinatoria

Ad

esempio,

la

combinazione A=1, B=1,

C=0.

In

tali

condizioni

dovrebbe

essere

OUT1=0 e OUT2=1.

Massimo Barbaro

Logiche dinamiche in cascata (3)

A=1, B=1, C=0

In precarica risulta OUT1=1 e OUT2=1.

Al termine della precarica inizia la valutazione.

M1

A

M2

B

OUT1

All’inizio

della

valutazione

chiudono M4 e M8.

M5

M3

M4

12 Ottobre 2012

M8

Poiché OUT1 è precaricato a 1 si

chiude il percorso M6-M8 che tende

a scaricare OUT2.

OUT2

M7

M6

si

C

Contemporaneamente si chiude il

percorso M2-M3-M4 che scarica

OUT1.

Nel funzionamento corretto, quando

OUT1 va a 0 apre il percorso M6-M8

lasciando OUT2 a 1 come deve

essere.

CI - Logica Combinatoria

Massimo Barbaro

Logiche dinamiche in cascata (4)

A

B

Possibile malfunzionamento

M1

OUT1

M5

OUT2

M2

M7

M6

M3

M4

12 Ottobre 2012

M8

Se la scarica attraverso il

percorso M6-M8 è più veloce

della scarica attraverso M2M3-M4, il nodo OUT2 si

scarica prima che OUT1 vada

a 0.

Una volta che OUT2 si è

scaricato, l’uscita risulterà 0 e

non sarà più possibile riportarla

C a 1 perché M5 è spento.

Dunque nel momento in cui

OUT1 arriverà finalmente a 0,

l’uscita

OUT2

sarà

erroneamente pari a 0.

CI - Logica Combinatoria

Massimo Barbaro

Logica DOMINO

Una possibile soluzione al problema è offerta

dalle logiche DOMINO

OUT1

x1

x2

x3

La presenza dell’inverter

impedisce che OUT1=1 in

precarica

scarichi

inavvertitamente OUT2.

PDN

12 Ottobre 2012

OUT2

PDN

x4

x5

CI - Logica Combinatoria

Infatti quando OUT1 è

precaricato a 1 in ingresso

alla PDN di OUT2 c’è uno 0

che NON può chiudere

percorsi di scarica.

La logica è detta domino

perché la valutazione della

prima

PDN

innesca

l’eventuale

commutazione

della seconda PDN e così via

Massimo Barbaro

Logiche DOMINO: caratteristiche

Possono implementare solo funzioni non

invertenti (per la presenza dell’inverter)

Sono molto compatte e veloci

Vengono utilizzate nella realizzazione di blocchi

logici critici (ALU di processori ad alte

prestazioni)

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Logica np-CMOS

Una altra possibile soluzione al problema è

offerta dalle logiche np-CMOS

’

OUT1

x1

x2

x3

PDN

PUN

x4

x5

’

12 Ottobre 2012

CI - Logica Combinatoria

OUT2

Quando (in precarica)

OUT1=1 la rete PUN di

OUT2 sarà sicuramente

disabilitata (un 1 in

ingresso su dei PMOS

NON

può

chiudere

percorsi di carica) quindi

all’inizio

della

valutazione

non

ci

possono essere errori

indesiderati.

Massimo Barbaro

Logiche np-CMOS: caratteristiche

Sono ancora più veloci delle DOMINO (per via

dell’eliminazione dell’inverter fra i due blocchi

dinamici).

Danno luogo ad implementazioni molto dense e

compatte.

Vengono utilizzate nella realizzazione di blocchi

logici critici (ALU di processori ad alte

prestazioni).

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Logica Combinatoria

Logica a pass-transistor

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

Logica a pass-transistor

Visto che un MOS è equivalente ad un interuttore si può pensare di

realizzare una funzione logica semplicemente scegliendo, a

seconda della combinazione in ingresso, cosa fare passare in uscita

fra 1 e 0

E’ NECESSARIO che almeno uno dei percorsi sia chiuso in modo

che il valore dell’uscita sia determinato in ogni istante

x1

x2

x3

F(x1,x2,x3)

Rete di

interruttori

Può essere sostituito da un semplice buffer, cioè una

porta non invertente col solo compito di isolare l’uscita

dall’ingresso (un buffer NON invertente sono 2 inverter in

cascata).

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Esempio

La porta F=AB può essere realizzata così:

B

A

B

F=AB

B’

Se B=1 passa A (quindi 0 o 1 a

seconda del valore di A). Il

secondo percorso è necessario

per garantire una logica statica,

cioè un percorso a bassa

impedenza fra l’uscita e 0 o

VDD

per

qualunque

configurazione di ingresso

La porta F=(AB)’ può essere realizzata così:

B

A

B

F=(AB)’

B’

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Esempio: multiplexer

La logica a pass-transistor è particolarmente adatta alla

realizzazione di multiplexer

Nel caso di un multiplexer 2x1 (due ingressi A e B e 1

ingresso di selezione S), la cui espressione logica è

F=AS’+BS si ha la seguente implementazione:

S’

A

F=AS’+BS

S

B

12 Ottobre 2012

CI - Logica Combinatoria

Se S=0 passa A (quindi 0

o 1 a seconda del valore

di A). Se S=1 passa B

(quindi 0 o 1 a seconda

del valore di B).

Massimo Barbaro

Esempio: multiplexer 4x1

Nel caso di un multiplexer 4x1 (mux4x1) in cui

gli ingressi di selezione sono 2 bit (S1 e S0):

S0’

S1’

S0

S1’

S0’

S1

A

B

C

D

S0

12 Ottobre 2012

Z=AS0’S1’+BS0S1’+CS0’S1+DS0S1

Se S S =00 passa A

Se S S =01 passa B

Se S S =10 passa C

Se S S =11 passa D

S1

CI - Logica Combinatoria

1

0

1

0

1

0

1

0

Massimo Barbaro

Logica a pass-transistor: sintesi

Il meccanismo è quello di costruire un diverso

percorso per le varie combinazioni di ingressi

(non necessariamente tutte, ma quelle

mutuamente esclusive).

A seconda della combinazione di ingresso uno

ed uno solo dei percorsi si chiuderà.

Tale percorso porterà in uscita uno degli

ingressi

Il meccanismo è particolarmente indicato nella

realizzazione di circuiti di selezione (come i

mutliplexer)

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Realizzazione degli switch

Gli interruttori potrebbero essere realizzati con dei

singoli MOS.

A

X

VGS

VGS

Y

ID

Se Y<X

A

X

Se Y>X

Y

ID

Il transistor MOS è un dispositivo simmetrico, dunque non si può definire uno dei due

terminali souce o drain senza sapere il verso della corrente.

Il source è il terminale verso cui è diretta la corrente. Dunque a seconda di come scorre la

corrente cambia la caduta di potenziale che devo considerare (VGS) per verificare se il

transistor è acceso o spento.

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Realizzazione degli switch

Un singolo transitor non è in grado di trasferire in modo

perfetto l’informazione.

A=VDD

VDD

In questo caso, infatti:

VGS = VDD – Y

VGS

Y

ID

Il transistor si spegne quando:

VGS < VTH

Ossia

Y > VDD – VTH

Lo NMOS ha problemi nel trasferire le tensioni alte. La

massima tensione che compare su Y prima che lo switch si

interdica è VDD – VTH

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Realizzazione degli switch

Il PMOS ha evidentemente il problema opposto.

In questo caso, infatti:

VSG = Y – 0 = Y

A=0

VSG

0

ID

Y

Il transistor si spegne quando:

VSG < VTH

Ossia

Y < VTH

Il PMOS ha problemi nel trasferire le tensioni basse. La

minima tensione che compare su Y prima che lo switch si

interdica è VTH

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Problemi con switch singoli

Un 1 “sporco” causa un consumo di potenza statico

nell’inverter che segue l’interruttore. Infatti il PMOS sarà

sull’orlo della conduzione ed avrà una corrente non nulla

Y=VDD- VTH

A=VDD

X=VDD

12 Ottobre 2012

C

CI - Logica Combinatoria

Ishort

Massimo Barbaro

Transmission gate

La soluzione al problema è l’uso dei transmission gate

A

X

Y

A’

Simbolo

Il PMOS è pilotato dal segnale di ingresso del NMOS

invertito. Il PMOS si occupa di correggere gli 1 “sporco”

e lo NMOS di correggere gli 0 “sporchi”.

Svantaggi: ho bisogno del PMOS e del segnale invertito

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Esempio: multiplexer

Realizzazione di un multiplexer a 2 ingressi (un blocco

che, in base ad un segnale di selezione S sceglie se

fare passare A o B)

S

A

F=(AS+BS’)’

S’

B

S

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Esempio: XOR

E’ possibile realizzare un XOR con soli 4

transistor

B

F=(AB’+A’B)

Non VDD !

Se B=1 l’uscita

e A’

B’

A

A

B

Se B=0 l’uscita

è A (l’inverter è

disabilitato)

Non 0 !

B’

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Tempo di propagazione

Si usa il solito metodo e si sostituiscono i MOS

con resistenze equivalenti (Ron)

Si utilizza il metodo di Elmore (esattamente

come per gli altri circuiti visti) per calcolare la

costante di tempo da cui si ricava il tempo di

propagazione ()

Al valore così calcolato (il tempo di

propagazione attraverso la rete di switch)

bisogna aggiungere il tempo di propagazione

del buffer (invertente o non invertente)

tp = 0.69 + tp,buff

12 Ottobre 2012

Tempo di propagazione del buffer in

cascata

CI - Logica Combinatoria

Massimo Barbaro

Tempo di propagazione

Si dimostra (col modello di Elmore) che, in una

catena di switch il tempo di propagazione è:

C

C

C

N ( N 1)

t p 0.69 ReqC

2

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

N: numero

interruttori

Implementazione con soli NMOS

L’implementazione con soli NMOS (che risolve il

problema di dovere avere a disposizione tutti i

segnali di ingresso negati) è possibile usando il

level restorer

A=5

X=5

12 Ottobre 2012

Y

CI - Logica Combinatoria

Quando passa un

1 è sufficiente che

il nodo Y sia

abbastanza

alto

da fare commutare

l’inverter

per

accendere il levelrestore che porta

Y stesso a VDD

Massimo Barbaro

Porte tri-state

Porte logiche bidirezionali

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

Alta impedenza

Il segnale in alta impedenza (Z) è utilizzato per

gestire bus bidirezionali:

Unità 1

Unità 2

BUS

Se l’Unità 1 (ad esempio il processore) deve potere

inviare/ricevere dati a/da l’Unità 2 (ad esempio la

memoria) è necessario che entrambe siano in grado di

pilotare lo stesso bus.

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro

Alta impedenza

Quando una delle due unità pilota il bus (cioè tenta di imporne il

valore di tensione) l’altra lo deve rilasciare (ossia mettersi in alta

impedenza) in modo da non generare confitti. Altrimenti si avrebbe

la situazione in figura con un corto-circuito fra alimentazione e

massa e l’impossibilità di stabilire la tensione d’uscita del bus (che

potrebbe essere anche VDD/2 a seconda del dimensionamento dei

transistor).

1

12 Ottobre 2012

0

CI - Logica Combinatoria

Massimo Barbaro

Alta impedenza

Da un punto di vista circuitale

l’alta impedenza si può

implementare

così.

EN=1 la porta è abilitata e

rappresenta

un

inverter

EN=0 il pmos in alto e lo

nmos in basso sono interdetti

e l’uscita è in alta impedenza

(non c’è percorso né verso

massa né verso VDD)

Questa porta è detta tri-state

(ha tre stati logici: 0,1 e Z)

EN’

IN

OUT

EN

12 Ottobre 2012

CI - Logica Combinatoria

Massimo Barbaro