PortelogichecontransistorMOSFET:NOTeNAND

Descrizione dell’Esperienza

Con questa esperienza si realizza una porta logica di tipo Inverter (NOT) e una porta logica di tipo NAND a

due ingressi.

L’implementazione avviene utilizzando transistor di tipo NMOS o PMOS, di cui sono disponibili i data sheet,

resistenze da 330 Ohm, LED . Tutti i componenti sono con package per montaggio su scheda a foro

passante e la scheda utilizzata è una scheda di prototipazione che permette di non saldare i componenti.

L’alimentazione può essere fornita da una batteria da 9V.

L’esperienza permette di provare tutte le possibili combinazioni logiche all’ingresso della porta logica e di

verificare la tabella della verità dall’osservazione del diodo LED che, collegato all’output, si illumina qualora

l’output è a ‘1’ ossia a livello logico alto.

La corrente nel LED è limitata dalla resistenza serie di valore 330 Ohm.

Alcuni dati dei datasheet dell’nmos e del pmos

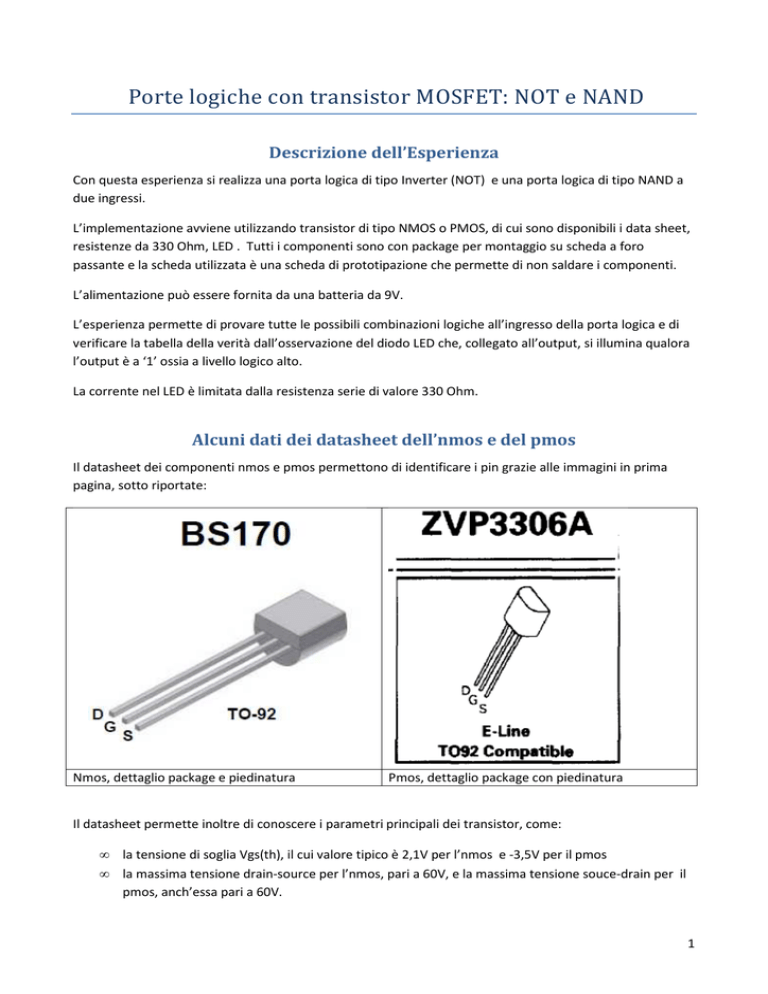

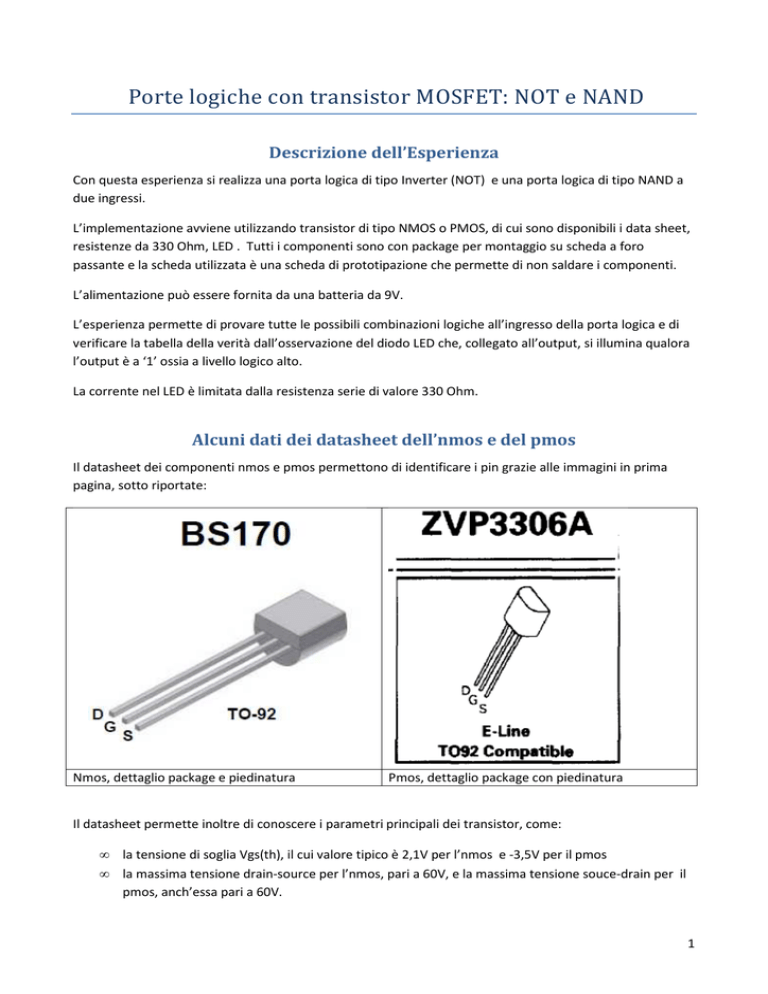

Il datasheet dei componenti nmos e pmos permettono di identificare i pin grazie alle immagini in prima

pagina, sotto riportate:

Nmos, dettaglio package e piedinatura

Pmos, dettaglio package con piedinatura

Il datasheet permette inoltre di conoscere i parametri principali dei transistor, come:

•

•

la tensione di soglia Vgs(th), il cui valore tipico è 2,1V per l’nmos e -3,5V per il pmos

la massima tensione drain-source per l’nmos, pari a 60V, e la massima tensione souce-drain per il

pmos, anch’essa pari a 60V.

1

Nmos, alcuni parametri riportati dal datasheet: massima VDS e tensione di soglia

Pmos, alcuni parametri riportati dal datasheet: massima VDS e tensione di soglia

Porta NOT

A

0

1

Simbolo della porta logica NOT e sintassi dell’operazione di NOT logico

Z

1

0

tabella della verità

2

schema elettrico della porta NOT

schema elettrico da usare per l’esperienza, caso con

A=0

schema elettrico da usare per l’esperienza, caso con

A=1

3

foto della breadboard, caso con A=0

Schema sovrapposto a foto della breadboard, caso con A=0

4

Schema sovrapposto a foto della breadboard, caso con A=1

Porta NAND

A

0

0

1

1

Simbolo della porta logica NAND e sintassi dell’operazione di NAND

logico

B

0

1

0

1

Z

1

1

1

0

tabella della verità

5

schema elettrico della porta NAND

6

schema elettrico da usare per l’esperienza, caso con A=0 e B=0

schema elettrico da usare per l’esperienza, caso con A=0 e B=1

schema elettrico da usare per l’esperienza, caso con A=1 e B=0

7

schema elettrico da usare per l’esperienza, caso con A=1 e B=1, unica combinazione a tenere spento il

LED.

foto della breadboard, caso con A=0 e B=1

8

Schema sovrapposto a foto della breadboard, caso con A=0 e B=1

Schema sovrapposto a foto della breadboard con modello dei mosfet semplificato a switch, caso con A=0 e

B=1

9

Estratti dal datasheet dell’nmos

10

11

Estratti dal datasheet del pmos

12

13