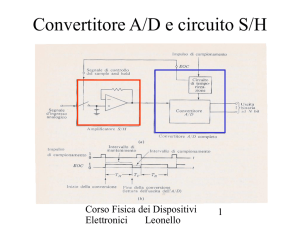

Convertitore A/D e circuito S/H

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

1

Convertitori A/D (1)

I convertitori A/D sono oggetti abbastanza complicati.

Solitamente includono:

•Uno stadio di comparazione

•Uno di immagazzinamento del risultato della comparazione

•Uno stadio di decodifica del risultato della comparazione

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

2

Convertitori A/D a Comparatori

in parallelo (1)

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

3

Convertitori A/D a Comparatori in parallelo (2)

Campo di variabilità dell’ingresso analogico: 0 – V0 .

Uscita digitale: 3 bit (LSB, 2SB, MSB)

Campo di ingresso diviso in otto bande:

0 – V0/14 - V0/7 - V02/7 - V03/7 - V04/7 -V05/7 - V06/7 - V013/14 - V0

errore di quantizzazione = V0/14 = S/2 con S = V0/7.

Un comparatore è un dispositivo a due ingressi (segnale e riferimento)

ed una uscita che se il segnale è maggiore del riferimento vale V(1),

altrimenti se il segnale è minore del riferimento vale V(0).

I comparatori servono a determinare in quale intervallo cade il valore

analogico della tensione

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

4

Convertitori A/D a Comparatori in parallelo (3)

A seconda del numero di bit varia il numero di

comparatori necessari. Più precisamente 2N – 1.

Nel nostro caso: 8 - 1 = 7.

Tutti i comparatori avranno una uscita V(0) tranne uno

che avrà uscita V(1). L’uscita viene trasferita a dei

flip-flop di tipo D, e attraverso un comando inviato da un

clock viene trasferita all’uscita dei flip-flop.

I registri sono seguiti da un decodificatore che converte

l’indicazione in un codice binario a 3 bit.

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

5

Cascata di Convertitori A/D a comparatori (1)

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

6

Cascata di Convertitori A/D a comparatori (2)

Si possono ridurre il numero dei comparatori al prezzo

di un aumento dei tempi di elaborazione:

4) ADC-1 fornisce i tre bit più significativi del valore

della tensione;

2) l’uscita di ADC-1 viene inviata ad un convertitore

D/A.

3) Si sottrae dal segnale iniziale il VD/A, e si invia il

segnale così ottenuto ad ADC-2 che fornirà i 3 bit

meno significativi.

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

7

Cascata di Convertitori A/D a comparatori (3)

Per fare un convertitore a 6 bit servirebbero 63 comparatori

nella versione completamente parallela; ne servono 14+1

operazionale per la sottrazione nella configurazione a 3 bit

a 2 stadi, al prezzo di due cicli di clock.

Le fonti di errore sono:

• La conversione analogico-digitale di ADC-1

• La conversione digitale-analogica del DAC

• Il dispositivo di sottrazione che effettua (V- VD/A).

• L’amplificatore di (V- VD/A).

• La conversione analogico-digitale ADC-2

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

8

Convertitori A/D ad approssimazioni successive

Si prende un intervallo di tensione (0-V0), e si divide in due

parti (0-V0/2) e (V0/2 - V0 ). Se il segnale cade nel primo

intervallo il bit corrispondente (MSB) sarà 0, se cade nel

secondo sarà 1.

Poi si prende l’intervallo in cui cade il segnale e lo si

suddivide in altri due intervalli: es. se cade nel primo

intervallo lo suddividiamo in: (0 – V0/4) e (V0/4 - V0/2 )

4e si ripete il procedimento di paragone.

Questo fino ad arrivare alla assegnazione del LSB.

Per avere un errore che sia sempre +- 0.5 LSB, occorre in

pratica sommare al segnale il valore 0.5 LSB.

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

9

Es. convertitore A/D a 3-bit (1)

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

10

Es. convertitore A/D a 3-bit (2)

Il convertitore viene realizzato con i seguenti blocchi logici:

3) 5 Flip-Flop che realizzano un contatore ad anello

(1 per ogni bit + 1 read-out + 1 clear)

5) 3 Flip-Flop per registrare i bit

6) 1 convertitore D/A per fornire una tensione da comparare

a quella del segnale

8) 1 comparatore

9) 1 circuito S/H (sample and hold) per rendere disponibile

il segnale durante tutto il ciclo di conversione (5 colpi di

clock)

6) Uno stadio di abilitazione dell’output digitale (3 porte AND)

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

11

Es. convertitore A/D a 3-bit (3)

Nel primo ciclo di clock il contatore ad anello fornisce un segnale

V(1) al flip-flop FF3 e V(0) ai flip-flop FF2 e FF1.

Q3 = V(1), mentre Q2 = Q1 = V(0)

Il segnale digitale Q3Q2Q1 = 100 viene quindi convertito dal D/A,

gli viene sommato 0.5 LSB e viene inviato al comparatore per la

prima comparazione (V0).

Se il segnale Va > V0 allora l’uscita del comparatore è V(0)

Le porte AND G3,G2,G1 saranno disabilitate nel ciclo successivo,

altrimenti saranno abilitate.

Nel secondo ciclo di clock, è il flip-flop FF2 che riceve il valore V(1)

mentre FF3 e FF1 valgono V(0).

Se G3 è disabilitata Q3 mantiene il valore precedente, e Q2 =V(1).

Quindi il valore Q3Q2Q1 = 110 viene inviato al D/A per la seconda

conversione.

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

12

Es. convertitore A/D a 3-bit (4)

Si somma di nuovo il valore 0.5 LSB e si compara con Va.

Se adesso Va < V0 l’uscita del comparatore C0 = V(1), e le porte

G3,G2,G1 saranno abilitate nel ciclo successivo.

Nel terzo ciclo di clock, è il flip-flop FF1 che riceve il valore V(1)

mentre FF3 e FF2 valgono V(0).

Poiché QB =V(0) Q3=V(1) mentre poiché QC= V(1) Q2=V(0).

Infine Q1= V(1), e quindi al D/A viene inviato il valore Q3Q2Q1 = 101.

Si somma di nuovo 0.5 LSB, e si compara.

Nel quarto ciclo di clock, le uscite Q3Q2Q1 indicheranno il numero

digitale che dovrà essere poi trasferito nel ciclo successivo.

Nel quinto ciclo di clock, FFE trasmette alle porte GAGBGC il segnale

abilitante che permette di leggere i bit in uscita dal dispositivo e

contemporaneamente, può essere usato come segnale di abilitazione

Fisica dei Dispositivi

Elettronici

Leonello Servoli

13

del circuito S/H perCorso

effettuare

un nuovo

campionamento.

Convertitori A/D a conteggio (1)

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

14

Convertitori A/D a conteggio (2)

I blocchi logici sono:

2) Un contatore ad anello (1 flip-flop per ogni bit)

3) 1 convertitore D/A

4) 1 comparatore

5) 1 circuito S/H

6) 1 linea di controllo H

7) 1 uscita digitale (1 porta per ogni bit)

L’idea di base è la seguente:

Il contatore ad ogni ciclo di clock emette un numero,

che sarà convertito dal D/A e comparato col segnale V0.

Se V0 sarà maggiore il contatore continuerà a contare,

altrimenti smetterà ci contare.

Dopo un certo periodo, sufficiente al contatore per raggiungere il fondo scala,

viene abilitata la lettura dell’uscita digitale.

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

15

Convertitori A/D a conteggio (3)

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

16

Convertitori A/D a doppia rampa (1)

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

17

Convertitori A/D a doppia rampa (2)

L’idea di base è la seguente:

Si carica una capacità usando il segnale Va per un tempo

noto, poi la si fa scaricare usando una tensione nota Vr fino

a quando non torna a zero la tensione applicata al

comparatore e si misura il tempo necessario, che fornisce

una misura diretta del segnale iniziale.

Per t=0, S1 è chiuso, e il segnale Va viene applicato al

condensatore C che si carica secondo la costante di tempo

caratteristica: τ = RC.

L’ingresso del comparatore vale: V0 = -(t/τ)Va .

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

18

Convertitori A/D a doppia rampa (3)

Nel frattempo a t=0 parte il conteggio del contatore a N

Stadi, che dura fino a quando si raggiunge la configurazione

1000000…0. Il tempo necessario è: T1 =2NTc ,

con Tc = intervallo di clock del contatore.

La tensione V0 = -T1Va/ τ = - Va2NTc/τ.

All’istante T1 l’interruttore S1 si chiude su -Vr , ed il

condensatore C inizia a scaricarsi secondo la stessa costante

di tempo τ. Quando V0 = 0 Vr (T2-T1)/τ = VaT1/τ.

T2-T1 = Va 2NTc /Vr = λTc

λ = Va2N/Vr.

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

19

Convertitori A/D a doppia rampa (4)

Il convertitore a doppia rampa è molto preciso, perché

ogni non-linearità del comparatore durante la prima rampa

viene compensata con il comportamento opposto durante

la seconda rampa.

È un dispositivo molto preciso, ma molto lento

(raddoppia il numero di clock necessari)

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

20

Paragone tra Convertitori A/D

Tipo ADC

Velocità

Numero di

(clock vs N bit) componenti

a comparatore

1

molto elevato

ad approssimazioni

N

medio

a doppia rampa

2*N

medio-basso

a conteggio

2N

basso

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

21

Convertitore tensione-frequenza (1)

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

22

Convertitore tensione-frequenza (2)

Si basa sul principio che una tensione Va, applicata ad

un condensatore, lo carica tanto più velocemente quanto

maggiore è la tensione Va.

Il circuito presentato permette alla tensione V0 = -tVa/(RC)

risultante all’ingresso del comparatore di raggiungere il

valore - Vr prima che l’interruttore S venga chiuso facendo

così scaricare il condensatore per poi ricominciare il ciclo.

La frequenza del ciclo è: f = 1/(T+ Td) = 1/T = (RC)Va/Vr

(se T>> Td), cioè f proporzionale a Va .

Quando S è chiuso il segnale digitale (c) va nello stato V(1).

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

23

Convertitore tensione-frequenza (3)

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

24

Specifiche dei Convertitori A/D

Tensione analogica di ingresso: (0,10 V);(-5 V,5 V)

Precisione: 0,02% del fondo scala + 0.5 LSB.

Stabilità in temperatura: 20 ppm del fondo scala /°C

Tempi di conversione: 50 ns – 50 µs .

Formati: binario unipolare, complemento a uno, a due.

Corso Fisica dei Dispositivi Elettronici

Leonello Servoli

25