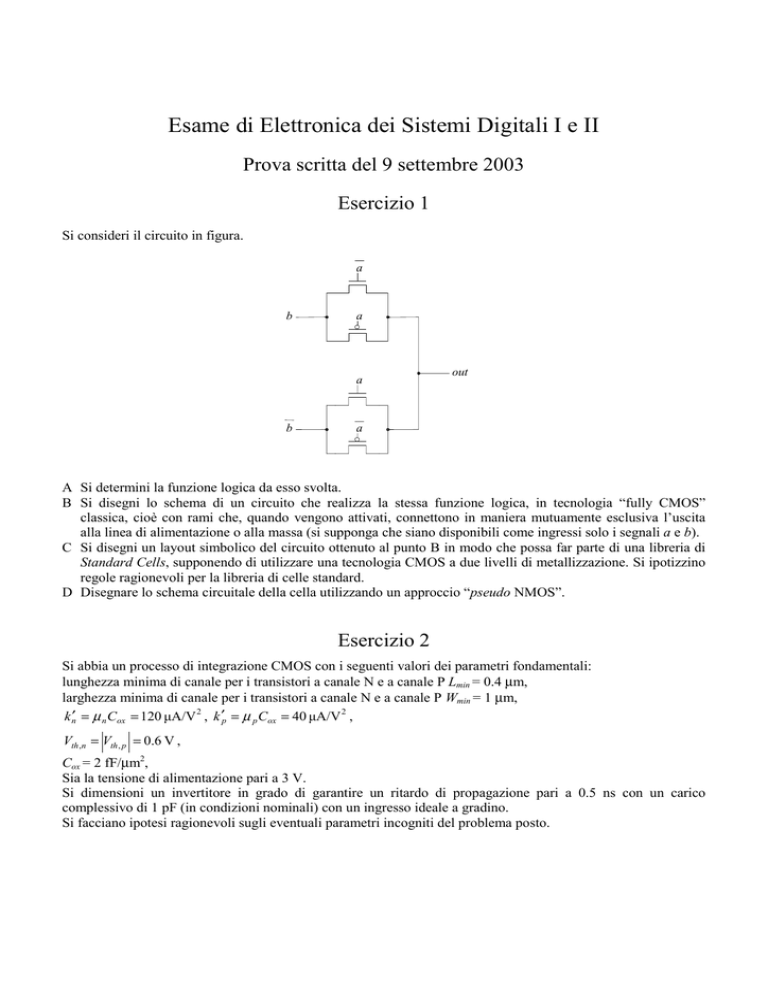

Esame di Elettronica dei Sistemi Digitali I e II

Prova scritta del 9 settembre 2003

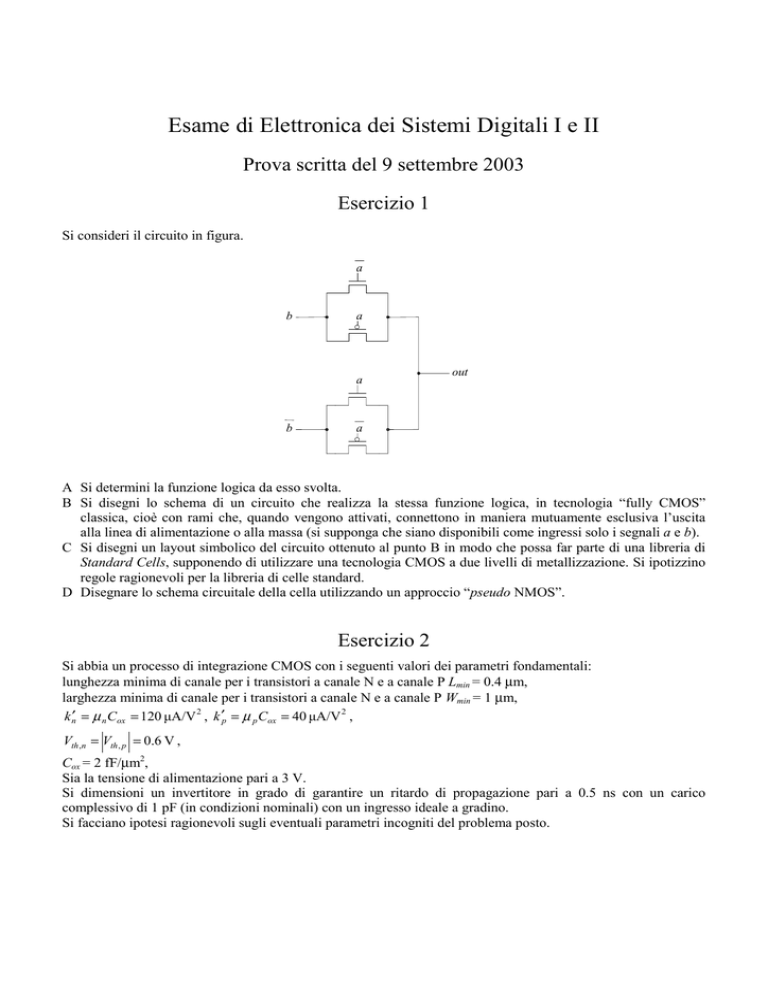

Esercizio 1

Si consideri il circuito in figura.

a

b

a

a

b

out

a

A Si determini la funzione logica da esso svolta.

B Si disegni lo schema di un circuito che realizza la stessa funzione logica, in tecnologia “fully CMOS”

classica, cioè con rami che, quando vengono attivati, connettono in maniera mutuamente esclusiva l’uscita

alla linea di alimentazione o alla massa (si supponga che siano disponibili come ingressi solo i segnali a e b).

C Si disegni un layout simbolico del circuito ottenuto al punto B in modo che possa far parte di una libreria di

Standard Cells, supponendo di utilizzare una tecnologia CMOS a due livelli di metallizzazione. Si ipotizzino

regole ragionevoli per la libreria di celle standard.

D Disegnare lo schema circuitale della cella utilizzando un approccio “pseudo NMOS”.

Esercizio 2

Si abbia un processo di integrazione CMOS con i seguenti valori dei parametri fondamentali:

lunghezza minima di canale per i transistori a canale N e a canale P Lmin = 0.4 µm,

larghezza minima di canale per i transistori a canale N e a canale P Wmin = 1 µm,

k n′ = µ n Cox = 120 µA/V 2 , k ′p = µ p Cox = 40 µA/V 2 ,

Vth ,n = Vth , p = 0.6 V ,

Cox = 2 fF/µm2,

Sia la tensione di alimentazione pari a 3 V.

Si dimensioni un invertitore in grado di garantire un ritardo di propagazione pari a 0.5 ns con un carico

complessivo di 1 pF (in condizioni nominali) con un ingresso ideale a gradino.

Si facciano ipotesi ragionevoli sugli eventuali parametri incogniti del problema posto.

Esercizio 3

Si supponga di avere a disposizione una libreria CMOS con le seguenti celle digitali: Inverter, NAND, NOR

(entrambi fino a 6 ingressi), EXOR negato, Multiplexer, Latch sensibile al livello alto del clock con set e reset

asincroni, Flip-flop DELAY “positive edge triggered” (ETDFF) con set e reset asincroni. Per gli elementi di

memoria sia il set sia il reset sono attivi al livello logico alto; nel caso dell’ETDFF set e reset agiscono sia sul

master sia sullo slave.

Le caratteristiche dinamiche di tali porte siano le seguenti:

Inverter: td = 1 ns;

NAND, NOR, EXOR negato: td = 1.2 ns;

Multiplexer tin.out = 1.1 ns; tsel.out = 0.9 ns;

Latch td,q = 1.3 ns; tck,q = 1.4 ns; tsu = 1 ns; th = 0.5 ns; tr,s = 0.6 ns; tck/2,min = 0.8 ns;

ETDFF tck,q = 1.8 ns; tsu = 1 ns; th = 0.5 ns; tr,s = 0.6 ns; tck/2,min = 0.8 ns;

ove

= tempo di ritardo (o ritardo di propagazione), assunto per semplicità indipendente dal

td

carico e dal numero di ingressi;

= tempo di ritardo tra ingresso ed uscita (per il Multiplexer);

tin.out

tsel.out

= tempo di ritardo tra segnale di abilitazione ed uscita (per il Multiplexer);

= tempo di ritardo tra ingresso ed uscita (sia diritta, sia negata);

td,q

tck,q

= tempo di ritardo tra il fronte del clock e l’uscita (sia diritta, sia negata);

tsu

= tempo di “set-up”;

= tempo di “hold”;

th

tr,s

= tempo tra il fronte del reset (o del set) e l’uscita, sia diritta, sia negata;

tck/2,min = durata minima del semiperiodo di clock (sia a livello positivo sia a livello negativo).

a)

b)

c)

d)

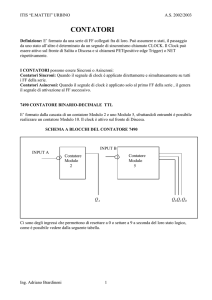

Si progetti un contatore binario sincrono all’indietro per 8, che conti a partire dal fronte di clock 0/1

successivo al rilascio di un segnale di disabilitazione D (Disable, attivo alto), i cui fronti sono supposti per

semplicità sufficientemente distanti dai fronti del segnale di clock.

Determinare la frequenza massima di funzionamento del circuito progettato (cioè la massima frequenza di

clock per cui esso funziona correttamente).

Si disegni lo schema di un circuito che, a partire dall’ottavo fronte 0/1 di clock successivo al rilascio del

segnale di disabilitazione Disable, e poi ogni 8 periodi di clock, generi un’uscita che permane alta per un

intero periodo di clock.

Si supponga che per un guasto l’uscita del secondo Flip Flop a partire da sinistra sia S-A-0. Proporre un

vettore per il test.