ITIS “E.MATTEI” URBINO

A.S. 2002/2003

CONTATORI

Definizione: E’ formato da una serie di FF collegati fra di loro. Può assumere n stati, il passaggio

da uno stato all’altro è determinato da un segnale di sincronismo chiamato CLOCK. Il Clock può

essere attivo sul fronte di Salita o Discesa e si chiamerà PET(positive edge Trigger) o NET

rispettivamente.

I CONTATORI possono essere Sincroni o Asincroni:

Contatori Sincroni: Quando il segnale di clock è applicato direttamente e simultaneamente su tutti

i FF della serie.

Contatori Asincroni: Quando il segnale di clock è applicato solo al primo FF della serie , il genera

il segnale di attivazione al FF successivo.

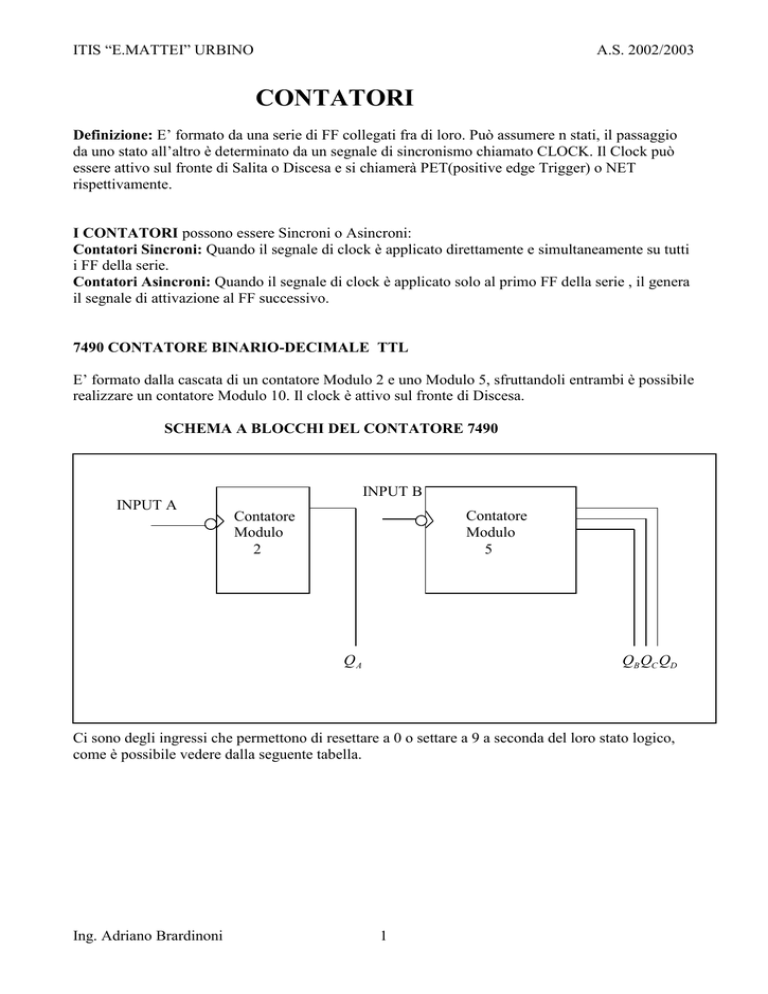

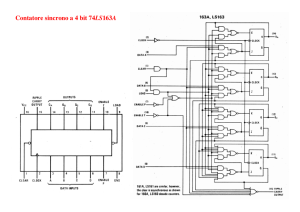

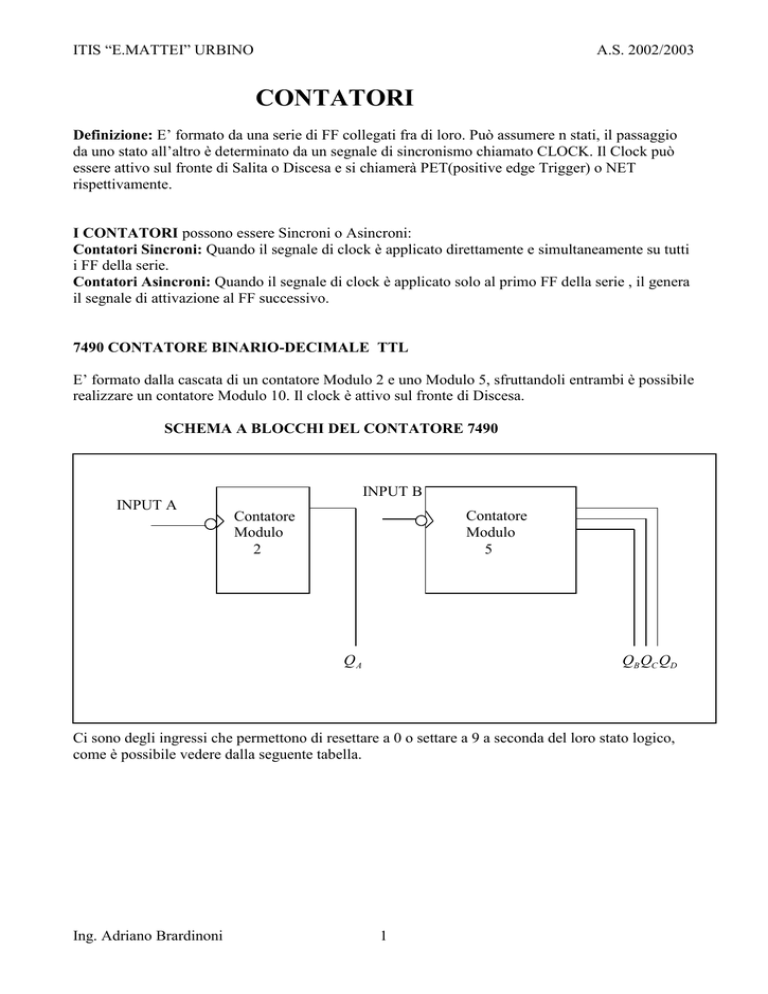

7490 CONTATORE BINARIO-DECIMALE TTL

E’ formato dalla cascata di un contatore Modulo 2 e uno Modulo 5, sfruttandoli entrambi è possibile

realizzare un contatore Modulo 10. Il clock è attivo sul fronte di Discesa.

SCHEMA A BLOCCHI DEL CONTATORE 7490

INPUT B

INPUT A

Contatore

Modulo

5

Contatore

Modulo

2

QA

QB QC QD

Ci sono degli ingressi che permettono di resettare a 0 o settare a 9 a seconda del loro stato logico,

come è possibile vedere dalla seguente tabella.

Ing. Adriano Brardinoni

1

ITIS “E.MATTEI” URBINO

A.S. 2002/2003

FUNZIONAMENTO DEL 7490 IN MODULO 10

Si deve collegare l’uscita Qa all’ingresso INPUT B.

Si deve applicare il clock all’ingresso INPUT A.

FORME D’ONDA DEL CONTATORE BCD MODULO 9 :

Ing. Adriano Brardinoni

2

ITIS “E.MATTEI” URBINO

A.S. 2002/2003

CIRCUITO DI ANTIRIMBALZO ( CLOCK MANUALE )

Il circuito di antirimbalzo è formato da un latch a porte Nand. Questo circuito permette di ovviare

all’inconveniente che si verifica quando si hanno dei contatti metallici che provocano dei rimabalzi

di tensione.

Tali rimbalzi creano dei livelli logici che transitano nella zona di incertezza provocando effetti

indesiderati.

Supponiamo di essere nella posizione A in cui abbiamo R 1 e S 0 che è lo stato di SET, quando

portiamo il deviatore nella posizione B il contatto metallico oscilla prima di stabilizzarsi in tale

situazione.

Appena il contatto metallico tocca la posizione B abbiamo R 0 e S 1 che è lo stato di RESET,

dopo averla toccata inizia ad oscillare portandosi nella situazione R S 1 che è lo stato di

memoria e l’uscita rimarrà nello stato di RESET evitando cosi l’instaurarsi di oscillazione della

tensione d’uscita.

Con questo circuito è possibile realizzare un clock manuale che fornisce delle transizioni positive e

negativi senza rimabalzi.

4511 DECODER BCD/7 SEGMENTI CMOS

Il circuito integrato pilota display a catodo comune senza resistenze limitatrici della corrente per i

segmenti del display.

Presenta degli ingressi di controllo:

LT: ingresso attivo basso che accende tutti i segmenti del display

BI: ingresso attivo basso che spegne tutti i segmenti del dispaly

LE: LATCH ENABLE ingresso attivo alto che memorizza il dato BCD presente agli

ingressi DCBA.

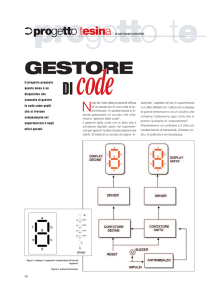

PROGETTO:

Progettare e Realizzare un circuito in grado di visualizzare su un display a sette segmenti il

conteggio modulo 9 di un contatore BCD. Il circuito deve disporre di un interruttore per la

memorizzazione del dato un pulsante per l’accensione di tutti i segmenti del display e unpo per

l’azzeramento del display.

Ing. Adriano Brardinoni

3

ITIS “E.MATTEI” URBINO

A.S. 2002/2003

SCHEMA A BLOCCHI :

CLOCK

MANUALE

VISUALIZZAZIONE

SU DISPLAY

CONATORE

MODULO 10

Circuito di

RESET

Circuito di

LAMP

TEST

Circuito per la

memorizzazione

SCHEMA ELETTRICO:

CIRCUITO DI RESET:

Quando il contatore conta normalmente gli ingressi di controllo sono nella seguente situazione:

R0(1)=1

R0(2)=0 R9(0)=0 R9(1)=0

Cioè con interuttore S4 CHIUSO.

Mentre il contatore è nello stato di reset quando :

R0(1)=1

R0(2)=1 R9(0)=0 R9(1)=0

Cioè con interruttore S4 APERTO.

Ing. Adriano Brardinoni

4