E

I

1.4 - Diodi di potenza

e diodi

di di Schottky

S h ttk

1

1

E

I

Diodi di potenza

Diodi di potenza al silicio a giunzione pn

Valori tipici di VKN

0.7÷1.2 V,

Valori di resistenze tali da mantenere le cadute alla

corrente nominale a 1÷2.2

1÷2 2 V

V.

Correnti nominali da pochi A fino a 4000÷5000 A

A.

Corrente inversa di fuga IR molto piccola rispetto alla

corrente nominale IFN (IFN/IR maggiore di

20000÷40000).

1

2

E

I

Diodi di p

potenza

Se la tensione inversa supera un valore limite BVKA

(tensione di “Breakdown”),

Breakdown ), si ha la scarica a

valanga e la corrente inversa aumenta

bruscamente.

I valori

ao d

di BVKA variano

a a o molto

o to da u

un d

dispositivo

spos t o a

all’altro

at o

e possono andare da poche decine di Volt fino a

6000 V.

Alcuni diodi ((a “valanga

g controllata”)) sono costruiti in

modo da poter sopportare, entro dati limiti di

corrente,, tensione e di durata,, le condizioni di

breakdown.

1

3

E

1

Diodi di potenza

I

4

E

I

Diodi di potenza

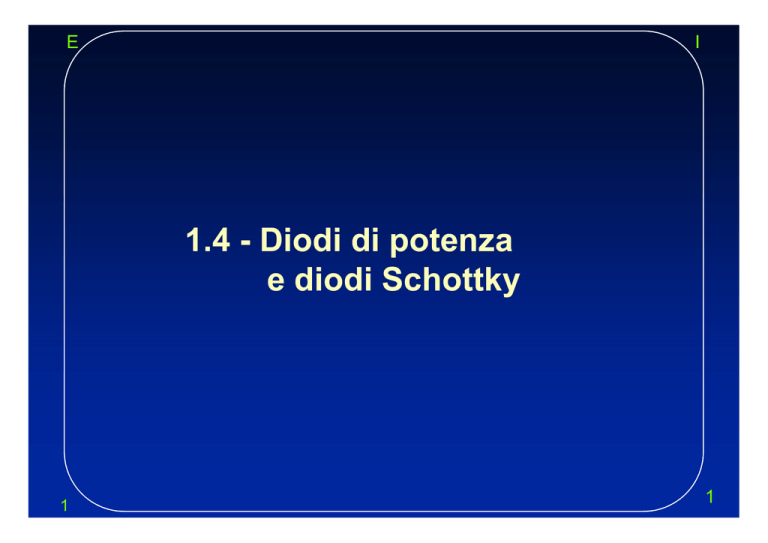

Simbolo e caratteristica statica

Anodo

i

Catodo

A

K

+ vi

BVKA

Resistenza

ohmica

IR

VKN

v

Breakdown

B

kd

a valanga

1

5

E

Diodi di potenza

I

Sezione di un diodo a giunzione pn

La sezione varia secondo la corrente che deve circolare

Lo strato n-, chiamato regione di drift e assente nei diodi di

segnale, è tanto più largo quanto maggiore è la tensione

inversa da sostenere

1

6

E

I

Diodi di potenza: Commutazioni

Circuito di prova per le forme d’onda

e per i tempi di comm

commutazione

ta ione

K

i

+

VR

A

Diodo

in prova

v

+

IL

Diodo

ideale

1

iT

7

E

I

Diodi di potenza: Commutazioni

i

C

Commutazioni

t i i

diR /dt

diF /dt

IL

Q rr=I rr t rr /2

IR

IR

t

I rr

t Rf

t ri

t rd

0.25 I rr

v

t rr

VFp

Von

t

VR

VR

t Fr

1

t Fd

t rdd

S=

t ri

Vrr

8

E

Diodi di potenza: Commutazioni

I

Elementi rilevanti:

• overshoot

h t di tensione

t

i

all turn-on

t

d

dovuta

t all’induttanza

ll’i d tt

del wafer di silicio e delle connessioni; tale overshoot

cresce al crescere della di/dt

• corrente di recovery al turn-off: le cariche in eccesso

nella regione di drift devono essere rimosse prima

che la giunzione possa essere contropolarizzata. Tale

rimozione avviene grazie alla ricombinazione e

all’azione della corrente negativa.

• la tensione rimane quella dello stato on finchè vi sono

portatori in eccesso,, p

p

poi la g

giunzione diventa

contropolarizzata e la tensione sale rapidamente

1

9

E

Diodi di potenza Schottky

I

Anode

p

p

n

Contatti metallici

n+

Cathode

Struttura: viene depositato un film metallico sullo strato ndel semiconduttore,, il film è l’elettrodo positivo

p

e il

semiconduttore è il catodo.

1

Caduta in conduzione diretta ridotta rispetto ai diodi a

giunzione pn.

VKN è tipicamente di 0.3-0.4 V perdite di conduzione

molto ridotte.

10

E

Diodi di potenza Schottky

I

Tempi di commutazione molto ridotti rispetto ai

corrispondenti diodi al silicio di potenza a giunzione

pn perchè non hanno portatori di minoranza che

devono essere iniettati al turn-on ed estratti al turn-off

Overshoot alla commutazione molto ridotti rispetto ai

corrispondenti diodi al silicio di potenza a giunzione

pn perchè non hanno portatori di minoranza che

devono essere iniettati al turn-on ed estratti al turn-off

1

Per contro, la massima tensione inversa di breakdown

BVKA è minore

minore. I limiti massimi dei dispositivi

commerciali non superano 200 V.

11

E

I

Diodi di potenza: Limiti Massimi

Per un diodo di potenza, un esempio di specificazione

dei limiti massimi assoluti può essere:

- Absolute maximum ratings, TC=25 °C (unless

otherwise specified)

Peak repetitive reverse voltage

Working peak reverse voltage

DC blocking voltage

Average rectified forward current

(TC=117 °C)

1

VRRM

VRWM

VR

IF(AV)

1000 V

1000 V

1000 V

30 A

12

E

I

Diodi di potenza: Specifiche

Per un diodo di potenza, come per gli altri dispositivi,

il costruttore specifica tre tipi di dati:

- “limiti massimi assoluti” (“absolute maximum

ratings”)) valori che non devono essere superati

ratings

per non danneggiare il componente.

- “caratteristiche”

ca atte st c e ((“characteristics”)

c a acte st cs ) che

c e

comprendono sia valori minimi e/o massimi, in

ben p

precise condizioni di funzionamento e di

temperatura, che si garantisce non vengano

superati,

p

, sia valori tipici.

p

- “curve tipiche” (“typical performance curves”) che

mostrano l’influenza delle variazioni delle condizioni

di funzionamento sui vari parametri del dispositivo.

1

13

E

I

Diodi di potenza: Limiti Massimi

Repetitive peak surge current

IFSM

60 A

(square wave, 20 kHz)

Nonrepetitive peak surge current IFNRSM 300 A

(halfwaave, 1 phase, 60 hz)

Maximum power dissipation

PD

125 W

Avalanche energy

EAVL 20 mJ

Operating and storage

temperature

TSTG, TJ -65 to +125 °C

1

14

E

I

Diodi di potenza: Caratteristiche

Esempio di specificazione:

caratteristiche garantite

VF at IF =30 A, TC =25 °C

VF at IF =30 A

A, TC =150 °C

C

IR at VR =800 V, TC =25 °C

IR at VR =800 V

V, TC =150 °C

C

trr at IF =1 A, dIF/dt =100 A/μs

RθJC

1

Max

Max

Max

Max

Max

Max

valori indicativi:

trr at IF =30 A, dIF/dt =100 A/μs Typ

tri at IF =30 A,

A dIF/dt =100 A/μs Typ

trd at IF =30 A, dIF/dt =100 A/μs Typ

1.8 V

16V

1.6

500 μA

1 mA

110 ns

1 2 °C

1.2

C /W

150 ns

90 ns

45 ns

15

E

I

CAMPI DI APPLICAZIONE

DEI DISPOSITIVI DI POTENZA

1

16

E

I

PROCESSO DI FABBRICAZIONE

BIPOLARI DI POTENZA

TECNOLOGIA

C O OG PLANARE

1

17

E

I

Substrato N+

X

N+

N+

~ 600 μm

ρ ~ 10 mΩ • cm

1

18

E

I

Crescita epitassiale

p

strati N e NBassa Tensione ~ 100 V

NN

X

N

~ 15 μm

ρ ~ 5 Ω • cm

Alta Tensione ~ 1000 V

N+

X

N-

~ 80 μm

ρ ~ 80 Ω • cm

1

19

E

I

Ossidazione iniziale

SiO2

NN

Xossido ~ 1 μm

N+

1

20

E

I

Fotolitografia

g

Photoresist

NN

Mascheratura

e attacco

N+

1

21

E

I

Formazione anello di bordo

P

N-

impianto ionico P

(boro o alluminio)

N

diffusione in

ambiente ossidante

N+

1

22

E

I

Formazione base

P

P

P+

1

N-

fototecnica base

N

i i t ionico

impianto

i i P+

N+

xj ~ 10 μm

Cs ~ 1018 at/cm

t/ 3

23

E

I

Formazione emettitore

P

P+

1

N-

N++

fototecnica

emettitore

N

i i t ionico

impianto

i i N++

N+

xj ~ 5 μm

Cs ~ 1020 at/cm

t/ 3

24

E

I

Contatti e metallizzazione

AlSi

P

P+

++

N- N

N

Xmetal ~ 3 μm

N+

1

25

E

I

Riduzione spessore

p

e metallizzazione retro

P

P+

++

N- N

N

X ~ 400 μm

N+

metal TiNiAu

1

26

E

I

Sezione di un transistor npn con emettitori e

basi interallaciati

1

27

E

I

BJT: Componente

p

bipolare,

p

, chiamato così perchè

p

la

corrente è determinata sia dal flusso dei portatori di

maggioranza che di minoranza

BJT: Componente controllato in corrente

Power BJT: lo spessore della base dovrebbe essere il

più piccolo possibile per avere buona amplificazione

e più grande possibile per sostenere maggiore

tensione inversa.

Power BJT: realizzati con tanti emettitori e basi

interconnessi p

per ridurre l’effetto di concentrazioni di

corrente localizzate che provocano il breakdown

secondario. Questo layout riduce anche la resistenza

ohmica parassita e quindi la dissipazione.

1

28

E

I

1.5 - Transistori Bipolari

(

(connessione

i

Darlington)

D li t )

1

29

E

I

Transistori Bipolari (BJT) di potenza

Simboli

Collettore

Collettore

C

B

B

Base

Base

E

1

C

E

Emettitore

Emettitore

BJT

npn

BJT

pnp

30

E

I

Transistori Bipolari npn di potenza

in connessione Darlington

Simbolo

Collettore

C

T1

B

D2

Base

D1

T2

E

Emettitore

1

31

E

I

BJT di potenza: Caratteristiche statiche

Caratteristiche statiche (IC, VCE) param. IB

Saturazione

IC

Breakdown

secondario

Breakdown

primario

IB crescente

IB

IB <0

R i

Regione

attiva

i

IB =0

0

0

1

I CEO

BV SUS

BV CEO

BV CBO

V CE

32

E

I

BJT di potenza: Caratteristiche statiche

Caratteristiche statiche (IC, VCE) param. IB

Diagramma espanso nella zona di saturazione

Saturazione

forte (("hard")

hard )

"forte"

Quasi - saturazione

IC

Breakdown

secondario

IB crescente

IB

1/R D

Regione attiva

0

0

1

I CEO

V CE

33

E

I

BJT di potenza: Caratteristiche statiche

Guadagno di corrente β=IC/IB in zona attiva

IC

atan( I C / IB )

IB

β

~

= I C /IB

IC

1

34

E

I

BJT di potenza: Commutazioni

Circuito di prova per le forme d’onda

e per i tempi di comm

commutazione

ta ione

Diodo

ideale

IL

+

E

C

RB

+

vBB

B

E

-

1

35

E

I

BJT di p

potenza: Commutazioni

Commutazioni

I B on

iB

VBE on

t ri

t don

iC

iB

I B off

vBE

vCE

vBE

t fv

t swon

t rv

t sat

E

t fi

t

VBE off

t swoff

vCE

IL

VCE sat

iC

t

1

36

E

I

BJT di potenza: Limiti Massimi Assoluti

Per un BJT di potenza, un esempio di specificazione

d i lilimiti

dei

iti massimi

i i assoluti

l ti può

ò essere:

- Absolute

Ab l t maximum

i

ratings

ti

(TC=25

25 °C)

Collector-emitter voltage

VCEO

C ll t

Collector-emitter

itt voltage

lt

(VBE =-2.5 V)

VCEX

E itt b

Emitter-base

voltage

lt

VEBO

Collector current

IC

C ll t currentt (tp ≤ 5ms)

Collector

5 )

ICM

Base current

IB

B

Base

currentt (tp ≤ 5ms)

5 )

IBM

1

450 V

700 V

7V

30 A

60 A

8A

30 A

37

E

I

BJT di potenza: Limiti Massimi Assoluti

Power dissipation

Ptot

150 W

Junction temperature

Tj -65,+150

-65 +150 W

Insulation voltage (t=1 mn)

Vins

2500 VRMS

Screw torque (mounting terminals)

15 kg ·cm

cm

Junction-case thermal resistance Rth (j-c) 0.83 °C/W

1

38

E

I

BJT di potenza: Caratteristiche

Per un BJT di potenza, un esempio di specificazione

delle caratteristiche garantite e tipiche può essere:

OFF CHARACTERISTICS

BVCEO sus @ Tj=25 °C, IB=0 A,

IC=0.2

0 A,, L=25

5 mH

BVEBO sus @ Tj=25 °C, IC=0 A,

IE=100 mA

ICEX @ Tj=25 °C,, VCE= VCEX,

VBE=-2.5 V

ICEX @ Tj=125 °C,, VCE= VCEX,

VBE=-2.5 V

1

Min

450

50 V

Min

Max

7V

30 V

Max

0.4 mA

Max

4 mA

39

E

BJT di potenza: Caratteristiche

ICER @ Tj=25 °C

C, VCE= VCEX,

RBE=5 Ω

ICER @ Tj=125 °C

C, VCE= VCEX,

RBE=5 Ω

IEBO @ Tj=25 °C

C, IC= 0 A

A,

VBE=-5 V

1

Max

1 mA

Max

8 mA

Max

2 mA

ON CHARACTERISTICS

VCE sat @ Tj=25 °C

C, IC=20 A

A,

IB=4 A, pulsed tp<300μs d<2% Max

VCE sat @ Tj=25 °C

C, IC=30 A

A,

IB=8 A, pulsed tp<300μs d<2% Max

VBE sat @ Tj=25 °C

C, IC=20 A

A,

IB=4 A, pulsed tp<300μs d<2% Max

I

1.5 V

3.5 V

1.6 V

40

E

BJT di potenza: Caratteristiche

DYNAMIC CHARACTERISTICS

fT @ Tj=25 °C, f=1 MHz, IC=1 A,

VCE=10

10 V

T

Typ

C22b @ Tj=25 °C, f=1 MHz,

VCE=10

10 V

T

Typ

5 MH

MHz

SWITCHING CHARACTERISTICS

- Switching times on resistive load

ton @ Tj=25

25 °C,

°C VCC=150

150 V

V, IC=20

20 A

A,

Typ

IB1=- IB2=4 A

M

Max

ts @ Tj=25 °C, VCC=150 V, IC=20 A,

IB1=- IB2=4

4A

T p

Typ

Max

1

0.55 μs

1 μs

I

500 pF

F

1.5

1

5 μss

3 μs

41

E

I

BJT di p

potenza: Caratteristiche

tf @ Tj=25 °C, VCC=150 V, IC=20 A,

IB1== IB2=4 A

Typ

Max

- Switching times on inductive load

ts @ Tj=25 °C, VCC=300 V, VBB=-5 V,

IC=20 A,

A IBend=4 A,

A LB=1.5μΗ

=1 5μΗ Typ

ts @ Tj=100 °C, VCC=300 V, VBB=-5 V,

IC=20 A,

A IBend=4 A,

A LB=1.5μΗ

=1 5μΗ Max

tf @ Tj=25 °C, VCC=300 V, VBB=-5 V,

IC=20 A,

A IBend=4 A,

A LB=1.5μΗ

=1 5μΗ Typ

tf @ Tj=100 °C, VCC=300 V, VBB=-5 V,

IC=20 A,

A IBend=4 A,

A LB=1.5μΗ

=1 5μΗ Max

1

0.3

0

3 μss

0.8 μs

3 5 μs

3.5

5 μs

0 08 μs

0.08

0 4 μs

0.4

42

E

I

1.6 - MOSFET di potenza

1

43

E

I

Struttura del PMOS

Polysilicio

y

Metal

Ossido di Gate

N-

Dielettrico

P

P+

N++

N+

1

44

E

I

Wc

Lc

N1

N+

P

P+

N++

45

E

Struttura 3D del PMOS

N-

P

I

P+ N++

N+

Il source è costituiti da molte aree connesse in parallelo e

circondate dalle regioni di gate.

gate Ciò serve a massimizzare

la larghezza delle regioni di gate e quindi il guadagno.

1

46

E

I

Simulazione 2D di una cella PMOS

1μm

1014

1

1017

at/cm3

1020

47

E

MOSFET di potenza

I

Il gate è isolato dal body da uno strato di ossido,

ossido quindi non

ci può essere iniezione di cariche minoritarie dal gate, e non

quindi p

possibile la circolazione di corrente

sembrerebbe q

drain-source.

1

48

E

MOSFET di potenza

I

Tuttavia, l’applicazione di una tensione che polarizza

positivamente il g

p

gate rispetto

p

al source converte la superficie

p

di silicio sotto l’ossido che isola il gate in uno strato n-, detto

canale, connettendo così il source al drain e consentendo la

circolazione di una corrente significativa.

Per minimizzare il rischio che il transistor parassita si

accenda, la regione del body è cortocircuitata al source

tramite uno strato di metallizazione ((body-source

y

short).

)

Questo strato aumenta la conduttività della regione di drift

f

formando

d un accumulo

l di cariche

i h che

h aiuta

i t a minimizzare

i i i

l

la

resistenza in on; inoltre tende ad aumentare il raggio di

curvatura della regione di svuotamento (depletion layer).

layer)

1

49

E

I

MOSFET di potenza

1

50

E

I

MOSFET di potenza

Simboli

Drain

Drain

D

D

G

G

Gate

Gate

1

S

S

Source

Source

MOSFET

a canale n

MOSFET

a canale p

51

E

I

MOSFET di potenza

Simboli

col diodo integrale messo in e

evidenza

iden a

Drain

Drain

D

G

G

Gate

1

D

Gate

S

S

Source

Source

MOSFET

a canale n

MOSFET

a canale p

52

E

I

MOSFET di p

potenza: Caratteristiche statiche

Caratteristiche statiche (ID, VDS) param. VGS

ID

Regione

ohmica

Regione

attiva

VGS crescente

V GS

interdizione

V GS < V GS th

0

0

1

I DSS

BV DSS

V DS

53

E

I

MOSFET di p

potenza: Caratteristiche statiche

Caratteristica di trasferimento (ID, VSG)

in regione attiva

ID

effettiva

linearizzata

I DSS

0

0

1

V GS th

V GS

54

E

MOSFET di potenza: Applicazioni

I

Caratteristiche dei MOSFET di potenza, usati come

interruttori a conduzione inversa:

Pilotaggio molto semplice;

intrinsecamente più veloci degli altri dispositivi di

potenza

pote

a ma

au

un pò p

più

ù costosi

costos e più

p ù se

sensibili

sb a

alle

e

sovratensioni.

Cadute in conduzione maggiori,

maggiori specie con

dispositivi per alte tensioni.

Limiti di correnti e tensioni

da pochi Ampere fino a 100 A

da poche decine di Volt fino a circa 1500 V.

1

55

E

I

MOSFET di potenza: Commutazioni

Circuito di prova per le forme d’onda

e per i tempi di comm

commutazione

ta ione

Diodo

ideale

IL

+

E

D

RG

+

vGG

G

S

-

1

56

E

MOSFET di potenza: Commutazioni

Capacità Equivalenti

Drain

D

CGD

Gate

G

C DS

CGS

I

I mosfet di potenza sono

intrinsecamente più veloci dei

dispositivi bipolari perchè non

hanno portatori minoritari in

eccesso che devono essere

rimossi alle commutazioni. Le

uniche

i h cariche

i h iin gioco

i

sono

quelle relative alle capacità

parassite

parassite.

S

Source

MOSFET

a canale n

1

La capacità drain-source

influenza limitatamente le

commutazioni.

57

E

I

MOSFET di p

potenza: Commutazioni

Capacità Equivalenti

1

58

E

I

MOSFET di potenza: Commutazioni

Capacità Equivalenti

1

Le capacità variano, però Cgs può essere assunta costante

in prima approssimazione. Le variazioni di Cggd invece sono

maggiori; si possono però assumere i due valori discreti

indicati in figura.

59

E

I

MOSFET di p

potenza: Commutazioni

Commutazioni

vGG

vGS (I L )

vGS th

vGS

vGS

iG

vGG

t don

t ri

t fv

t swoff

t swon

vDS

iD

1

t

iG

t rv t fi

E

vDS

t doff

iD

VDS on

IL

iD

t

60

E

1

MOSFET di potenza: Commutazioni

I

Nella fase flat, l’intera corrente iG scorre nella capacità CGD e

la tensione VGS resta al valore necessario per mantenere la

corrente iD. Quando VDS raggiunge il valore “on”,la VGS

riprende la sua crescita esponenziale.

61

E

I

MOSFET di p

potenza: Commutazioni

Commutazioni

1

62

E

I

MOSFET di potenza: Specifiche

Anche per i MOSFET di potenza si specificano tre

tipi di dati: limiti massimi assoluti (absolute

maximum ratings), caratteristiche

(characteristics), curve tipiche (typical

performance

f

curves)) (si

( vedano le definizioni

f

date

trattando dei diodi di potenza).

1

63

E

I

MOSFET di potenza: Limiti Massimi

Per un MOSFET di potenza, un esempio di

specificazione dei limiti massimi assoluti può

essere:

- Absolute maximum ratings

Continuous Drain Current

(VGS=10 V, TC=25 °C)

Continuous Drain Current

(VGS=10 V, TC=100 °C)

Pulsed Drain Current

(repetitive rating) (1)

1

ID

16 A

ID

10 A

IDM

64 A

64

E

I

MOSFET di potenza: Limiti Massimi

Power Dissipation (TC=25 °C)

PD25 280 W

Linear Derating Factor

DF

2.2 W / °C

Gate to Source Voltage

VGS

± 20 V

Single Pulse Avalanche Energy(2)EAS

1000 mJ

Avalanche Current (1)

IAR

16 A

Repetitive Avalanche Energy (1) EAR

28 mJ

Peak Diode Recovery dv/dt (3) dv/dt 3.0 V/ns

Operating Junction and Storage

Temperature Range

TJ, TSTG -55/+150 °C

Soldering Temperature (for 10 s,

1.6 mm from case)

300 °C

Mounting Torque (6-32 or M3 screw)

1.1 Nm

1

65

E

I

MOSFET di potenza: Caratteristiche

Per un MOSFET di potenza, un esempio di

specificazione delle caratteristiche garantite e

tipiche può essere:

- Thermal resistance

RθJC Junction to Case

Max 0.45

0 45 °C

C /W

RθCS Case to Sink, Flat, Greased

Surface

Typ 0

0.24

24 °C

C /W

RθJA Junction to Ambient

Max 40 °C /W

1

- Electrical characteristics @ TC=25 °C (unless

otherwise specified)

BVDSS @ VGS=0V, ID =250 μA

Min. 600 V

66

E

I

MOSFET di potenza: Caratteristiche

ΔBVDSS/ΔΤJ @ TJ=25 °C,ID=1 mA Typ 0.83 V/ °C

RDS(on) @ VGS=10 V

V, ID=9.6

=9 6 A (4) Max 0.40

0 40 Ω

VGS(th) @ VDS=VGS, ID=250 μA

Min/Max 2/4 V

gfs (Forward transconductance)

@ VDS=50 V,ID=9.6 A (4)

Min 13 S

IDSS @ VDS=600 V

V, VGS=0 V

Max 100 μA

A

IDSS @ VDS=480 V,

VGS=0 V

V, TJ=125 °C

C

Max 500 μA

IGSS Gate to Source Forward Leakage

@ VGS=20 V

Max 100 nA

IGSS Gate to Source Reverse Leakage

@ VGS= -20

20 V

Max -100

100 nA

1

67

E

I

MOSFET di potenza: Caratteristiche

QG

QGS

QGD

td(on)

tr

td(off)

tf

LD

LS

1

@ ID=16 A,, VDS=360 V,,

VGS=10 V

@ as above

@ as above

@ E=300 V,, ID=16 A,,

RG=4.5 Ω, RD=18 Ω

@ as above

@ as above

@ as above

Max 210 nC

Max 26 nC

Max 110 nC

Typ 19 ns

Typ

yp 54 ns

Typ 110 ns

Typ

yp 56 ns

Typ 5 nH

Typ

yp 13 nH

68

E

I

MOSFET di potenza: Caratteristiche

CISS @ VGS=0 V,, VDS=25 V,,

f=1 MHz

COSS @ as above

CRSS @ as above

Typ 3900 pF

Typ

yp 440 p

pF

Typ 98 pF

- Source-Drain (Body Diode) Ratings and

Characteristics

IS

Continuous Source Current Max 16 A

ISM Pulsed Source Current

Max 64 A

VSD Diode Forward Voltage @ VGS=0 V,

IS=16 A, TJ=25 °C

Max 1.8 V

1

69

E

I

MOSFET di potenza: Caratteristiche

trr

Qrr

ton

1

Reverse Recovery Time @ IS=16 A,

TJ=25 °C

C, di/dt=100 A/

A/μss

Max 920 ns

Typ 610 ns

Reverse Recovery Charge

@ as above

Max 9.9 μC

Typ 6.6

6 6 μC

Forward Turn-On Time: intrinsic turn-on time

is negligible

negligible, turn on is dominated by LS+LD

70

E

I

1.7 - IGBT

1

71

E

I

Struttura PMOS

S

D

G

G

P+

N-

S

N+

D

1

72

E

I

S

G

Struttura IGBT

D

P+

G

NN+

P++

S

D

La principale differenza rispetto al mosfet è lo strato aggiuntivo

P+ che formail drain dell’IGBT

dell IGBT. Questo forma una giunzione pn

che inietta portatori minoritari nella regione drain del mosfet (N )

1

73

E

I

Mosfet,, transistors e resistori che compongono

p g

lo

schema equivalente

D

p+

n-

p

G

n+

S

1

74

E

I

Struttura IGBT

Questa struttura ha un tiristore parassita, lo strato di

metallizzazione che cortocircuita il body ed il source serve a

minimizzare la probabilità di accensione del tiristore parassita.

1

75

E

Flusso dei portatori

E

G

-

+

+

stato ON VG > VT VCE > 0

+

+

C

-

+

I

+

+

N-

G

P++

C

E

All’accensione avviene quanto descritto per il mosfet nella

zona gate-source, ma in aggiunta vi è un’iniezione di lacune

d ll zona P+ alla

dalla

ll zona N- secondo

d molti

lti percorsii che

h

interessano tutta l’area del semiconduttore.

1

76

E

I

L’IGBT é un dispositivo a conduzione “mista”

Le caratteristiche di uscita sono determinate

d l guadagno

dal

d

d

dell PNP

(bassa resistenza di uscita alle alte tensioni)

Le caratteristiche

L

tt i ti h di iingresso sono analoghe

l h

a quelle dei MOS di potenza

( il t

(pilotaggio

i iin ttensione)

i

)

1

77

E

βPNP =

IC

C IB

=

ICE

IB

IC

Imos

I

ICE = IC + Imos

ICE = Imos (1+βPNP)

Imos

G

IC

E

1

78

E

I

Mosfet,, transistors e resistori che compongono

p g

lo

schema equivalente

1

79

E

I

IGBT (Insulated Gate Bipolar Transistor)

Simboli

Collettore

Collettore

C

G

C

G

Gate

Gate

E

Emettitore

E

Emettitore

Simboli alternativi di

IGBT

a canale n

1

80

E

Buffer layer

I

La regione N+ viene chiamata buffer

layer; essa inietta portatori di carica

nella regione di deriva,

debolmente drogata, aumentandone

la conduttività e migliorando il tempo

di commutazione.

La presenza dello strato N+ altera

la distribuzione del campo elettrico

da triangolare a trapezoidale,

consentendo così un minor

spessore della

d ll regione

i

di d

drift

ift e

quindi minor resistività.

Questo si traduce in minor perdite

i conduzione.

in

d i

1

81

E

IGBT (Insulated Gate Bipolar Transistor)

I

Collettore

Struttura interna equivalente

C

BJT

pnp

MOSFET

Canale n

Gate

G

BJT

npn

Resistenza

di t ib it

distribuita

del body

E

Emettitore

1

La caduta di tensione sulla resistenza del body tende a

polarizzare positivamente la giunzione base emettitore del

transistor parassita npn. Se questo si accende, avviene il

fenomeno chiamato latch-up;

latch p il dispositivo

dispositi o funziona

f n iona come un

n

tiristore e il gate non ha più controllo sulla corrente di drain.

82

E

I

IGBT

Caratteristiche statiche (IC, VCE) param. VGE

IC

VGE crescente

V GE

interdizione

V GE < V GE th

BV CER

0

0

1

I CES

BV CES

V CE

C

83

E

I

IGBT

Caratteristica di trasferimento (ID, VSG)

in regione attiva

IC

effettiva

linearizzata

0

0

1

I CES

V GE th

V GE

84

E

I

IGBT

Miglioramenti della caratteristica di uscita (dati Mitsubishi ’98)

1

85

E

1

IGBT – Trend di sviluppo (dati Mitsubishi ’07)

I

86

E

IGBT – tecnologia planare e trench

Nella tecnologia trench, il canale è verticale, la dispersione della

corrente è minore,

minore la resistività è minore

minore, è possibile realizzare

delle celle più strette

ISPSD ‘06

1

I

87

E

1

IGBT – Trend di sviluppo (dati Mitsubishi ’07)

I

88

E

I

IGBT

Circuito di prova per le forme d’onda

e per i tempi di comm

commutazione

ta ione

Diodo

ideale

IL

+

E

C

RG

+

vGG

G

E

-

1

89

E

I

IGBT

Commutazioni

vGG

+V GG M

vGE

vGE (I L )

vGE th

vGE

iG

vGG

-V GG m

t

t don

t ri

iG

t fv

t rv

t swon

vCE

E

t fi

t doff

iC

iC

iC

t swoff

vCE

IL

I C tail

VCE on

t

1

90

E

IGBT package

I

Modulo

d l

Press pack

1

91

E

I

IGBT: Specifiche

Anche per gli IGBT si specificano tre tipi di dati: limiti

massimi assoluti (absolute maximum ratings),

caratteristiche (characteristics), curve tipiche

(typical performance curves) (si vedano le

definizioni

f

date trattando dei diodi di potenza).

)

1

92

E

IGBT: Dati tecnici

I

Per la spiegazione

p g

dei dati

tecnici vedere il file

APPLYING IGBT

1

93

E

I

1.8 - SCR

1

94

E

I

SCR (Silicon Controlled Rectifier)

Simboli

Anodo

Anodo

A

A

G

G

Gate

Gate

K

K

Catodo

Catodo

Simboli alternativi dell'SCR

1

95

E

I

SCR (Silicon Controlled Rectifier)

Schema interno equivalente

derivato dalla struttura a quattro strati pnpn

Anodo

Anodo

BJT

npn

n

G

G

p

Gate

n

BJT

pnp

n

n

BJT

pnp

p

p

G

Gate

BJT

npn

n

K

Catodo

1

A

p

p

Gate

Anodo

A

A

K

Catodo

K

Catodo

96

E

I

SCR (Silicon Controlled Rectifier)

Schema interno equivalente

derivato dalla struttura a quattro strati pnpn

1

97

E

I

SCR (Silicon Controlled Rectifier)

Caratteristiche statiche (IA, VAK) param. IG

IA

I G >0

I G1

IH

I G2

I G =0

BV RO

0

0

BV FO

1

V AK

98

E

I

SCR (Silicon Controlled Rectifier)

Circuito di prova per illustrare

l’innesco ed il comportamento bistabile

RL

+

IA

E

-

A

G

IG

+

vGK

K

-

1

99

E

I

SCR (Silicon Controlled Rectifier)

Punti di equilibrio con IG = 0

Con IG = 0 vi sono

due punti (P1 e P3)

di equilibrio stabile

ed uno (P2) di

equilibrio instabile

IA

E/R L

Equilibrio

stabile

P1

Equilibrio

E

ilib i

instabile

I G >0

I G1 I G2

IH

P2

I G =0

BV RO

0

0

P3

E

1

BV FO

V AK

100

E

I

SCR (Silicon Controlled Rectifier)

Condizione di interdizione P3 (IG = 0)

Il punto P3

corrisponde alla

INTERDIZIONE

(alta tensione VAK

e piccola

corrente

co

e te IA)

IA

E/R L

Interdizione

(equilibrio

stabile)

I G >0

I G1 I G2

IH

I G =0

BV RO

0

0

P3

E

1

BV FO

V AK

101

E

I

SCR (Silicon Controlled Rectifier)

Innesco (con IG = IG1 > 0)

Per causare

ll’INNESCO

INNESCO

dell’SCR si manda

in gate una

adeguata corrente

IG > 0 (ad es

es. IG1 )

IA

E/R L

Innesco

(equilibrio

stabile con

IG =I G1 >0)

P1

I G >0

I G1 I G2

IH

I G =0

BV RO

0

0

E

1

BV FO

V AK

102

E

I

SCR (Silicon Controlled Rectifier)

Innesco (con IG = IG1 > 0)

In tali condizioni,

l’ i punto

l’unico

t

di equilibrio

possibile

ibil

è P1

IA

E/R L

Innesco

(equilibrio

stabile con

IG =I G1 >0)

P1

I G >0

I G1 I G2

IH

I G =0

BV RO

0

0

E

1

BV FO

V AK

103

E

I

SCR (Silicon Controlled Rectifier)

Condizione di conduzione P1 (IG = 0)

L’SCR rimane in

CONDUZIONE,

in P1 (alta corrente

IA e piccola

tensione VAK)

anche quando si

torna a IG = 0

IA

E/R L

Conduzione

(equilibrio

stabile con

I G = 0)

P1

I G >0

I G1 I G2

IH

I G =0

BV RO

0

0

E

1

BV FO

V AK

104

E

I

SCR (Silicon Controlled Rectifier)

Schema interno equivalente di principio

corrispondente alla struttura distribuita dell’SCR

Anodo

A

BJT

pnp

Gate

G

Rn

Rp

Rn

Rp

BJT

npn

K

Catodo

1

105

E

I

SCR (Silicon Controlled Rectifier)

Circuito di prova per le forme d’onda

e per i tempi di comm

commutazione

ta ione

Diodo ideale

Ld

+

v AA

-

IA

IL

A

G

IG

+

vGK

K

-

1

106

E

I

SCR (Silicon Controlled Rectifier)

Commutazioni

i A ,i G

iA

diF /dt

diR /dt

iG

t don t Fr

vAK , vAA

IL

iG

iA

iA

Q rr=I rr t rr /2

0.25 I rr

t

I rr

t pps

t Rf

t ri

t rd

vAA

vAA

t rr

vAK

VF

Von

d F/dt

dv

vAA

vAK

vAK

t

VR

vAA

vAK

Vrr

VR

vAK

t off

1

107

E

I

1.9 - GTO

1

108

E

I

GTO (Gate Turn Off thyristor)

Simbolo

Anodo

A

G

Gate

K

Catodo

1

109

E

I

GTO (Gate Turn Off thyristor)

Struttura a quattro strati pnpn

Note:

• la struttura altamente interdigitata gate-catodo favorisce il

turn off

turn-off

• i catodi appaiono come isole direttamente a conattto col

metallo

• le regioni n+ dell’anodo facilitano la rimozione delle lacune in

eccesso in n-, riducendo il tempo di storage durante il turn-off

1

110

E

I

GTO (Gate Turn Off thyristor)

Caratteristiche statiche (IA, VAK) param. IG

IA

I G3 <0

I G >0

I G1 I G2

I G =0

IH

BV RO

0

0

BV FO

1

V AK

111

E

I

GTO (Gate Turn Off thyristor)

Punti di equilibrio con IG = 0

Come per l’SCR,

con IG = 0 vi sono

due punti (P1 e P3)

di equilibrio stabile

ed uno (P2) di

equilibrio instabile

IA

E/R L

Equilibrio

stabile

P1

I G3 <0

Equilibrio

instabile

I G >0

I G1 I G2

I G =0

IH

BV RO

P2

0

0

P3

E

1

BV FO

V AK

112

E

I

GTO (Gate Turn Off thyristor)

Condizione di conduzione P1 (IG = 0)

Se il GTO è in

CONDUZIONE,

nel punto di

equilibrio

stabile P1

con IG = 0.....

IA

E/R L

Conduzione

(equilibrio

stabile con

I G = 0)

P1

I G3 <0

I G >0

I G1 I G2

I G =0

IH

BV RO

0

0

E

1

BV FO

V AK

113

E

I

GTO (Gate Turn Off thyristor)

Spegnimento mediante comando IG = IG3 <0

portando IG ad un

valore negativo

g

IG

= IG3 <0, l’unico

punto possibile di

funzionamento è

P4 (interdizione)

IA

E/R L

Interdizione

(equilibrio

stabile)

I G3 <0

I G >0

I G1 I G2

I G =0

IH

BV RO

P4

0

0

E

1

BV FO

V AK

114

E

I

GTO (Gate Turn Off thyristor)

Condizione di interdizione P3 (IG = 0)

Quando si torna

ad IG = 0, il GTO

rimane

INTERDETTO nel

punto di equilibrio

stabile P3

IA

Interdizione

(equilibrio

stabile)

E/R L

I G3 <0

I G >0

I G1 I G2

I G =0

IH

BV RO

0

0

P3

E

1

BV FO

V AK

115

E

I

GTO (Gate Turn Off thyristor)

Schema interno equivalente di principio

corrispondente alla struttura distribuita del GTO

Anodo

A

BJT

pnp

Gate

G

Rp

Rp

Rp

BJT

npn

K

1

Catodo

116

E

I

GTO (Gate Turn Off thyristor)

Circuito di prova per le forme d’onda

e per i tempi di commutazione

Snubber di

accensione

Ls

+

E

-

IL

IA

IG

A

+

VGGP

-

+

VGGN

-

1

G

+

vGK

-

K

Cs

Snubber di

spegnimento

117

E

I

GTO (Gate Turn Off thyristor)

Commutazioni

I GM

iG

vGK

vGK

t swon

IL

t sat t fi t GKbrk

vAK

VAKon

t

vAK

dv

iA

vGK

t tail

iG

E

vAK

iG

vGGN

vGGN

t don

iA

I GBP

AK

dt

i A tail

iA

t

1

118

E

I

1.10 - TRIAC

1

119

E

I

TRIAC (Triode AC thyristor)

Simbolo

Terminale 1

MT 2

G

Gate

MT 1

Terminale 2

1

120

E

I

TRIAC (Triode AC thyristor)

Caratteristiche

C

tt i ti h statiche

t ti h

(IMT2, VMT2MT1) param. IG

I MT2

I G =0

I G > I GT1+

I G < I GT1-

I G =0

I H1

BV O

0

0

I H3

I G =0

BV O

V MT2MT1

I G < I GT3I G > I GT3+

I G =0

0

1

121

E

I

TRIAC ((Triode AC thyristor)

y

)

Circuito di applicazione tipica

in Corrente Alternata con carico Ind

Induttivo-Resistivo

tti o Resisti o

Carico

LL

RL

I MT2

+

v AC

-

MT2

G

IG

CS

+

vGMT1

R SN

C SN

+

VMT2MT1

-

MT1

-

Snubber

1

122

E

TRIAC (Triode AC thyristor)

I

Andamenti

A

d

ti ti

tipici

i i di corrente

t e ttensione

i

con carico Induttivo-Resistivo in CA

vAC

α

i MT2

t

i MT2

vAC

vAC

vMT2MT1

commutazione di

spegnimento

t

vMT2MT1

dv/dt

vAC

oscillazione di

sovratensione

1

123

E

I

TRIAC ((Triode AC thyristor)

y

)

Commutazione allo spegnimento

-di/dt

Von

i MT2

vMT2MT1

t

vMT2MT1

-dv/dt

d /dt

1

124

E

I

1.10 - IGCT

1

125

E

I

IGCT (Integrated Gate Commutated thyristor)

Struttura

St

tt

del

d l GTO

GTO, del

d l

diodo di potenza e

d ll’IGCT

dell’IGCT

1

126

E

I

IGCT (Integrated Gate Commutated thyristor)

Nello

N

ll stato

t t on, un GCT sii comporta

t come un SCR o un GTO

Nello stato off, la giunzione gate-catodo e’ contropolarizzata,

non e

e’ interessata da circolazione di corrente che passa tutta

attraverso il gate.

1

127

E

I

IGCT (Integrated Gate Commutated thyristor)

Il tempo di storage e’ fortemente ridotto

La connessione serie di GCT e’ piu’ facile

L’IGCT puo’’ spegnere alte

lt correntiti anche

h senza snubber

bb

1

128

E

I

GTO structure

IGCT structure

BUFFER

LAYER

Distribuzione

d l campo

del

elettrico

Con l’anodo emettitore sottile,

sottile parte degli elettroni TRANSPAREN

si ricombinano sulla superificie metallica di

T EMITTER

contatto senza generare lacune.

ABB ‘97

97

1

129

E

1

I

130

E

1

I

131

E

Perdite di conduzione

IGCT

1

I

IGBT

132

E

I

Perdite di commutazione

IGCT

1

IGBT

133

E

IGCT: Dati tecnici

I

Per la spiegazione

p g

dei dati

tecnici vedere il file

APPLYING IGCT

1

134

E

I

Evoluzione dei semiconduttori di potenza

• DIODO (1955)

• TIRISTORE, TRIAC (1958)

• BIPOLAR POWER TRANSISTOR (1975)

• GATE TURN OFF THYRISTOR (GTO) (1980)

• POWER MOSFET (1975)

• INSULATED GATE BIPOLAR TRANSISTOR (IGBT) ( 1985)

• INTEGRATED GATE COMMUTATED THYRISTOR (IGCT) (1996)

• SILICON CARBIDE DEVICES

1

135

E

I

Tendenza di sviluppo dei semiconduttori di potenza

1

136

E

1

Settori di applicazione dei semiconduttori di potenza

I

137

E

I

Orientamento e sviluppo dei semiconduttori di potenza

• Graduale obsolescenza dei dispositivi a controllo di fase

(tiristori e triac)

• Dominio dei semiconduttori con controllo di gate isolato

(IGBT, Power Mosfet)

• Graduale obsolescenza dei GTO ((Sostituiti dagli

g IGBT –

potenza inferiore ed IGCT – potenza superiore)

• Riduzione delle cadute di tensione in conduzione nei

power mosfet ed IGBT

• Sviluppo di componenti silicon carbide (bassissima Von)

che causeranno una nuova rivoluzione nel settore

1

138