Elettronica I – Inverter con

transistore MOS

Valentino Liberali

Dipartimento di Tecnologie dell’Informazione

Università di Milano, 26013 Crema

e-mail: [email protected]

http://www.dti.unimi.it/˜liberali

Elettronica I – Inverter con transistore MOS – p. 1

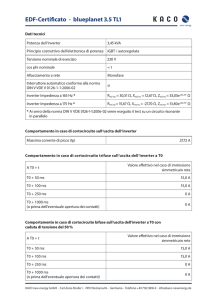

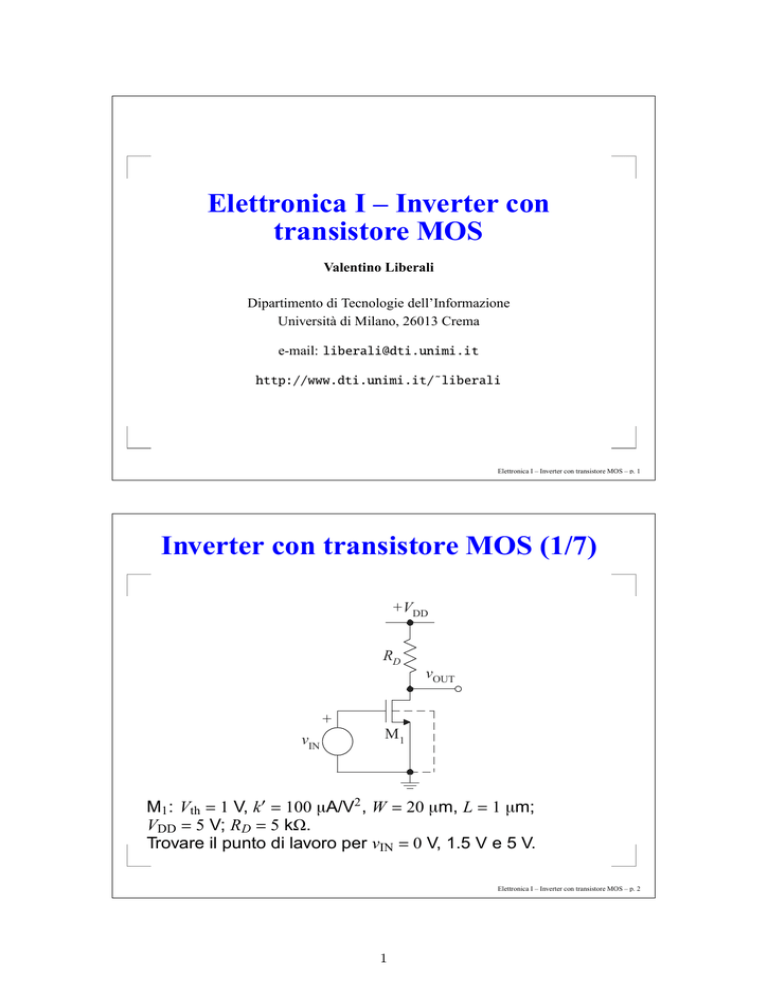

Inverter con transistore MOS (1/7)

+VDD

RD

vOUT

+

vIN

M1

M1 : Vth = 1 V, k′ = 100 µA/V2 , W = 20 µm, L = 1 µm;

VDD = 5 V; RD = 5 kΩ.

Trovare il punto di lavoro per vIN = 0 V, 1.5 V e 5 V.

Elettronica I – Inverter con transistore MOS – p. 2

1

Inverter con transistore MOS (2/7)

• vIN = 0 V

M1 è spento: VGS = 0 < Vth = 1 V. Quindi ID = 0 e nel circuito

non passa corrente; la tensione al drain di M1 è

VD = VDD = 5 V. La tensione di uscita è vOUT = VD = 5 V.

VGD = −5 V < Vth = 1 V; questo conferma che il MOS è

spento.

Elettronica I – Inverter con transistore MOS – p. 3

Inverter con transistore MOS (3/7)

• vIN = 1.5 V

M1 è sicuramente acceso: VGS = 1.5 V > Vth = 1 V. Quindi

M1 può essere in triodo oppure in regione attiva.

Ipotesi: M1 in regione attiva.

ID = K (VGS − Vth )2

è indipendente da VDS

con

1 W

K = k′ = 1 mA/V2

2 L

Risulta ID = 0.25 mA e VD = VDD − RD ID = 3.75 V. La tensione

di uscita è vOUT = VD = 3.75 V.

Verifica dell’ipotesi: VGD = −2.25 V < Vth = 1 V; questo

conferma che il MOS è in regione attiva.

Elettronica I – Inverter con transistore MOS – p. 4

2

Inverter con transistore MOS (4/7)

• vIN = 5 V

M1 è sicuramente acceso: VGS = 5 V > Vth = 1 V. Quindi M1

può essere in triodo oppure in regione attiva.

Ipotesi: M1 in regione attiva.

ID = K (VGS − Vth )2

è indipendente da VDS

con

1 W

K = k′ = 1 mA/V2

2 L

Risulta ID = 16 mA e VD = VDD − RD ID = −75 V. La tensione

di uscita dovrebbe avere il valore vOUT = VD = −75 V, che è

ovviamente impossibile.

Elettronica I – Inverter con transistore MOS – p. 5

Inverter con transistore MOS (5/7)

• vIN = 5 V. Cambiamo l’ipotesi: M1 in regione di triodo.

2

ID = K 2(VGS − Vth ) · VDS − VDS

In questo caso, la corrente dipende anche dalla tensione di

drain VDS = VD (VS = 0).

L’altra equazione è data dalla legge di Ohm per RD :

ID =

VDD − VD

RD

Poiché M1 e RD hanno la stessa corrente ID , si ricava

l’equazione nella sola incognita VD :

VDD − VD

K 2(VGS − Vth ) · VD − VD2 =

RD

Elettronica I – Inverter con transistore MOS – p. 6

3

Inverter con transistore MOS (6/7)

VD2 − VD

!

VDD

1

+

=0

2(VGS − Vth ) +

KRD

KRD

è un’equazione di secondo grado nell’incognita VD : ha due

soluzioni, di cui sicuramente una è da scartare.

Risolvendo, si ottiene VD = 8.08 V e VD = 0.12 V.

Prima soluzione: VD = 8.08 V

Avremmo VGD = −3.08 V < Vth = 1 V; questo

contraddice l’ipotesi che M1 sia in triodo

−→ soluzione da scartare

Seconda soluzione: VD = 0.12 V

Avremmo VGD = 4.88 V > Vth = 1 V; questo conferma

l’ipotesi che M1 sia in triodo

−→ soluzione valida

Elettronica I – Inverter con transistore MOS – p. 7

Inverter con transistore MOS (7/7)

Se i valori di tensione 0 e 5 V corrispondono rispettivamente

ai bit “0” e “1”, possiamo riepilogare il funzionamento del

circuito con la tabella (X = bit di ingresso; Y = bit di uscita)

X

vIN

M1

vOUT

Y

0

0V

spento (“off”)

5V

1

1

5V

in triodo

0.12 V

0

Leggendo la prima e l’ultima colonna, si ricava che il circuito

realizza la funzione di una porta logica NOT (inverter):

X

Y

Elettronica I – Inverter con transistore MOS – p. 8

4

Caratteristica statica ingresso-uscita

La caratteristica statica ingresso-uscita è il grafico che

riporta in ascissa la variabile elettrica di ingresso e in

ordinata la variabile elettrica di uscita, calcolata facendo

un’analisi in continua senza tenere conto delle eventuali

costanti di tempo.

6.0V

4.0V

2.0V

0V

0V

V(V1:+)

1.0V

V(R1:1)

2.0V

3.0V

4.0V

5.0V

V_V1

Elettronica I – Inverter con transistore MOS – p. 9

Livelli logici dell’inverter (1/4)

I punti in cui la caratteristica statica ingresso-uscita ha

pendenza −1 determinano i livelli logici di ingresso e di

uscita.

vout

za

en

nd -1

=

VOH

pe

VDD

za

en

nd -1

=

pe

VOL

VIL

VDD/2 VIH

VDD

vin

Elettronica I – Inverter con transistore MOS – p. 10

5

Livelli logici dell’inverter (2/4)

vout

za

en

nd -1

pe =

VDD

VOH

za

en

nd -1

pe =

VOL

VDD/2 VIH

VIL

VDD

vin

Se il segnale di ingresso è minore di VIL , viene interpretato

come uno 0 logico; se è maggiore di VIH , viene interpretato

come un 1 logico.

Elettronica I – Inverter con transistore MOS – p. 11

Livelli logici dell’inverter (3/4)

vout

za

en

nd -1

=

VOH

pe

VDD

za

en

nd -1

=

pe

VOL

VIL

VDD/2 VIH

VDD

vin

Se il segnale di ingresso è compreso tra VIL e VIH , il valore

logico dell’ingresso non è ben determinato (potrebbe

essere interpretato come 0 o come 1, in modo dipendente

dai parametri dei componenti, dalla temperatura, dalle

fluttuazioni della tensione di alimentazione, . . . ).

Elettronica I – Inverter con transistore MOS – p. 12

6

Livelli logici dell’inverter (4/4)

vout

za

en

nd -1

=

VOH

pe

VDD

za

en

nd -1

=

pe

VOL

VIL

VDD/2 VIH

VDD

vin

Le tensioni VOL e VOH sono i valori estremi che l’uscita può

assumere quando l’ingresso ha un valore logico ben

determinato (0 o 1). Per poter collegare le porte logiche in

cascata, deve essere VOL < VIL e VOH > VIH affinché le

uscite di una porta logica vengano sicuramente interpretate

nel modo corretto dalla porta successiva.

Elettronica I – Inverter con transistore MOS – p. 13

Margini di rumore

vout

za

en

nd -1

=

VOH

pe

VDD

za

en

nd -1

=

pe

VOL

VIL

VDD/2 VIH

VDD

vin

I margini di rumore (NM: Noise Margin) sono:

N MH = VOH − VIH

N ML = VIL − VOL

In pratica, qualunque disturbo di ampiezza inferiore al

margine di rumore non può far cambiare il significato del bit.

Elettronica I – Inverter con transistore MOS – p. 14

7