Reti logiche (1)

Algebra booleana e circuiti combinatori

1

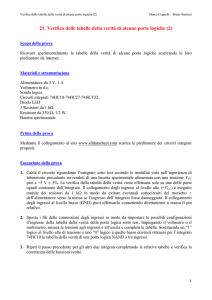

Un quadro della situazione

In particolare gli argomenti qui trattati interessano

ALU (Unità Aritmetico Logica) e CPU

Elementi di memoria e progetto delle gerarchie di memorie

2

1

Piano delle lezioni

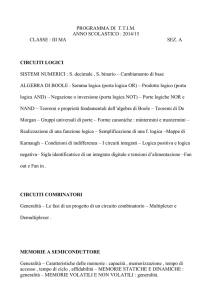

Algebra booleana e porte logiche

Postulati e proprietà, operatori, tabelle di verità …

Porte, insiemi di operatori funzionalmente completi, …

Logica combinatoria e sequenziale

Circuiti combinatori fondamentali, principi di progettazione,…

Temporizzazione, elementi di memoria, register file, RAM, …

Introduzione a gerarchia di memorie

Costruzione di una unità aritmetico-logica

La CPU: Datapath, unità di elaborazione e unità di controllo

Patterson e Hennessy

Appendice B - Reti logiche

Capitolo 7 – Gerarchie di memorie

Capitolo 3 – Unità aritmetico-logica

Capitolo 5 – La CPU

3

Organizzazione della lezione

Algebra di Boole

Tabelle di verità

postulati ed identità

Logica digitale

Operatori e porte logiche

Insiemi di operatori funzionalmente completi

Circuiti combinatori

Decodificatori e Multiplexer

Forme canoniche: “somma di prodotti”, “prodotto di somme”

PLA: Array a Logica Programmabile

ROM: Read Only Memory

Minimizzazione, semplificazione, e condizioni di indifferenza

Patterson e Hennessy, sezioni B.1, B.2, B.3

Tanenbaum, complementi

4

2

Logica digitale

I componenti elettronici nei calcolatori odierni sono digitali

La logica digitale lavora con due livelli di tensione

Tutti gli altri valori di tensione sono temporanei e compaiono solo

come transizioni tra due valori principali

Dal punto di vista logico si parla di segnali

Veri (TRUE), o affermati, pari a 1

Falsi (FALSE), o negati, pari a 0

Il valore 0 è il complemento o l’inverso del valore 1, e viceversa

Tipicamente (logica positiva)

un segnale tra 0 e 1 volt rappresenta uno 0 binario e

un segnale tra 2 e 5 volt rappresenta un 1 binario

Applicato il valore di input

il valore di output appare dopo il tempo di propagazione

5

Circuiti combinatori

Circuito combinatorio

L’output in ogni istante è funzione solo dell’input, non degli

input precedenti o da stato interno (circuito senza memoria)

in generale n input e m output

Può essere specificato da:

tavola di verità: per ognuno delle 2n possibili combinazioni

in input viene specificato il valore degli m output

espressioni booleane: ogni segnale di output viene espresso

come una funzione booleana dei suoi segnali di output

simboli grafici: struttura di interconnessione

Analisi:

dato un circuito comprendere le funzioni realizzate

Progettazione:

data una funzione sviluppare circuito (minimo?) che la realizza

6

3

Tabelle di verità

Ogni riga della tabella di verità specifica il valore di tutte le uscite

in corrispondenza di una combinazione di ingressi

Con n ingressi la tabella di verità contiene 2n righe => la

dimensione cresce velocemente con il numero di ingressi!

Esempio

Funzione logica a 3 ingressi

A, B, C e 3 uscite D, E, F

D è vero se almeno uno degli

ingressi è vero

E è vero se esattamente due

ingressi sono veri

F è vero se tutti e tre gli

ingressi sono veri

23=8 righe

7

Algebra di Boole

George Boole: matematico inglese (1815-1864)

Algebra di Boole definita da un insieme di:

costanti: TRUE e FALSE (rappresentati da 1 e 0)

variabili (con valore TRUE o FALSE): A, B, C,…

operatori:

AND (simbolo ·), operatore binario

OR (simbolo +), operatore binario

NOT (simbolo ¯), operatore unario

Claude Shannon (1938)

ha dimostrato la utilità della algebra di Boole per progettazione ed

analisi di circuiti logici

8

4

Postulati ed identità (1)

Postulati:

regole di base (non dimostrate)

9

Postulati ed identità (2)

Identità:

possono essere derivate dai postulati

Proprietà di

assorbimento

Proprietà di

idempotenza

10

5

Legge di De Morgan

Si può derivare calcolando la tabella di verità per i due membri

dell’identità

11

Esempio

Funzione logica con tre ingressi A, B, C e tre uscite D, E, F

D è vero se almeno uno degli ingressi è vero

D = A + B+ C

F è vero se tutti e tre gli ingressi sono veri

F = A ⋅ B⋅ C

E è vero se esattamente due ingressi sono veri

E = ((A⋅ B) + (A⋅C) + (B⋅C)) ⋅( A⋅ B⋅C)

E = (A⋅ B ⋅C) + (A⋅C ⋅ B) + (B⋅C ⋅ A)

Esercizio (B.7): dimostrare l’equivalenza

12

6

Insiemi di operatori

funzionalmente completi

Un insieme di operatori è funzionalmente completo

se realizza tutte le funzioni realizzabili con AND, OR, NOT

Determinare un insieme funzionalmente completo più piccolo

permette un processo produttivo più semplice

Un operatore si dice universale

Se da solo rappresenta un insieme completo di operatori

AND e NOT sono insieme di operatori funzionalmente completo

Dalla legge di De Morgan: A + B = A ⋅ B

Complementiamo ambo i membri:

A+ B = A ⋅B

Vale l’identità:

A=A

Allora:

A+B= A⋅B

13

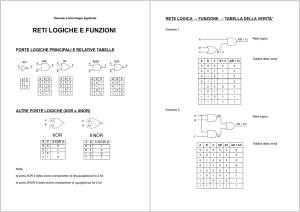

Porte logiche

AND

Notazione: C=A·B

Tabella di verità:

Porta logica:

OR

Notazione: C=A+B

Tabella di verità:

Porta logica:

NOT

Notazione: B = A

Tabella di verità:

Porta logica:

14

7

NOT: rappresentazioni

alternative

Si possono disegnare esplicitamente gli invertitori

Più spesso si aggiunge un pallino in corrispondenza di un

ingresso o di una uscita

Esempio: la funzione

C = A +B

15

Altre porte logiche

NOR

NAND

XOR

Notazione: C = A⋅ B

Notazione: C = A+B

Notazione: C = A ⊕ B

Tabella di verità:

Tabella di verità:

Tabella di verità:

Porta logica:

Porta logica:

Porta logica:

16

8

Implementazione di XOR

Esercizio: dimostrare l’equivalenza

ricavando le tabelle di verità dei due

circuiti

Due porte AND e una

porta OR

Tre porte NAND

17

Livello fisico: Invertitore

Il transistor bipolare

Si chiude (resistenza infinita)

quando l’input Vin è sotto un

valore critico

Si apre (filo) quando Vin è

sopra il valore critico

18

9

Livello fisico: NOR e NAND

NOR: due transistor in parallelo

NAND: due transistor in serie

19

Progettazione di circuiti

Ogni funzione booleana può essere realizzata da una

rete di porte logiche (con diverse alternative)

Passi da seguire:

Scrivere la tavola di verità della funzione da realizzare

Dalla tavola di verità arrivare alla espressione booleana

Dall’espressione booleana progettare la rete

Espressioni booleane utilizzate:

La forma come “somma di prodotti”

La forma come “prodotti di somme”

Obiettivi della progettazione

Economicità: realizzare circuiti che calcolino la stessa funzione

con meno porte logiche (minimizzazione di circuiti)

Semplicità costruttiva : utilizzare il minor numero di porte

diverse nel circuito (standardizzazione del processo produttivo)

20

10

Evoluzione della produzione

(1)

In passato, su ogni circuito integrato andavano poche porte

Chip SSI (Small Scale Integrated)

Tipicamente contenenti da 2 a 6 porte indipendenti

In più alimentazione Vcc e messa a terra GND

La realizzazione di circuiti utilizzava questi circuiti “base”

21

Evoluzione della produzione

(2)

Adesso il processo di produzione permette la realizzazione di

moltissime porte su un singolo circuito

Chip VLSI (Very Large Scale Integrated): più di 100.000 porte

Anche 107 transistor su un singolo chip

Ci starebbero 5•106 porte NAND

Ci vorrebbero 1.5•107 + 2 piedini

Sarebbe un chip lungo alcuni chilometri

Ci vogliono chip general-purpose con elevato rapporto

porte/piedini

22

11

Decodificatore

Circuito combinatorio con n input e 2n output:

una sola delle linee di output viene messa a TRUE

in dipendenza dal valore binario presente in input

La linea messa a TRUE corrisponde al valore binario

associato al vettore degli ingressi

23

Tabella di verità di un

decodificatore

Allora:

Eccetera

D0 = A ⋅ B ⋅ C D1 = A ⋅ B ⋅ C

24

12

Implementazione di un

decodificatore

25

Multiplexer

Circuito combinatorio con n input

di dato, 1 output e log2n input di

controllo:

Permette di selezionare

(tramite linee di controllo) quale

delle linee di input deve andare

in output

Esempio: un multiplexer a 2 vie

A seconda dei valori della linea

di controllo (S) una delle linee

dati (A,B) viene data in output

su C

È necessario un codice di

selezione della linea dati

(tipicamente il valore binario

dell’indice della linea dati)

26

13

Implementazione di un

multiplexer a 2 vie

Scriviamo le tre rappresentazioni (tabella di verità, espressione

booleana, porte logiche)

C = (A⋅ S) + (B⋅ S)

27

Multiplexer a n vie

Per selezionare n segnali in ingresso sono necessari log2 n

segnali di controllo Si

Analogamente al Mux 2 vie (implementazione a due livelli):

Primo livello di porte AND tra gli ingressi e i controlli

Secondo livello con una porta OR a n vie che combina le

uscite da tutti gli AND.

Per ogni possibile combinazione degli Si solo un AND riceverà 1

in input

il valore in uscita dell’AND sarà quello della linea dati

corrispondente, tutti gli altri AND ricevono almeno uno 0

L’OR finale avrà il valore della unica porta AND con 1in input

Applicazione: convertitore parallelo/seriale

Gli 8 bit vanno su 8 ingressi, controlli ciclati tra 000 e 111

28

14

Implementazione di un

multiplexer a n vie

Per n=8 segnali in ingresso

sono necessari log2 8 = 3

segnali di controllo Si

Dato il valore binario dell’indice

della linea dati, il

decodificatore produce 1 sul

corrispondente AND, tutti gli

altri AND ricevono 0

Il valore in uscita dell’AND sarà

quello della linea dati

corrispondente

L’OR finale avrà il valore della

unica porta AND “aperta”

29

Matrici di elementi logici

Molte operazioni

combinatorie realizzate su

dati devono elaborare

parole (32 bit).

Si costruisce una matrice di

elementi logici: una data

operazione è applicata ad

un intero insieme di

ingressi (bus)

Esempio: un multiplexer a 2

vie e ampiezza 32 bit è in

realtà una matrice di 32

multiplexer a 2 vie e

ampiezza 1 bit

30

15

Forma canonica “Somma di

prodotti” (SDP)

Sia data la tabella di verità.

Si può ricavare una espressione booleana

elencando le combinazioni dei valori di A,B

e C per cui il valore di F è 1

Forma “somma di prodotti”

Si elencano (in AND) le occorrenze delle

variabili in input che danno F=1

Questi vengono talvolta detti minterm o

mintermini

Si uniscono i minterm in un OR

Risultato:

F = ABC + ABC + ABC

31

Esempio

E è vero se esattamente due

ingressi sono veri

E = ((A⋅B) +(A⋅C) +(B⋅C)) ⋅( A⋅B⋅C)

E =(A⋅B⋅C) +(A⋅C⋅B) +(B⋅C⋅ A)

La seconda espressione è una somma di prodotti

32

16

Forma canonica “Prodotto di

somme” (PDS)

Si può ricavare una espressione booleana

elencando le combinazioni dei valori di

A,B, e C per cui il valore di F è 0

Forma “prodotto di somme”

L’idea: basta la occorrenza di uno di

questi input per rendere F=0

si elencano (in OR) le occorrenze delle

variabili in input che danno F=0

Le variabili vanno complementate

le si unisce in un AND

Risultato:

F = (A + B + C)⋅ (A + B + C ) ⋅

( A + B + C)⋅ ( A + B + C ) ⋅ ( A + B + C )

33

Alcuni commenti

In generale la forma SDP è più usata della forma PDS

Il multiplexer di prima è stato rappresentato in forma SDP

Un criterio per scegliere se rappresentare una tabella di verità

funzione) come somma di prodotti oppure come prodotto di

somme dipende dal numero di zeri ed uni della funzione

Se ci sono meno uni: somma di prodotti

Se ci sono meno zeri: prodotto di somme

E’ possibile avere forme più compatte delle forme SDP o PDS

Minimizzazione: implementazione di una funzione logica

usando un numero più piccolo di porte

Ci sono anche altri criteri da tenere presente

Semplificazione: implementazione di una funzione logica

usando una sola porta (NAND o NOR)

34

17

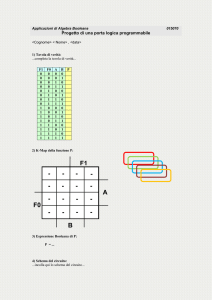

Programmable Logic Array

(PLA)

Approccio generale all’implementazione di funzioni logiche

sfruttando la rappresentazione a due livelli SDP

Ogni input del chip disponibile in forma vera e complementata

Primo livello

Ogni input può essere collegato a qualsiasi porta AND

Secondo livello

L’output di qualsiasi porta AND è collegabile a qualsiasi porta

OR

Realizzazione di un circuito ad hoc

durante la fabbricazione del chip

fusibili (che possono essere bruciati) su “intersezioni” di linea

35

PLA: rappresentazione e

implementazione

PLA con 12 input, 50 prodotti, 6 somme

36

18

Esempio (il solito)

Funzione logica con tre ingressi A, B, C e tre uscite D, E, F

D è vero se almeno uno degli ingressi è vero

F è vero se tutti e tre gli ingressi sono veri

E è vero se esattamente due ingressi sono veri

37

Read Only Memory (ROM)

Altro approccio generale all’implementazione di funzioni logiche

I circuiti combinatori sono “senza memoria”

l’output dipende esclusivamente dagli input applicati

Una Memoria a sola lettura (Read Only Memory)

memoria immagazzinata permanentemente

dato un input (indirizzo della ROM) l’output è sempre lo stesso

(dato corrispondente all’indirizzo)

Per progettare una ROM serve tavola di verità che, per ogni

indirizzo (input) definisce valore di output (parola memorizzata nella

ROM)

Altezza: numero di elementi indirizzabili

Con n ingressi l’altezza è 2n

Ampiezza: numero di bit di ogni elemento indirizzabile

Con m uscite l’ampiezza è m

Queste due dimensioni definiscono la forma di una ROM

38

19

Progettazione di una ROM

39

Commenti su PLA e ROM

Nella sintesi con ROM sono fisicamente rappresentati tutti i 2n

termini prodotto che si possono costruire con n variabili di

ingresso

Nella sintesi con PLA intervengono solo i termini prodotto che che

sono effettivamente presenti nella espressione della funzione da

realizzare

In altre parole

I dispositivi ROM sono completamente decodificati

I dispositivi PLA sono parzialmente decodificati

I dispositivi PLA sono più efficienti

I dispositivi ROM sono meno efficienti (la dimensione cresce

esponenzialmente con il numero di ingressi), ma di contenuto più

facilmente modificabile

40

20

Minimizzazione algebrica

Espressione in forma SDP che abbiamo trovato per l’esempio:

F = ABC + ABC + ABC

Dalle proprietà dell’algebra di Boole segue

F = ABC + ABC + ABC + ABC

Dalla proprietà distributiva (e commutativa):

F = AB⋅(C +C) +BC⋅(A+ A)

Allora

F = AB + BC = B( A+C)

41

Semplificazione (NAND)

algebrica

Data la espressione:

F = B( A + C) = AB + BC

vogliamo trovare una espressione equivalente composta solo da

operatori NAND

Applichiamo due volte la complementazione:

F = AB + BC

Applichiamo la legge di De Morgan:

F = AB ⋅ BC

42

21

Condizioni di indifferenza

(don’t care)

In fase di implementazione nascono spesso situazioni in cui è

indifferente il valore di qualche uscita

qualche altra uscita ha assunto un valore particolare

viene usato un sottoinsieme delle combinazioni di ingresso

Indifferenza in uscita (output don’t care)

Uscita indifferente per un dato ingresso

Si indica con una X nella casella corrispondente

Il progettista può scegliere il valore

Indifferenza in ingresso (input don’t care)

L’uscita dipende solo da alcuni ingressi

Si indica con una X nella casella corrispondente

Importanti applicazioni in tecniche di minimizzazione di circuiti

Karnaugh …

QuineMacCluskey …

43

Esempio

Funzione logica con tre

ingressi A,B,C, e tre uscite

D,E,F, così definita:

Se A o C sono veri allora D è

vero, indipendentemente da

B

Se A o B sono veri allora E è

vero, indipendentemente da

C

F è vero se esattamente un

ingresso è vero, ma non

interessa il valore di F se sia

D che E sono veri

Indifferenza in uscita

44

22

Esempio (continua)

Indifferenza in ingresso

45

Parole chiave

Algebra booleana

Circuiti combinatori

Tabelle di verità

Leggi di De Morgan

Operatori e porte logiche: AND, OR, NOT, NAND, NOR, XOR

Insiemi di operatori funzionalmente completi e Porte universali

Decodificatore e Multiplexer

Logica a due livelli: Somma di prodotti e prodotto di somme

PLA – Programmable Logic Array

ROM – Read only memory

Minimizzazione e semplificazione

Condizioni di indifferenza (in ingresso e uscita)

46

23

Esercizi

(Esercizio B.3) Dimostrare che NAND (da solo!) è un insieme

di operatori funzionalmente completo (altrimenti detto operatore

universale)

(Esercizio B.4) Dimostrare che NOR (da solo!) è un operatore

universale

Dimostrare la proprietà associativa per AND e OR

(Esercizio B.8) Dimostrare che le espressioni per la funzione

E in forma "somma di prodotti" e "prodotto di somme“ sono

equivalenti (sul libro paragrafo B.3 a pag. 750)

(Esercizio B.13) Calcolare la tabella di verità di un multiplexer

a due vie (ingressi A,B,S, uscita C) usando le condizioni di

indifferenza per semplificare la tabella

47

24