PORTE LOGICHE

Si dice circuito logico un circuito elettrico in grado di realizzare elettricamente una espressione

logica. Un circuito si dice combinatorio quando l'uscita dipende dalla combinazione degli ingessi

in quell'istante seconda una opportuna legge. Le porte logiche fondamentali sono OR AND NOT

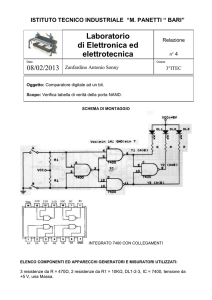

PORTA LOGICA OR

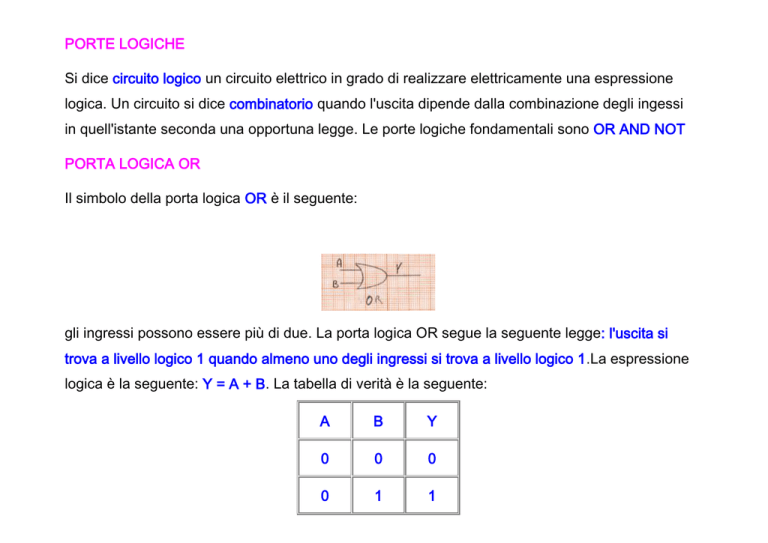

Il simbolo della porta logica OR è il seguente:

gli ingressi possono essere più di due. La porta logica OR segue la seguente legge: l'uscita si

trova a livello logico 1 quando almeno uno degli ingressi si trova a livello logico 1.La espressione

logica è la seguente: Y = A + B. La tabella di verità è la seguente:

A

B

Y

0

0

0

0

1

1

1

0

1

1

1

1

ricordiamo che si dice tabella di verità una tabella che indica per tutte le combinazioni possibili

degli ingressi quello che deve essere il valore dell'uscita. Nel nostro caso Y rappresenta l'uscita.

PORTA LOGICA AND

Il simbolo della porta logica AND è il seguente:

gli ingressi possono essere più di due. La porta logica AND segue la seguente legge: l'uscita si

trova a livello logico 1 quando tutti gli ingressi si trovano a livello logico 1. La espressione logica

è la seguente: Y = A x B. La tabella di verità è la seguente:

A

B

Y

0

0

0

0

1

0

1

0

0

1

1

1

PORTA LOGICA NOT

Il simbolo della porta logica NOT è il seguente:

L'ingresso è uno solo. La porta logica NOT segue la seguente legge: l'uscita si trova a un livello

logico opposto a quello dell'ingresso. Cioè se l'ingresso è 0 l'uscita è 1 e viceversa. La

espressione logica è la seguente: Y = A cioè A negato. La tabella di verità è la seguente:

EQUAZIONI LOGICHE E CIRCUITI

A

Y

0

1

1

0

Un modo per passare da una equazione logica al rispettivo circuito con le porte logiche è quello

di sostituire il segno + con una porta logica di tipo OR ed il segno x con una porta logica di tipo

AND. Data la seguente equazione

Y = A x B + C x ( D + A)

Si parte disegnando sulla destra una porta OR a due ingressi:

sull'ingresso superiore si applica l'uscita di una AND i cui ingressi sono A e B, naturalmente

occorre un NOT per realizzare A:

sul secondo ingresso della OR finale occorre portare l'uscita di una AND i cui ingressi saranno C

e l'uscita di una OR avente come ingressi D e A. Il circuito completo diventa:

RISOLUZIONE DI PROBLEMI

Per risolvere un generico problema di tipo logico occorre individuare dapprima tutte la variabili da

cui dipende la soluzione e porle in corrispondenza con una lettera dell'alfabeto A,B,C.

Successivamente occorre costruire una tabella di verità in cui per tutte le combinazioni delle

variabili di ingresso l'uscita deve avere valore 0 oppure 1, che sia logica secondo il tipo di

problema proposto.

Esempio

Consideriamo un distributore automatico di benzina che dia il consenso all'accensione della

pompa, quando si raggiunge l'importo di £ 10.000, sia con una banconota da 10.000 che con due

banconote da 5.000.

Soluzione

Si assegna all'ingresso A il valore 0 se la banconota da 10.000 non è stata inserita; il valore 1 se

la banconota da 10.000 è stata inserita. Si assegna alla variabile B il valore 0 se la banconota da

5.000 non è stata inserita, il valore 1 se la banconota da 5.000 è stata inserita. Si assegna alla

variabile C il valore 0 se la banconota da 5.000 non è stata inserita, il valore 1 se la banconota

da 5.000 è stata inserita. La tabella di verità sarà la seguente:

A

B

C

Y

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

1

Analizzando la tabella di verità guardiamo la colonna della uscita Y, tralasciamo i primi 3 valori

in cui l'uscita è 0 e vediamo i successivi in cui l'uscita è 1 e scriviamo l'equazione come somma

di prodotti:

Y = ABC +ABC +ABC+ABC+ABC

Possiamo notare che se la variabile di ingresso ha il valore 1 non si fa la negazione, se invece

assume il valore 0 occorre fare la negazione. Per realizzare tale circuito è necessaria una OR a

5 ingressi su ognuno dei quali viene applicata una AND a tre ingressi con gli eventuali NOT,

come spiegato in precedenza. Diciamo che vi sono particolari procedimenti di semplificazione

dell'equazione, che trascuriamo. Tuttavia dato il nostro particolare problema da risolvere, se

trascuriamo il problema del resto per le eventuali banconote versate in più, possiamo dire,

guardando la riga 5 e 6 della tabella che dicono che il consenso può essere dato quando sono

state introdotte le due banconote da 5.000, oppure guadando le ultime quattro righe che ci

indicano che è sufficiente una banconota da 10.000 indipendentemente dal fatto che il cliente ha

versato in eccedenza banconote da 5.000, l'equazione può essere ridotta alla seguente:

Y = A + BC

E quindi il circuito diventa il seguente:

PORTE LOGICHE NOR E NAND

Le seguenti porte NOR e NAND sono la negazione delle rispettive porte OR e AND.

PORTA LOGICA NOR

Il simbolo della porta logica NOR è il seguente:

gli ingressi possono essere più di due. La porta logica NOR segue la seguente legge: l'uscita si

trova a livello logico 0 quando almeno uno degli ingressi si trova a livello logico 1.La espressione

logica è la seguente: Y = A + B. La tabella di verità è la seguente:

A

B

Y

0

0

1

0

1

0

1

0

0

1

1

0

PORTA LOGICA NAND

Il simbolo della porta logica NAND è il seguente:

gli ingressi possono essere più di due. La porta logica NAND segue la seguente legge: l'uscita si

trova a livello logico 0 solo quando tutti gli ingressi si trovano a livello logico 1. La espressione

logica è la seguente: Y = A x B. La tabella di verità è la seguente:

A

B

Y

0

0

1

0

1

1

1

0

1

1

1

0

PARAMETRI CARATTERISTICI

I circuiti integrati delle porte logiche, di cui vediamo un esemplare nella seguente immagine:

appartengono a due famiglie fondamentali:

TTL, che è realizzata con transistor BJT

CMOS, che è realizzata con transistor CMOS

TENSIONE DI ALIMENTAZIONE

La famiglia TTL ha una tensione di alimentazione di 5 V; invece la famiglia CMOS ha tensione di

alimentazione variabile tra 5 V e 15 V

RITARDO DI PROPAGAZIONE

Le porte logiche hanno un certo ritardo tra l'istante in cui viene applicato il segnale in ingresso e

l'istante in cui l'uscita si adegua allo stato degli ingressi. Maggiore è il tempo di ritardo minore è

la frequenza di lavoro delle porte logiche.