Il Timer NE555

Il 555 è un circuito integrato progettato allo scopo di fornire impulsi di durata prestabilita, è in

pratica un temporizzatore che può funzionare anche come timer con duty cycle variabile. La

massima frequenza a cui il 555 può oscillare come astabile, con buona stabilità nei confronti

della temperatura, è di circa 500 KHz, anche se in alcune applicazioni si può raggiungere

qualche MHz.

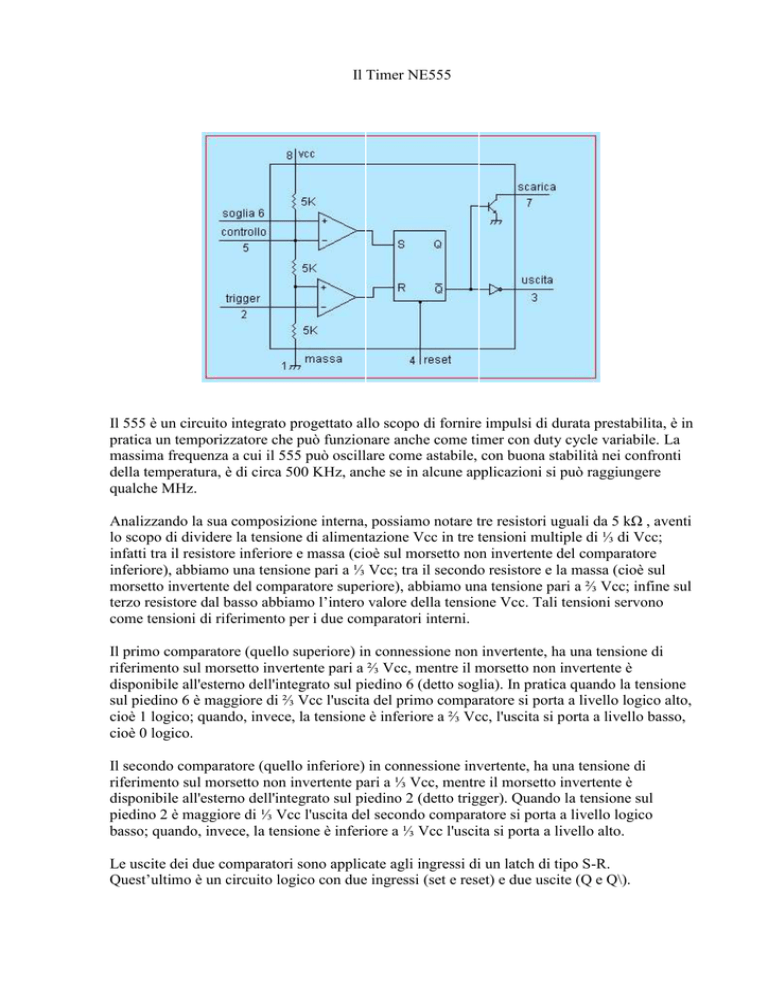

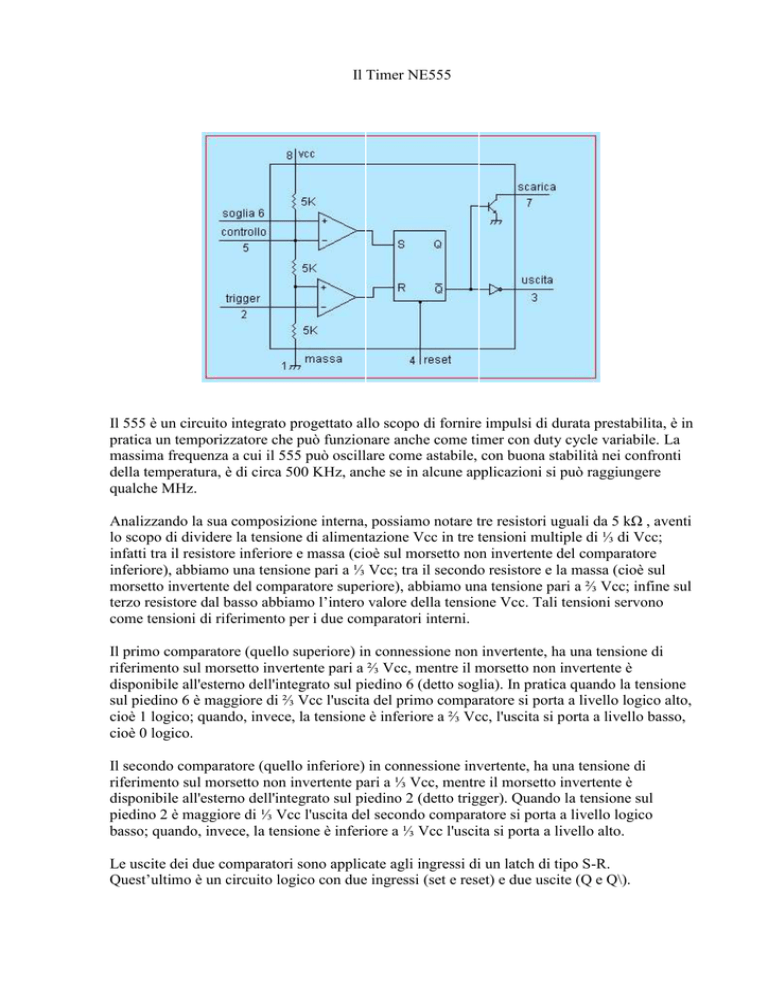

Analizzando la sua composizione interna, possiamo notare tre resistori uguali da 5 kΩ , aventi

lo scopo di dividere la tensione di alimentazione Vcc in tre tensioni multiple di ⅓ di Vcc;

infatti tra il resistore inferiore e massa (cioè sul morsetto non invertente del comparatore

inferiore), abbiamo una tensione pari a ⅓ Vcc; tra il secondo resistore e la massa (cioè sul

morsetto invertente del comparatore superiore), abbiamo una tensione pari a ⅔ Vcc; infine sul

terzo resistore dal basso abbiamo l’intero valore della tensione Vcc. Tali tensioni servono

come tensioni di riferimento per i due comparatori interni.

Il primo comparatore (quello superiore) in connessione non invertente, ha una tensione di

riferimento sul morsetto invertente pari a ⅔ Vcc, mentre il morsetto non invertente è

disponibile all'esterno dell'integrato sul piedino 6 (detto soglia). In pratica quando la tensione

sul piedino 6 è maggiore di ⅔ Vcc l'uscita del primo comparatore si porta a livello logico alto,

cioè 1 logico; quando, invece, la tensione è inferiore a ⅔ Vcc, l'uscita si porta a livello basso,

cioè 0 logico.

Il secondo comparatore (quello inferiore) in connessione invertente, ha una tensione di

riferimento sul morsetto non invertente pari a ⅓ Vcc, mentre il morsetto invertente è

disponibile all'esterno dell'integrato sul piedino 2 (detto trigger). Quando la tensione sul

piedino 2 è maggiore di ⅓ Vcc l'uscita del secondo comparatore si porta a livello logico

basso; quando, invece, la tensione è inferiore a ⅓ Vcc l'uscita si porta a livello alto.

Le uscite dei due comparatori sono applicate agli ingressi di un latch di tipo S-R.

Quest’ultimo è un circuito logico con due ingressi (set e reset) e due uscite (Q e Q\).

Nel timer 555, l'uscita Q non viene utilizzata, ma viene usata solo l'uscita Q\; su di essa è

applicato un invertitore (una porta logica NOT), che trasforma l'uscita Q\ in uscita Q.

Il timer 555 può essere utilizzato sia come multivibratore astabile, che come bistabile.

Le principali caratteristiche elettriche sono le seguenti:

Tensione d’alimentazione: compresa tra 4,5V (min) e 16V (max).

Corrente d’alimentazione massima: 15 mA (nelle condizioni di tensione di alimentazione di

15V e uscita a livello basso)

Tempo di salita tipico dell’uscita: 100 ns

Tempo di discesa tipico dell’uscita: 100 ns

Errori di temporizzazione: l’errore di temporizzazione è contenuto entro il valore tipico

dell’1% del valore teorico; la deriva per variazioni di tensioni d’alimentazione è tipicamente

contenuta entro lo 0,01% / V; la deriva per variazioni di temperatura è tipicamente contenuta

entro 50 ppm/°C

Entrate: ingresso di trigger e soglia (treshold).

Tensione di Treshold: ⅔ Vcc

Corrente di Treshold: 0,1 μA

Tensione di Trigger: ⅓ Vcc

Corrente di Trigger: 0,5 μA

Tensione di reset: 0,7 V (tipica)

Corrente di reset: 0,1 mA (tipica)

Tensione d’uscita tipica a livello alto: 12,5 V (nelle condizioni di tensione d’alimentazione di

15 V e di corrente fornita all’uscita di 200 mA); 3,3 V (nel caso di tensione di alimentazione

di 5 V e di corrente fornita all’uscita di 100 mA).

Tensione d’uscita tipica a livello basso: 2,5 V (nelle condizioni di tensione d’alimentazione di

15 V e di corrente fornita all’uscita di 200 mA); 0,25 V (nel caso di tensione di alimentazione

di 5 V e di corrente fornita all’uscita di 5 mA).

Il terminale di reset (piedino 4) a livello basso (<0,4 V) azzera il timer portando l’uscita a

livello basso e il BJT interno in conduzione.

Il teminale TC (tensione di controllo sul piedino 5) è collegato direttamente al partitore e

viene usato in alcune applicazioni per variare dall’esterno la tensione sul partitore e quindi i

riferimenti dei comparatori. Quando non è usato, non deve essere lasciato fluttuante, bensì

collegato a massa tramite un condensatore da 10 nF il quale, mentre cortocircuita a massa

eventuali disturbi captati dal terminale, isola in continua il partitore dalla massa.

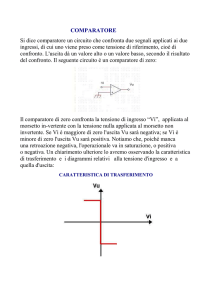

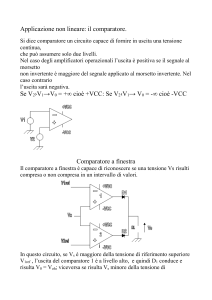

I Comparatori

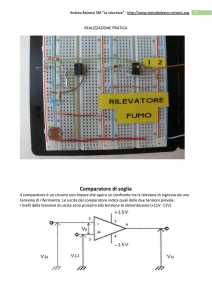

I comparatori sono dispositivi che permettono di confrontare due segnali elettrici sotto forma

di tensione. Generalmente una delle due tensioni (fissa o variabile) in ingresso viene presa

come riferimento e indicata con VR. L’uscita può assumere soltanto due valori che indichiamo

con VOH (uscita alta) e VOL (uscita bassa); per “uscita alta” si intende la saturazione positiva

Vsat+ dell’amplificatore e per “uscita bassa”, la saturazione negativa Vsat-.

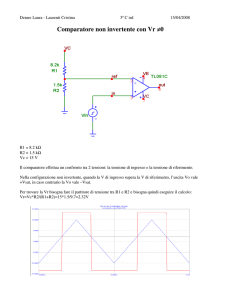

Il comparatore si definisce "invertente" quando il segnale Vin da confrontare con la tensione di

riferimento VR è applicato al morsetto invertente dell’amplificatore operazionale (-); viceversa

si definisce "non invertente" se il segnale Vin è applicato al morsetto non invertente (+).

Comparatore invertente

Comparatore non invertente

Caratteristiche di trasferimento

Comparatore invertente

Comparatore non invertente

Grazie al comparatore, è possibile eliminare gli effetti di indeterminazione causati da valori

di segnali prossimi al riferimento, in quanto il comparatore medesimo dà luogo ad una uscita

che commuta istantaneamente tra due livelli di tensione notevolmente diversi tra loro, poichè

il segnale raggiunge il riferimento.

Comparatore di zero invertente

Comparatore non invertente con Vr = 3V

Comparatore invertente con Vr = -2V

Con il set S=1 e il reset R=0, la porta A presenta uscita Q\ =0 qualsiasi stato sia presente sul

terminale di retroazione; la porta B con R=0 e Q\=0, presenta uscita Q=1, che rispetta la

condizione di disuguaglianza delle uscite.

Con il set S=0 e il reset R=1, la porta B presenta uscita Q=0 qualsiasi stato sia presente sul

terminale di retroazione; la porta A invece, con S=0 e Q=0, presenta uscita Q\=1, che rispetta

con la condizione di disuguaglianza delle uscite.

Agli stati logici S=0 e R=0 degli ingressi corrispondono due situazioni stabili delle uscite che

memorizzano lo stato precedente, infatti:

Quando inizialmente si ha lo stato S=1 e R=0 con uscite Q=1 e Q\=0 e successivamente si

applica lo stato S=0 e R=0, la porta B avendo tutti e due gli ingressi a 0 avrà uscita Q=1,

mentre la porta A avendo uno degli ingressi (Q) allo stato 1, avrà uscita Q\=0.

Quando invece, inizialmente si ha lo stato S=0 e R=1 con uscite Q=0 e Q\=1 e

successivamente si applica lo stato S=0 e R=0, la porta A avendo i due ingressi a 0 avrà uscita

Q\=1, mentre la porta B avendo uno degli ingressi (Q\) allo stato 1, avrà uscita Q=0.

La situazione S=1,R=1 non è lecita. Infatti entrambe le porte, avendo almeno uno dei due

ingressi allo stato 1, dovrebbero avere in uscita lo stato logico 0, ciò è in contraddizione con la

condizione che le due uscite non debbano assumere o stesso stato.Questa condizione perciò

non è ammessa, in quanto conduce ad una situazione di incompatibilità con le caratteristiche

prefissate per il dispositivo. Forzano in ingresso lo stato S=1,R=1, in pratica il dispositivo può

assumere ugualmente in uscita una condizione stabile, che però è un risultato casuale, dovuto

ai parametri interni, e non derivante da una precisa funzione logica. Tale condizione è

comunque inattendibile.

Gli stati assunti dal latch SR a porte NOR possono essere sintetizzati in una tabella in cui si

può notare che la configurazione 0-0 lascia inalterato (e quindi memorizza) lo stato delle

uscite mentre la configurazione 1-1 non è ammessa, in quanto produce stati indeterminati.