REALIZZAZIONE CIRCUITALE DI FUNZIONI LINEARI A TRATTI

Tomaso Poggi, Marco Storace

Università di Genova, Dipartimento di Ingegneria Biofisica ed Elettronica

Via Opera Pia 11A, 16145 Genova

Le funzioni lineari a tratti (PWL) trovano molte applicazioni nella realizzazione di sistemi di controllo

embedded [1], nell'emulazione/approssimazione di sistemi dinamici non lineari (neuroni biologici,

oscillatori, ecc.) [2,3] e in tutti i casi in cui è necessario calcolare funzioni non lineari mediante circuiti

veloci, di dimensioni ridotte e a basso consumo di potenza. In questa ottica, sono state proposte due

architetture digitali in grado di realizzare funzioni PWL definite su domini n-dimensionali [4].

Nonostante l'obiettivo finale sia la realizzazione di un circuito integrato dedicato, per un primo

collaudo le architetture sono state realizzate su una scheda programmabile (FPGA).

Una funzione PWL può essere rappresentata mediante una combinazione lineare di N funzioni base

pesate da coefficienti cj [5]. Mediante un'opportuna scelta delle funzioni base, il calcolo della funzione

viene ricondotto al calcolo di una somma pesata di un numero limitato di coefficienti cj, i quali sono

precalcolati e immagazzinati in una memoria.

Le architetture proposte realizzano lo stesso algoritmo e si differenziano solo per il modo in cui viene

effettuata l'elaborazione dei dati di ingresso. La prima architettura acquisisce gli ingressi un bit alla

volta ed effettua i calcoli utilizzando il minor numero di risorse (moltiplicatori, sommatori, registri)

possibili. La seconda, invece, agisce in parallelo sulle stringhe binarie in ingresso occupando un

maggior numero di celle base della FPGA a vantaggio della maggiore velocità di elaborazione.

Entrambe le realizzazioni su FPGA sono completamente configurabili: fissando alcuni parametri

all'inizio, si realizzano automaticamente funzioni

definite su domini n-dimensionali, con n qualunque

determinate da un qualunque numero di coefficienti cj

calcolabili con precisione arbitraria in termini di numero di bit usati per la rappresentazione

numerica (in virgola fissa)

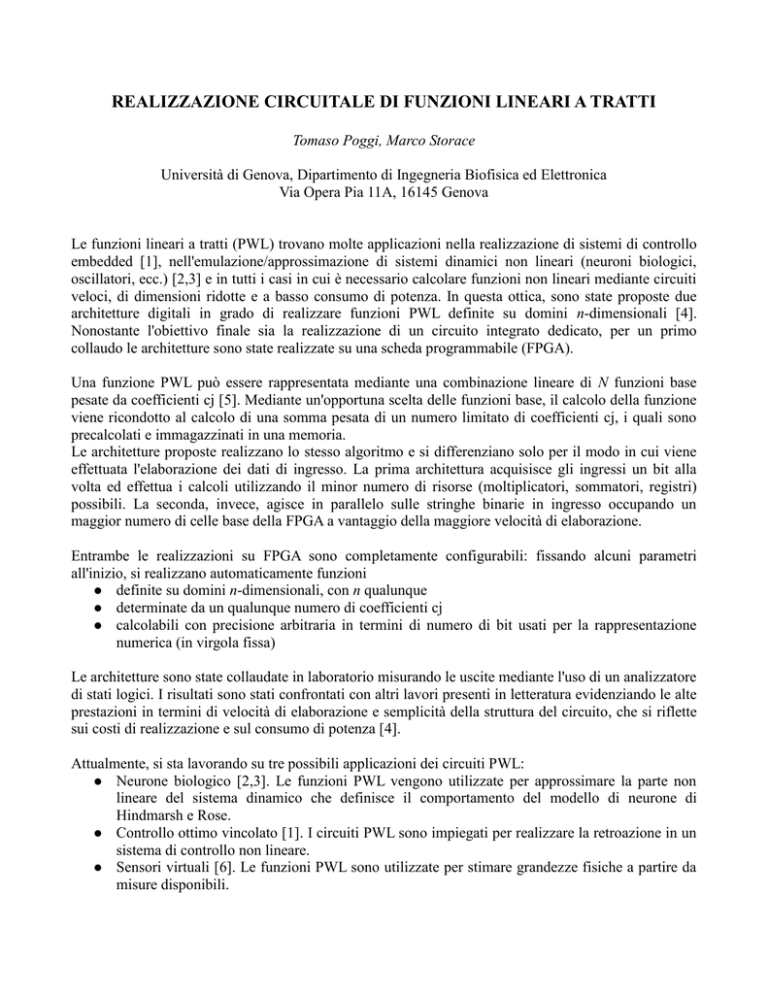

Le architetture sono state collaudate in laboratorio misurando le uscite mediante l'uso di un analizzatore

di stati logici. I risultati sono stati confrontati con altri lavori presenti in letteratura evidenziando le alte

prestazioni in termini di velocità di elaborazione e semplicità della struttura del circuito, che si riflette

sui costi di realizzazione e sul consumo di potenza [4].

Attualmente, si sta lavorando su tre possibili applicazioni dei circuiti PWL:

Neurone biologico [2,3]. Le funzioni PWL vengono utilizzate per approssimare la parte non

lineare del sistema dinamico che definisce il comportamento del modello di neurone di

Hindmarsh e Rose.

Controllo ottimo vincolato [1]. I circuiti PWL sono impiegati per realizzare la retroazione in un

sistema di controllo non lineare.

Sensori virtuali [6]. Le funzioni PWL sono utilizzate per stimare grandezze fisiche a partire da

misure disponibili.

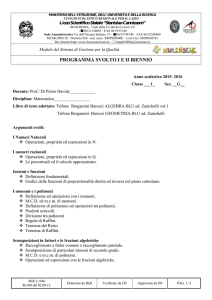

Misure effettuate mediante l'analizzatore di stati logici per l'architettura parallela. Ad ogni fronte di

salita del segnale CK il circuito elabora i tre ingressi per calcolare il valore della funzione PWL.

Riferimenti bibliografici

[1] A. Bemporad, M. Morari, V. Dua and E. Pistikopoulos, “The explicit linear quadratic regulator for

constrained systems”, Automatica, 2002, vol. 38, pagg. 3-30.

[2] M. Storace, F. Bizzarri, "Towards accurate PWL approximations of parameter-dependent nonlinear

dynamical systems with equilibria and limit cycles," IEEE Transactions on Circuits and Systems-I:

Regular Papers, 2007, vol. 54, pagg. 620-631.

[3] M. Storace, D. Linaro, E. de Lange, "The Hindmarsh-Rose neuron model: bifurcation analysis and

piecewise-linear approximations," Chaos, 2008, vol. 18, paper 033128(1-10).

[4] T. Poggi and M. Storace, “FPGA implementation of digital architectures realizing piecewise-linear

multi-variate functions”, accettato per la pubblicazione su International Journal of Circuit Theory

and Applications.

[5] M. Parodi and M. Storace and P. Juliàn, “Synthesis of multiport resistors with piecewise-linear

characteristics: a mixed-signal architecture”, International Journal of Circuit Theory and

Applications, 2005, vol. 33, pagg. 307-319.

[6] M. Milanese, C. Novara, K. Hsu and K. Poolla, “Filter design from data: direct vs. two-step

approaches”, Proceedings of the 2006 American Control Conference, 2006.