UNIVERSITÀ DEGLI STUDI DI PAVIA

DIPARTIMENTO DI ELETTRONICA

via Ferrata, 1 27100 Pavia

Tel.: 0382 - 985.200

Fax: 0382 - 422.583

Corso di Laurea in Ingegneria Elettronica

Elettronica per Telecomunicazioni

14/7/2005

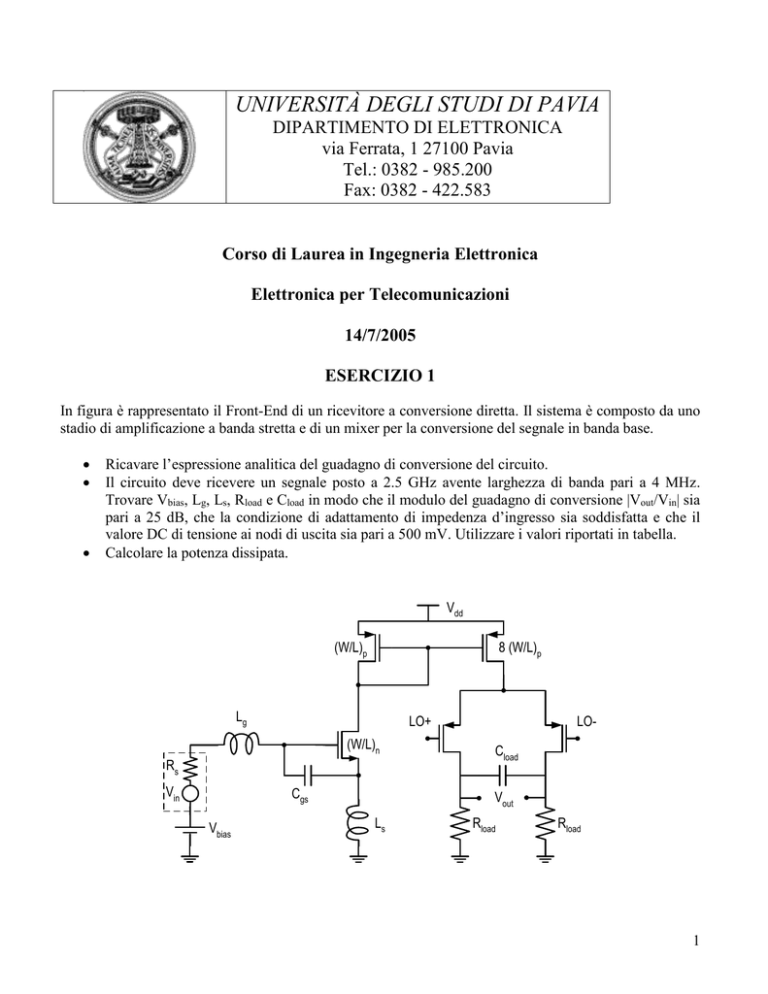

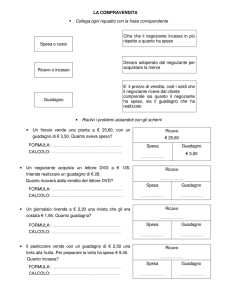

ESERCIZIO 1

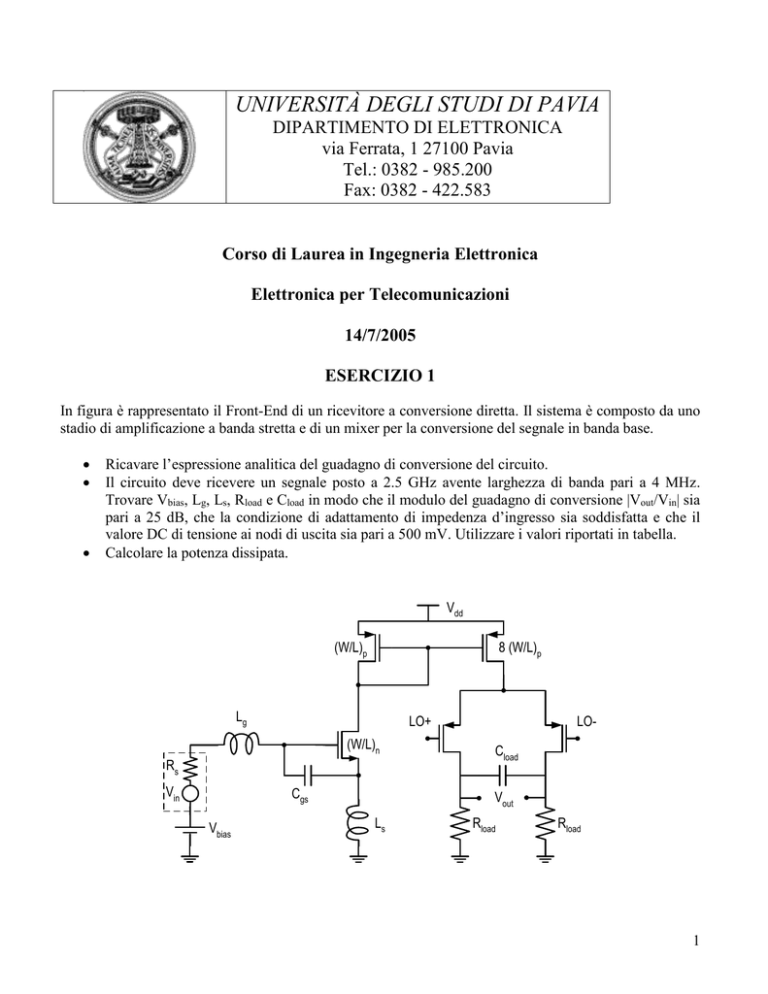

In figura è rappresentato il Front-End di un ricevitore a conversione diretta. Il sistema è composto da uno

stadio di amplificazione a banda stretta e di un mixer per la conversione del segnale in banda base.

Ricavare l’espressione analitica del guadagno di conversione del circuito.

Il circuito deve ricevere un segnale posto a 2.5 GHz avente larghezza di banda pari a 4 MHz.

Trovare Vbias, Lg, Ls, Rload e Cload in modo che il modulo del guadagno di conversione |Vout/Vin| sia

pari a 25 dB, che la condizione di adattamento di impedenza d’ingresso sia soddisfatta e che il

valore DC di tensione ai nodi di uscita sia pari a 500 mV. Utilizzare i valori riportati in tabella.

Calcolare la potenza dissipata.

Vdd

(W/L)p

8 (W/L)p

Lg

LO+

(W/L)n

Rs

Vin

Cgs

Vbias

LOCload

Vout

Ls

Rload

Rload

1

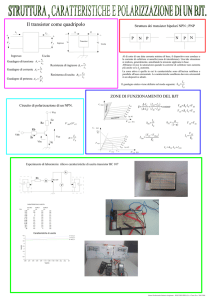

Resistenza di sorgente

Tensione di alimentazione

Capacità rete di ingresso

Tensione di soglia

Rapporto di dimensione

Transconduttanza di processo

RS

Vdd

Cgs

Vth

(W / L)n

nCox

50

1.8 V

250 fF

300 mV

100

240 A/V2

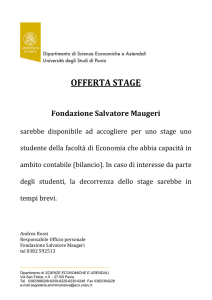

ESERCIZIO 2

Km

KVCO

R

Visin(2pfit+fi)

Vocos(2pfoutt+fo)

C

V2

÷M

Il sistema di figura rappresenta un PLL con filtro RC e comparatore di frequenza analogico

(moltiplicatore) con un divisore di frequenza a modulo fisso (M) nel percorso di feedback.

Dati i seguenti parametri:

frequenza libera del VCO:

guadagno del VCO:

guadagno del moltiplicatore:

ampiezza dei segnali in ingresso al moltiplicatore:

modulo del divisore di frequenza:

resistenza del Filtro:

capacita del Filtro:

fo = 100MHz

Kvco: 10MHz/V

Km = 5

Vi,V2=1V

M =5

R=1 kOhm

C=1nF

determinare:

-

la frequenza di ingresso per cui l’errore di fase a regime è nullo e l’errore di fase se la frequenza di

ingresso si discosta del 10% dal valore calcolato.

Dopo averne spiegato le differenze, calcolare il campo di cattura e il campo di mantenimento per

M=5 ed M=10.

2