Verifica delle tabelle della verità di alcune porte logiche

15. Verifica delle tabelle della verità di alcune porte logiche

Scopo della prova

Ricavare le tabelle della verità di diverse porte logiche.

Materiali e strumentazione

1 Alimentatore da 5 ÷ 15 V, 1 A

1 Voltmetro in d.c.

1 Sonda logica

1 Circuito integrato TTL 74LS00

1 Circuito integrato CMOS 4011

1 Diodo LED

2 Resistori da 1 kΩ

1 Resistore da 330 Ω, 1/2 W

1 Basetta sperimentale

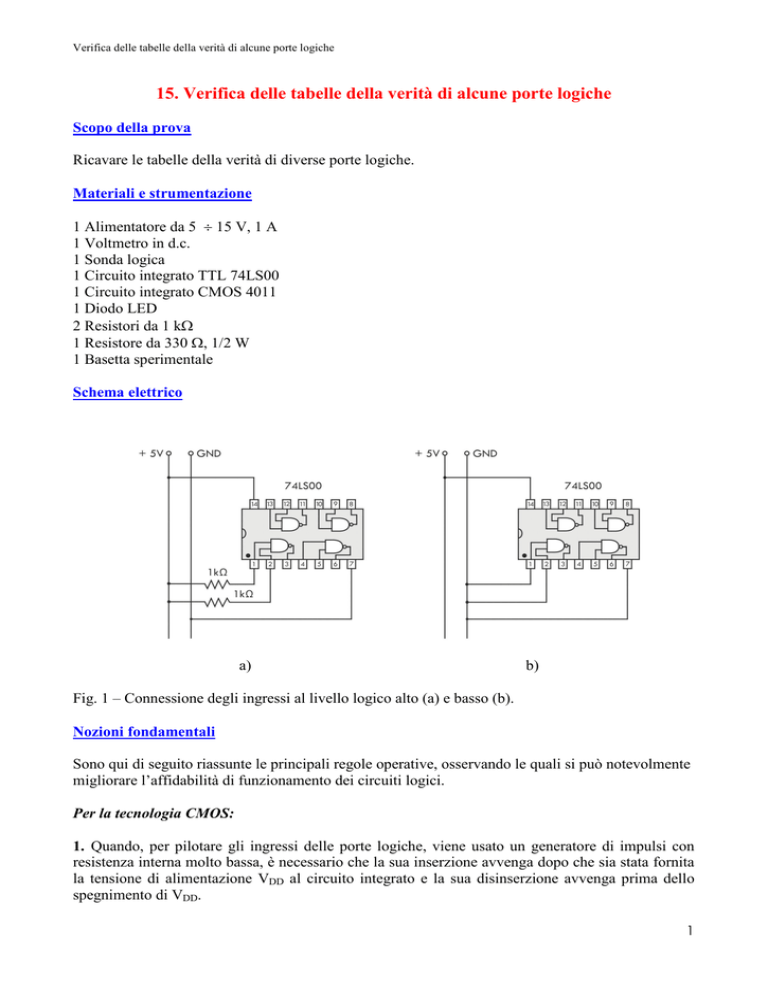

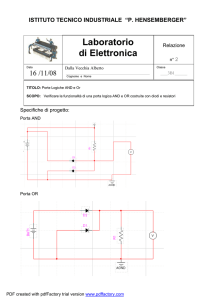

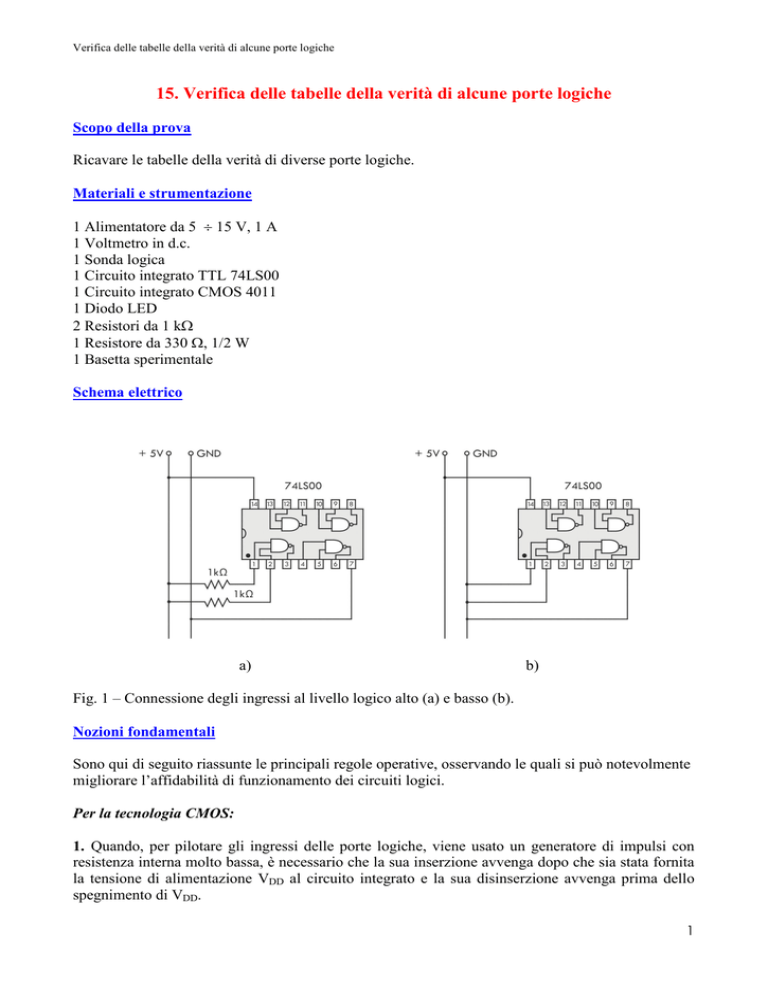

Schema elettrico

a)

b)

Fig. 1 – Connessione degli ingressi al livello logico alto (a) e basso (b).

Nozioni fondamentali

Sono qui di seguito riassunte le principali regole operative, osservando le quali si può notevolmente

migliorare l’affidabilità di funzionamento dei circuiti logici.

Per la tecnologia CMOS:

1. Quando, per pilotare gli ingressi delle porte logiche, viene usato un generatore di impulsi con

resistenza interna molto bassa, è necessario che la sua inserzione avvenga dopo che sia stata fornita

la tensione di alimentazione VDD al circuito integrato e la sua disinserzione avvenga prima dello

spegnimento di VDD.

1

Verifica delle tabelle della verità di alcune porte logiche

2. La tensione di alimentazione non deve mai essere invertita, vale a dire che: VDD – VSS > -0,5 V.

3. Gli ingressi non possono essere lasciati sconnessi. Debbono essere collegati all’uscita di una

porta logica che li piloti, o a massa (VSS), o all’alimentazione (VDD), o insieme ad un altro ingresso.

4. Quando si interfacciano dei dispositivi (circuiti, schede, apparati, ecc.) CMOS ad altri, con la

possibilità che qualche ingresso CMOS rimanga sconnesso, occorre che tali ingressi siano dotati di

resistori di pull-up (collegamento a VDD) o di pull-down (collegamento a VSS) in modo da garantire,

comunque, un livello logico certo.

5. I carichi posti all’uscita delle normali porte CMOS non possono essere collegati a tensioni più

elevate di VDD o più basse di VSS.

Per la tecnologia TTL:

1. Per ottimizzare i tempi di risposta e ridurre l’effetto della suscettibilità ai rumori, gli ingressi non

utilizzati delle porte AND e NAND debbono essere connessi ad una tensione maggiore di VOH, ma

non superiore a VCC.

2. E’ buona norma connettere gli ingressi non utilizzati alla tensione VCC mediante un resistore da 1

kΩ in modo che se avviene un transiente che aumenta la tensione VCC, tali ingressi vengono

protetti.

3. I carichi posti all’uscita delle normali porte TTL non possono essere collegati a tensioni più

elevate di VCC o più basse di VSS.

Per la visualizzazione dello stato dell’uscita delle porte logiche, si può impiegare un diodo LED. Il

reoforo negativo (catodo) è riconoscibile poiché è più lungo dell’altro o perché c’è una tacca, dal

suo lato, nell’involucro plastico.

La corrente necessaria per l’emissione di luce nei normali LED è di circa 16 mA.

Prima della prova

Per procedere nella prova fai riferimento alle caratteristiche statiche CMOS e TTL(LS) fornite dai

data sheet.

1. La tensione VOLMAX è la massima tensione di (ingresso / uscita) per il livello (alto / basso).

2. La VOLMAX per una porta CMOS vale_______ V per VDD = 5 V, vale _______ per VDD = 10 V e

vale _______ V per VDD = 15 V.

3. La tensione VOHMIN è la minima tensione di (ingresso / uscita) per il livello (alto / basso).

4. La VOHMIN per una porta CMOS vale______ V per VDD = 5 V, vale _____V per VDD = 10 V e

vale _______ V per VDD = 15 V.

5. La tensione VILMAX è la massima tensione di (ingresso / uscita) che viene ancora sicuramente

presa come livello (alto / basso).

6. La corrente IOL viene anche indicata come corrente di (sink/source) di una porta logica.

2

Verifica delle tabelle della verità di alcune porte logiche

7. La corrente IOH viene anche chiamata corrente di (sink / source) di una porta logica; viene

indicata come (positiva / negativa).

8. Per una porta CMOS, alimentata con VDD = 10 V la corrente IOH tipica vale ______ mA e la

corrente tipica IOL vale ______ mA.

9. La VOLMAX per una porta TTL LS vale_____ V.

10. La VOHMIN per una porta TTL LS vale_____V.

11. Per una porta TTL LS la corrente IOH tipica vale _______ mA e la corrente IOL tipica vale

______ mA.

12. I circuiti integrati CMOS della serie indicata con “B” (Bufferized) sono caratterizzati da una

(maggiore / minore) capacità di pilotaggio della corrente di uscita.

13. Il valore della corrente IDD media per un integrato CMOS 4011 alimentato a 5 V vale _____

µA, mentre la corrente media ICC per un integrato TTL 74LS00 vale ______ mA.

14. Tutti i dati, le informazioni e le tabelle della verità delle porte logiche mostrate dai manuali si

riferiscono alla logica (positiva / negativa).

15. In logica positiva il livello (alto / basso) di tensione viene indicato come livello logico 1, mentre

il livello (alto / basso) di tensione viene indicato come livello logico 0.

Esecuzione della prova

1. Cabla il circuito secondo lo schema mostrato nella figura 1, relativo all’integrato 74LS00

(quadruple 2- input positive -NAND gates) con una tensione di alimentazione VCC pari a + 5 V ±

5%. Per il cablaggio serviti di una basetta sperimentale di tipo bread-board.

2. La verifica della tabella della verità viene effettuata solo su una delle quattro porte uguali

realizzate all’interno dell’integrato.

Il collegamento dei due ingressi al livello alto (VCC) viene effettuato tramite resistori da 1 kΩ in

modo da evitare eventuali cortocircuiti del morsetto + dell’alimentatore verso la massa se l’ingresso

dell’integrato fosse danneggiato.

Il collegamento dei due ingressi al livello basso può essere effettuato connettendo direttamente a

massa il pin relativo.

3. Spostando i fili delle connessioni dei due ingressi cabla, alternativamente, le quattro

configurazioni di ingresso della tabella della verità di una porta NAND. Impiegando il voltmetro o

il multimetro, misura le tensioni agli ingressi ed all’uscita e completa la tabella 1. In logica

positiva, sostituendo un “1” logico al livello alto di tensione ed uno “0” logico al livello basso,

dovresti ottenere la tabella della verità 2 relativa ad una NAND.

3

Verifica delle tabelle della verità di alcune porte logiche

Ingressi

1 (V)

2 (V)

Uscita

3 (V)

Tabella 1

Ingressi

1

2

0

0

0

1

1

0

1

1

Uscita

3

1

1

1

0

Tabella 2

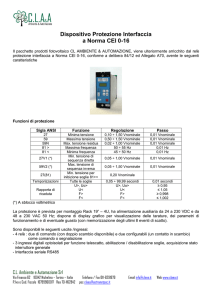

4. Un controllo qualitativo, piuttosto che quantitativo, dei corretti livelli alto e basso dell’uscita in

relazione agli ingressi può essere effettuato con una sonda logica oppure connettendo un diodo LED

all’uscita della porta logica. Il metodo usuale e più corretto è quello mostrato nella figura 2a perché

la porta logica è in grado di assorbire (sink) i 16 mA necessari al diodo LED per illuminarsi con

buona intensità.

5. Con questa connessione l’accensione del diodo avviene quando all’uscita della porta logica che

lo pilota è presente un livello logico basso. E’ per questo motivo che, a volte si effettua il montaggio

mostrato nella figura 2b. In questo caso, però, la porta logica è forzata ad operare in condizioni non

corrette dato che deve erogare una corrente molto superiore a quella tipica quando l’uscita si porta

al livello logico alto.

a)

b)

Fig. 2 - Montaggio corretto (a) e meno corretto (b) di un diodo LED all’uscita di una porta logica.

Il calcolo del valore di R da porre in serie al LED per limitarne la corrente a 12 mA, dà come

risultato ______ Ω.

Il valore che hai calcolato è di circa ______ Ω.

6. La verifica della tabella della verità di una porta NAND CMOS (4011) puoi effettuarla seguendo

gli stessi passi precedenti da 1 a 4. I resistori da 1 kΩ possono essere sostituiti con altri da 10 kΩ.

Considerazioni sulla prova effettuata

1. Le tabelle della verità ottenute per via sperimentale (confermano/non confermano) quelle

teoriche.

2. Nelle porte logiche TTL il livello alto dell’uscita senza alcun carico vale _____ V, mentre il

livello basso vale ______ V.

4

Verifica delle tabelle della verità di alcune porte logiche

3. Nelle porte CMOS alimentate a 5 V, il livello alto dell’uscita senza alcun carico vale _____V

mentre il livello basso vale ______ V.

4. Dall’esame delle tabelle ottenute sperimentalmente si può dedurre che una NAND in logica

positiva equivale ad una _____________ in logica negativa.

5. La tensione VOH di una porta logica (aumenta / diminuisce) all’aumentare della corrente IOH

erogata.

6. Diminuendo il valore del resistore R posto in serie al diodo (Fig. 2a), la tensione VOL (aumenta /

diminuisce).

5