Capitolo V

Comparatori, multivibratori e bistabili.

Capitolo V

Comparatori, multivibratori e bistabili.

5.1) I comparatori.

I comparatori sono dispositivi dotati di due ingressi, v1 e v2 e di un’uscita vo. Uno degli ingressi viene di solito posto ad una tensione di riferimento costante, mentre all’altro viene applicato

un segnale. Supponendo che tale segnale sia applicato all’ingresso v1, mentre all’altro ingresso v2

sia applicata la tensione di riferimento VR, la tensione d’uscita del comparatore sara’:

se v1 − VR < 0

V1

vo =

V

2

V1 ≠ V2

con

se v1 − VR > 0

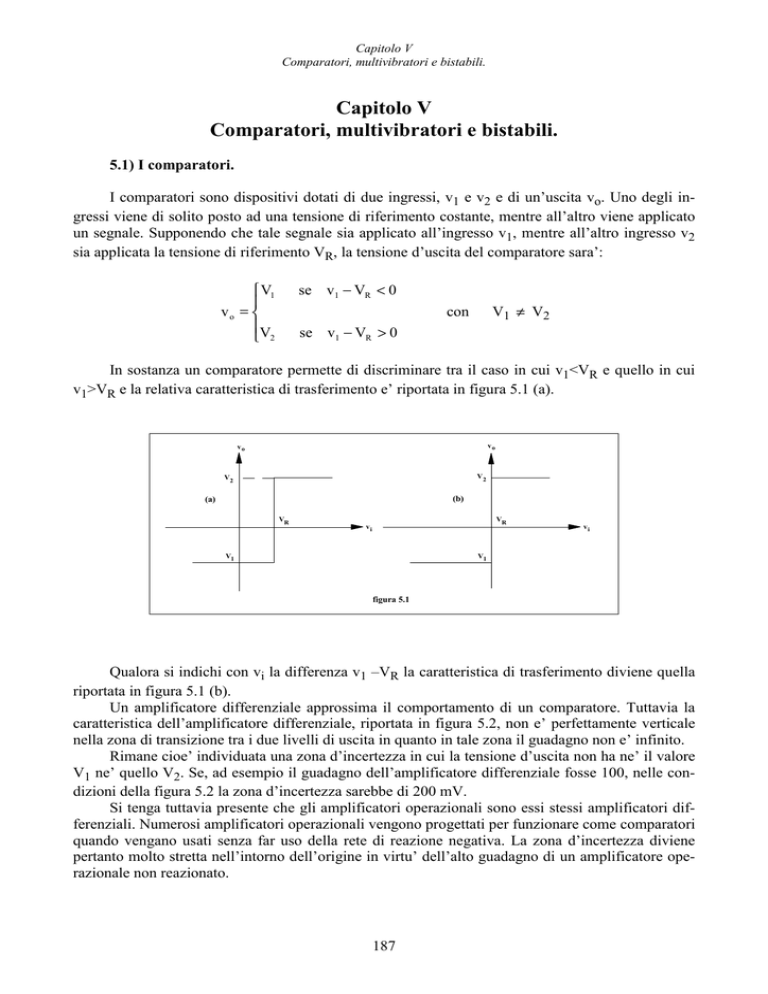

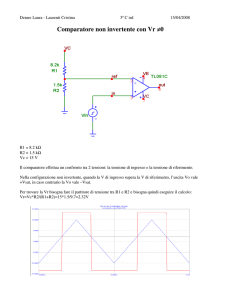

In sostanza un comparatore permette di discriminare tra il caso in cui v1<VR e quello in cui

v1>VR e la relativa caratteristica di trasferimento e’ riportata in figura 5.1 (a).

vo

vo

V2

V2

(b)

(a)

VR

VR

vi

V1

vi

V1

figura 5.1

Qualora si indichi con vi la differenza v1 –VR la caratteristica di trasferimento diviene quella

riportata in figura 5.1 (b).

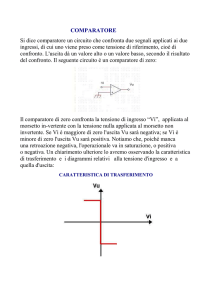

Un amplificatore differenziale approssima il comportamento di un comparatore. Tuttavia la

caratteristica dell’amplificatore differenziale, riportata in figura 5.2, non e’ perfettamente verticale

nella zona di transizione tra i due livelli di uscita in quanto in tale zona il guadagno non e’ infinito.

Rimane cioe’ individuata una zona d’incertezza in cui la tensione d’uscita non ha ne’ il valore

V1 ne’ quello V2. Se, ad esempio il guadagno dell’amplificatore differenziale fosse 100, nelle condizioni della figura 5.2 la zona d’incertezza sarebbe di 200 mV.

Si tenga tuttavia presente che gli amplificatori operazionali sono essi stessi amplificatori differenziali. Numerosi amplificatori operazionali vengono progettati per funzionare come comparatori

quando vengano usati senza far uso della rete di reazione negativa. La zona d’incertezza diviene

pertanto molto stretta nell’intorno dell’origine in virtu’ dell’alto guadagno di un amplificatore operazionale non reazionato.

187

Capitolo V

Comparatori, multivibratori e bistabili.

vo

+10 V

vi

zona di incertezza

-10 V

figura 5.2

In aggiunta, non e’ piu’ necessario compensare l’amplificatore per assicurarne la stabilita’ e

quindi esso avra’ una larghezza di banda superiore a quella degli amplificatori compensati e di conseguenza una maggior velocita’ operativa.

Con tali tecniche l’ampiezza della zona di incertezza e’ dell’ordine della decina di µV, mentre

il tempo di risposta, definito come il tempo necessario affinche’ il comparatore cambi stato, sara’

compreso tra i 20 e i 200 nsec.

Se si volesse poi rendere la tensione d’uscita indipendente dalle tensioni d’alimentazione, si

puo’ ricorrere ad un tosatore realizzato con due diodi zener, come illustrato in figura 5.3, avendo

cura di scegliere la resistenza R di un valore tale da far lavorare i diodi ad una corrente superiore a

quella minima di zener aumentata di quella che viene assorbita dall’eventuale carico connesso in

uscita.

v1

v2

R

+

-

vo

figura 5.3

E’ ovvio inoltre che scegliendo qual’e’ il morsetto cui applicare il segnale e qual’e’ quello cui

applicare la tensione di riferimento VR, si possono ottenere comparatori non invertenti e comparatori invertenti.

I comparatori vengono utilizzati in un gran numero di applicazioni, di cui alcune verranno

prese in considerazione nei paragrafi successivi. Di particolare interesse sono quelle relative alla

generazione di forme d'onda.

188

Capitolo V

Comparatori, multivibratori e bistabili.

5.1.1) Squadramento di un’onda sinusoidale.

La piu’ banale utilizzazione di un comparatore e’ quella che permette di passare da un’onda

sinusoidale ad un’onda quadra di uguale periodo. Se, infatti, la tensione di riferimento VR viene posta a zero, l’uscita variera’ tra i due livelli ogni volta che la sinusoide attraversa lo zero. La velocita’

della transizione sara’ determinata dallo slew-rate del comparatore. E’ pertanto semplice, qualora si

conoscano lo slew-rate e i livelli di tosatura, valutare il tempo di salita e di discesa dell’onda quadra

d’uscita

5.1.2) Generazione di impulsi.

Se in cascata allo squadratore viene connesso un circuito differenziatore, come illustrato in figura 5.4, si ottiene una struttura che fornisce in uscita una serie di impulsi, positivi quando lo squadratore esegue la transizione basso-alto, negativi nel caso opposto.

T

vi

+

D

C

vo

-

R

Rc

figura 5.4

E’ evidente che per un corretto funzionamento la costante di tempo del gruppo RC deve essere piccola rispetto il periodo T dell’onda quadra. Se poi si volessero impulsi di un solo segno e’

sufficiente inserire in cascata il diodo D e il resistore Rc. La polarita’ degli impulsi ricavati dipende

evidentemente dal verso con cui il diodo viene inserito in circuito.

Lo squadratore e il generatore di impulsi presentati non sono tuttavia esenti da critiche. Se, infatti, l’ampiezza del segnale vi e’ molto prossima allo zero, la presenza di segnali spuri, ad esempio

rumore, potrebbe far commutare il comparatore anche quando non dovrebbe. Questo effetto puo’

venire ridotto ricorrendo a comparatori rigenerativi, cioe’ a comparatori che fanno uso di una retroazione positiva. Un ulteriore vantaggio che in tal caso si consegue e’ anche quello di ridurre il

tempo di commutazione.

5.1.3) Il trigger di Schmitt.

Si consideri il circuito illustrato in figura 5.5.

189

Capitolo V

Comparatori, multivibratori e bistabili.

vs

vi

R

-

vo

+

R1

vr

R2

figura 5.5

Il segnale sia applicato all’ingresso invertente, mentre a quello non invertente sia applicata la

tensione di reazione vR. Se la resistenza di uscita del comparatore e’ trascurabile rispetto a R1+R2 e

contemporaneamente l’impedenza dell’ingresso non invertente e’ molto elevata (ipotesi normalmente realizzate), si puo’ affermare che:

vR =

R2

.v o

R1 + R 2

Da quanto visto per gli amplificatori operazionali, con vs = 0 si ha vi = vR e vo = Ao.vi, dove

con Ao si e’ indicato il guadagno a catena aperta del comparatore. In definitiva, con semplici passaggi si ottiene un guadagno d’anello pari a:

T=−

R2

.A o

R1 + R 2

Poiche’ Ao ha valori molto elevati e’ possibile rendere T in modulo considerevolmente superiore all’unita’. E’ immediato verificare, anche qualitativamente, che la reazione e’ positiva. Se, infatti, l’uscita aumentasse di ∆vo, il segnale riportato all’ingresso non invertente sarebbe

R2

.∆v o

R1 + R 2

e l’uscita crescerebbe ulteriormente di una quantita’ pari a:

∆v o .A o .

R2

= −T.∆v o

R1 + R 2

tendendo pertanto ad allontanarsi ulteriormente dal valore iniziale.

190

Capitolo V

Comparatori, multivibratori e bistabili.

L’effetto della reazione pertanto, anziche’ ridurre l’errore, tende a far divergere l’uscita, confermando che si e’ in presenza di una reazione positiva.

Indicando con Vo la quantita’ Vz+VD, dove VD e’ la tensione diretta e Vo la tensione di zener

dei diodi, e supponendo che vs sia minore di VR in modo tale che vo = +Vo, si ricava che:

vR =

R2

.v o = V1

R1 + R 2

Facendo ora aumentare il valore di vs la situazione permane inalterata finche’ non viene raggiunto il valore V1. In corrispondenza a tale valore, detto tensione di soglia, il comparatore commuta e la sua uscita si porta a – Vo, dove rimarra’ finche’ vs e’ maggiore di vR. Tale tensione si e’

tuttavia modificata e nelle nuove condizioni operative e’ pari a:

v R = − Vo .

R2

= V2

R1 + R 2

Per ritornare alle condizioni iniziali sara’ quindi necessario che la tensione di ingresso vs

scenda al di sotto di V2. Si hanno cioe’ due tensioni di soglia, di cui la prima rappresenta la soglia

di scatto quando il segnale ha derivata positiva, la seconda la soglia di scatto con un segnale a derivata negativa.

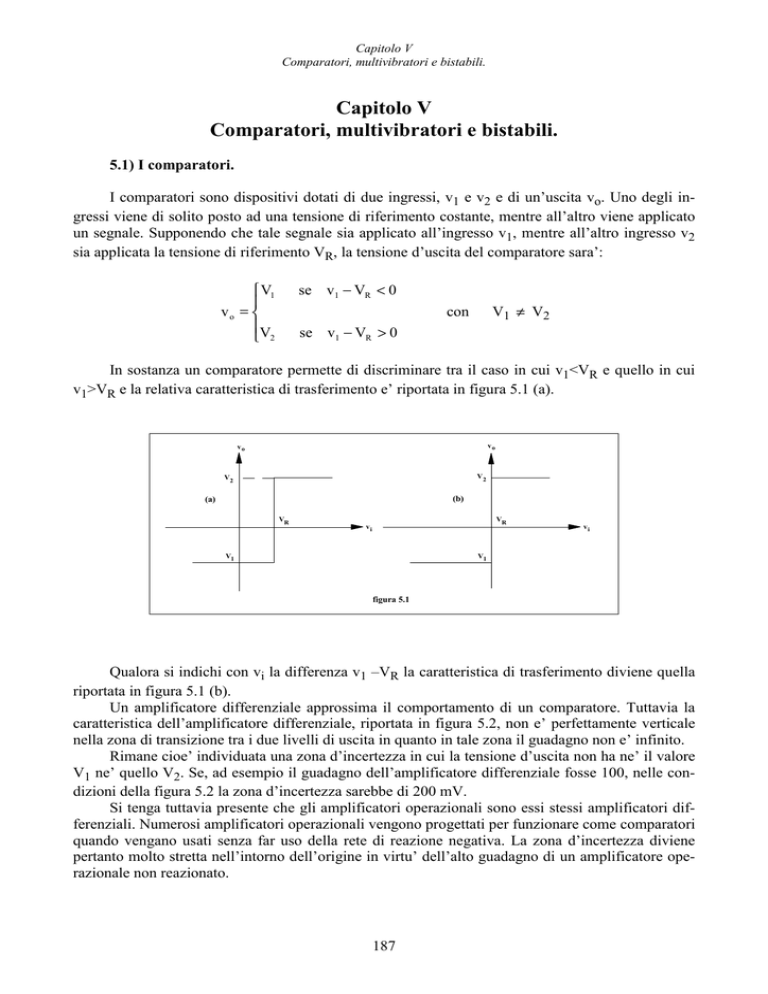

La caratteristica di trasferimento e’ illustrata in figura 5.6 in cui sono evidenziate le traiettorie

seguite in salita e in discesa.

vo

Vo

V1

V2

vs

-Vo

figura 5.6

In tale diagramma si nota la presenza di un ciclo di isteresi che permette di evitare commutazioni spurie in presenza di segnali di disturbo, almeno finche’ la loro ampiezza si mantiene inferiore

alla larghezza del ciclo.

Nelle ipotesi che sono state prese in considerazione tuttavia le soglie di scatto si trovano posizionate simmetricamente rispetto allo zero; pero’ se il partitore di uscita viene terminato su una tensione ausiliaria VA anziche’ a massa, le due tensioni di soglia rimangono determinate in:

V1 = VA +

R2

.(Vo − VA )

R1 + R 2

V2 = VA −

191

R2

.(Vo + VA )

R1 + R 2

Capitolo V

Comparatori, multivibratori e bistabili.

Se ad esempio si assumesse Vo = Vz+VD = 7 V, R1 = 100 Ω, R2 = 10 kΩ e VA = 1 V si

avrebbe:

V1 = 1 +

0,1.6

= 1,059

10,1

V2 = 1 −

V

0,1.8

= 0,921

10,1

V

e la differenza tra questi due valori

V1 − V2 = 2.

R2

.Vo

R1 + R 2

che nel caso in esame e’ pari a 0,138 V, fornisce l’ampiezza del ciclo di isteresi.

Tale ampiezza e’ legata al guadagno d’anello; se questo e’ esattamente uguale a –1 il ciclo di

isteresi si annulla. Tuttavia il guadagno complessivo del sistema reazionato e’ molto elevato e la

commutazione avviene con estrema rapidita’.

Nella pratica si sceglie un valore di |T| leggermente superiore all’unita’ ottenendo un valore di

isteresi relativamente piccolo e una velocita’ di commutazione lievemente inferiore alla massima

ottenibile.

Nel caso che si sta esaminando, supponendo che il guadagno a catena aperta sia pari a 104 il

guadagno d’anello diventa

T=−

0,1.10 4

= 99

10,1

e da’ luogo ad un’isteresi relativamente ampia.

Un trigger di Schmitt puo’ essere realizzato facilmente anche a componenti discreti. Un

esempio in cui vengono utilizzati transistori a giunzioni e’ riportato in figura 5.7.

Vcc

I c1

R1

R2

I c2

Vc1

Vo

Vin

RE

VE

figura 5.7

Per un adeguato funzionamento e’ necessario che le due resistenze di carico di collettore R1 e

R2 abbiano valore diverso con R1 > R2 in modo che le due correnti Ic1 e Ic2 abbiano diverso valore

quando i rispettivi transistori T1 e T2 vengono portati in saturazione. Si supponga, infatti, che la

tensione Vin di ingresso sia nulla. In queste condizioni T1 sara’ interdetto, mentre T2 sara’ lievemente saturato se R1 e’ stata scelta in maniera opportuna. Pertanto

192

Capitolo V

Comparatori, multivibratori e bistabili.

Vo = Vcc − R 2 .I c 2 (sat )

e se il guadagno di corrente β f =

I c (sat )

Ib

si puo’ ancora considerare molto maggiore dell’unita’, al-

lora

VE ≅ R E .I c 2 (sat )

Per portare in conduzione T1 sara’ allora necessaria una tensione di ingresso pari a

Vin = VBE (on ) + VE

La diminuzione di Vc1, dovuta alla caduta su R1, tende tuttavia a portare T2 verso

l’interdizione; la tensione di uscita Vo pertanto sale e tende al valore Vcc. Quando T1 e’ giunto alla

soglia della saturazione e T2 all’interdizione la tensione VE sara’ diventata pari a

VE = R E .I c1(sat )

Poiche’ tuttavia R1 > R2 si avra’ Ic1(sat) < Ic2(sat) e quindi per riportare T1 in interdizione la

tensione di ingresso Vin dovra’ scendere al di sotto del valore

R E .I c1(sat ) + VBE (on ) < R E .I c 2 (sat ) + VBE (on )

Si ha quindi anche in questo caso un’isteresi e il fatto che durante la transizione di Vin da valori bassi a valori elevati la soglia di commutazione si abbassi permette di affermare che una volta

che la tensione di ingresso abbia superato il valore R E .I c 2 (sat ) + VBE (on ) la commutazione di T1 e’ favorita, mettendo in evidenza l’esistenza di un fenomeno rigenerativo a tutto vantaggio della velocita’ di commutazione.

5.1.4) Generatori di onda quadra.

Un oscillatore con uscita ad onda quadra puo’ essere realizzato connettendo tra uscita e ingresso invertente di un trigger di Schmitt una rete RC di reazione. Il relativo circuito assieme alle

forme d’onda di interesse e’ riportato in figura 5.8

Con riferimento a tale figura la tensione differenziale di ingresso vi puo’ essere valutata in

v i = v c − v1 = v c − β.v o

R2

.

R1 + R 2

Indicando con Vo la somma della tensione di uno dei diodi zener e della caduta diretta

dell’altro diodo, la tensione di uscita sara’ vo =Vo se vi < 0, mentre se vi > 0 assumera’ il valore

vo = -Vo.

dove β =

193

Capitolo V

Comparatori, multivibratori e bistabili.

V

R

vo

A

C

vi

-

R3

+

vo

β vo

R1

T/2

vc

T

vc

R2

v1= βvo

t

−β vo

-vo

figura 5.8

Si prenda allora in considerazione la situazione in cui vi < 0 o in altre parole vc < βVo, quando

cioe’ la tensione di uscita vo ha assunto il valore Vo. Cio’ significa che il condensatore C si sta caricando esponenzialmente con costante di tempo RC verso li valore Vo.

In questa situazione l’uscita rimane fissata al valore Vo finche’ la tensione vc non raggiunge il

valore βVo. In questo istante la tensione di uscita commuta a – Vo e il condensatore inizia a portarsi, sempre in modo esponenziale con costante di tempo RC, verso la tensione – Vo. Anche in

questo caso la tensione di uscita permane inalterata finche’ vc non scende al di sotto del valore βVo facendo ricommutare l’uscita a Vo e riiniziando il ciclo.

Se si indica con t = 0 l’istante in cui vc = -βVo l’evoluzione della tensione ai capi di C e’:

t

t

−

−

v c (t ) = −β.Vo + (Vo + β.Vo ).1 − e RC = Vo .1 − (1 + β ).e RC

Indicando poi con T/2 l’istante in cui vc(t) raggiunge il valore β.Vo e tenendo presente la

simmetria di funzionamento nei due semiperiodi dell’onda quadra d’uscita, il periodo T puo’ venir

ricavato ponendo t = T/2 e risolvendo rispetto a T l’espressione precedente. Si ottiene:

T = 2.RC. ln

R

1+ β

= 2.RC. ln1 + 2

1− β

R1

Il periodo dell’onda quadra puo’ quindi essere controllato agendo sulla costante di tempo RC

ed e’ indipendente da Vo. La frequenza tuttavia non puo’ essere fatta salire troppo in alto, perché lo

slew-rate del comparatore determina fronti d’onda non verticali.

Se si volesse ottenere un’onda rettangolare con semiperiodi di diversa durata, la resistenza R

puo’ essere sostituita dall’arrangiamento circuitale di figura 5.9 in modo che il condensatore C si

carichi nei due semiperiodi con costante di tempo diversa.

194

Capitolo V

Comparatori, multivibratori e bistabili.

figura 5.9

In alternativa nel nodo A (figura 5.8) si puo’ sommare tramite una resistenza R un’opportuna

tensione Vp. In tal caso nella prima semionda il condensatore si carichera’ con una costante di

tempo pari a RC/2 verso il valore (Vp + Vo)/2, mentre nel secondo semiperiodo tendera’, sempre in

modo esponenziale e con la medesima costante di tempo, al valore (Vp –Vo)/2.

Si lascia al lettore il compito di determinare, a titolo d’esercizio, la durata dei due semiperiodi.

5.1.5) Generatori di onda triangolare.

La forma dell’onda prelevabile ai capi del condensatore C del generatore d’onda quadra del

paragrafo precedente ha un andamento approssimativamente triangolare. Tuttavia l’effettivo andamento e’ formato da archi di esponenziale in quanto tale capacita’ viene caricata e scaricata a tensione costante attraverso la resistenza R.

Si puo’ allora pensare di rendere effettivamente rettilinea la forma d’onda facendo si’ che la

capacita’ si carichi e scarichi a corrente costante, utilizzando un integratore, come illustrato nello

schema di figura 5.10.

C

v2 = VR

v1

R3

-

R

vo

+

R1

R2

-

Vs

+

vo' (t)

VA

v(t)

Vmax

VR .

R 1+ R 2

R2

Vmin

T

T1

T2

figura 5.10

195

t

Capitolo V

Comparatori, multivibratori e bistabili.

Si noti che a causa dell’inversione introdotta dall’integratore la tensione di uscita non viene

riportata all'ingresso invertente del comparatore, ma viene utilizzata come riferimento VA del partitore formato dalle resistenze R1 e R2.

Si supponga allora che vo (tensione di uscita del trigger di Schmitt) si trovi inizialmente al

valore -Vo. L’uscita dell’integratore v ,o sara’ allora una rampa di tensione a derivata positiva e la

tensione v1 all’ingresso non invertente del comparatore sara’, per il principio di sovrapposizione

degli effetti:

v1 = −

R2

R1

.Vo +

.v ,o

R1 + R 2

R1 + R 2

Quando tale tensione raggiunge il valore della tensione di riferimento VR, presente

all’ingresso invertente del comparatore, quest’ultimo scatta, facendo passare la sua tensione di

uscita al valore +Vo. L’uscita dell’integratore diviene allora una rampa a derivata negativa e indicando con Vmax la tensione di uscita dell’integratore alla quale avviene la commutazione, dalla relazione precedente si ricava per v1 = VR che:

Vmax =

R1 + R 2

R

.VR + 2 .Vo

R1

R1

Con considerazioni analoghe si puo’ trovare che il minimo valore della tensione di uscita e’:

Vmin =

R1 + R 2

R

.VR − 2 .Vo

R1

R1

Pertanto l’escursione picco-picco della tensione triangolare di uscita e’:

Vmax − Vmin = 2.Vo .

R2

R1

Si vede quindi che l’ampiezza dell’oscillazione puo essere controllata variando il rapporto tra

le due resistenze R1 e R2, mentre il suo valor medio puo’ essere variato agendo su VR. In particolare se VR = 0 l’onda triangolare di uscita ha valor medio nullo.

Per determinare il periodo della forma d’onda in corrispondenza a Vs = 0 e’ sufficiente osservare che all’uscita dell’integratore la tensione evolve nel tempo secondo la:

v ,o (t ) = −

1

.Vo .t

R.C

1

.Vo .

R.C

Nel primo semiperiodo (T1) tale tensione deve variare tra Vmax e Vmin e pertanto

e quindi la sua velocita’ di variazione e’ in valore assoluto pari a

R

1

.V0 .T1 = Vmax − Vmin = 2.Vo . 2

R.C

R1

196

Capitolo V

Comparatori, multivibratori e bistabili.

Si ottiene quindi:

T1 = 2.

R 2 .R.C

R1

Stante la simmetria dei due semiperiodi, per la situazione che si sta considerando si conclude

pertanto che:

T = 4.

R.R 2 .C

R1

che come si puo’ notare e’ indipendente da Vo.

Quando invece Vs fosse diversa da zero le due rampe che formano l’onda triangolare hanno

pendenza diversa. Una, infatti, avra’ una pendenza pari a (Vo + Vs ) / RC , l’altra (Vo − Vs ) / RC . E’

facile allora dimostrare che il rapporto tra i due semiperiodi T1 e T2 e’ dato da:

T1 Vo − Vs

=

T2 Vo + Vs

L’uso di una tensione Vs permette quindi di variare il duty cycle δ, definito come δ =

ottiene quindi:

1 Vs

1 −

2 Vo

δ=

e la variazione di δ e’ lineare con Vs.

Anche il periodo T varia con Vs. Si ha, infatti, per quanto detto:

T1 = 2.

T2 = 2.

R.R 2 .C

1

.

R 1 1 + Vs

Vo

R.R 2 .C

.

R1

e di conseguenza

197

1

V

1− s

Vo

T1

. Si

T

Capitolo V

Comparatori, multivibratori e bistabili.

R.R 2 .C 1

R.R 2 .C

1

1

T = T1 + T2 = 2.

.

+

= 4.

.

Vs

V

R1

R1

V

1− s

1+

1 − s

V

V

o

o

Vo

2

Si vede pertanto che, rispetto al caso in cui Vs = 0 il periodo varia secondo il fattore

V

1 − s

Vo

2

e che man mano che la tensione Vs cresce, la frequenza del segnale generato diminuisce.

5.1.6) Il circuito monostabile.

Il generatore d’onda quadra del paragrafo 5.1.4 puo’ essere modificato inserendo in parallelo

al condensatore C un diodo di tosatura, secondo lo schema di figura 5.11.

Si ottiene in tal caso un circuito atto a generare, in corrispondenza ad un opportuno segnale di

trigger, un impulso d’uscita di prefissata durata. In sostanza il circuito si trova normalmente in una

situazione stabile e solo in presenza di un opportuno segnale d’ingresso commuta la sua uscita, rimanendo in tale situazione per un prefissato periodo T, dopodiche’ ritorna alla condizione di partenza. Un circuito con tale tipo di funzionamento prende il nome di circuito monostabile.

vc = v1

D1

t

R

vc

C

D2

vi

+

t

verso Vo

R3

vo

V1

v2 = β vo

t

T'

τ

vo

R2

V1

T

R1

- β Vo

Vo

T

v

Vo

verso -Vo

t

- Vo

figura 5.11

Si assuma che il sistema si trovi nel suo stato stabile con vo = +Vo. In questa situazione la tensione ai capi del condensatore rimane fissata dal diodo al valore V1 approssimativamente pari a 0,7

V. E’ ovvio che, affinche’ la situazione descritta sia reale, la tensione di soglia βVo deve essere

maggiore di V1.

Se ora all’ingresso non invertente viene applicato un impulso di trigger (negativo) d’ampiezza

superiore a βVo – V1, il comparatore commuta e la sua uscita si porta a – Vo. E’ opportuno far notare che in questa discussione il diodo D2 non ha alcuna rilevanza, se non quella di impedire che

eventuali impulsi positivi spuri che si possono presentare all’ingresso possano andare a disturbare il

corretto funzionamento.

198

Capitolo V

Comparatori, multivibratori e bistabili.

Nella nuova situazione il condensatore si carichera’ esponenzialmente verso il valore – Vo

con costante di tempo RC e, quando ai suoi capi la tensione sara’ scesa al di sotto di -βVo, il comparatore commutera’ nuovamente riportando l’uscita al valore +Vo.

Il condensatore allora riprende a caricarsi esponenzialmente verso tale valore, ma quando ha

raggiunto il valore V1 il diodo D1 passa in conduzione esercitando la sua azione di tosatura.

La durata T dell’impulso e’ facilmente determinabile. Durante tale intervallo infatti

l’andamento della tensione vc ai capi del condensatore e’:

t

−

R .C

v c (t ) = V1 − (Vo + V1 ).1 − e

Ponendo in questa relazione vc(t) = -βVo e t = T e risolvendo rispetto T si ottiene:

V1

Vo

T = R.C. ln

1− β

1+

Se e’ possibile affermare, come normalmente avviene, che Vo >> V1 e si pone R1 = R2, da cui

consegue che β = ½, allora:

T = R.C. ln 2 = 0,69.R.C

E’ bene far osservare che la durata dell’impulso di trigger deve essere molto minore della durata T dell’impulso d’uscita e che l’impulso successivo di trigger deve essere a distanza T’ alquanto

superiore della durata T poiche’ la tensione ai capi del condensatore C raggiunge il suo valore di riposo V1 solo dopo un tempo T’ > T.

E’ possibile tuttavia realizzare circuiti monostabili in cui tale vincolo viene rimosso. Si puo’

cioe’ riapplicare l’impulso di trigger addirittura quando l’impulso d’uscita non e’ ancora terminato,

prolungandolo per un ulteriore periodo T. Un circuito che si comporta in tal modo prende il nome di

monostabile retriggerabile. Un possibile arrangiamento circuitale e’ riportato in figura 5.12.

+ Vcc

R1

R

+

+

v

C

-

vc

R2

-VGG

figura 5.12

199

vo

Capitolo V

Comparatori, multivibratori e bistabili.

Nello stato di riposo il JFET d’ingresso a causa della polarizzazione di gate risulta interdetto;

di conseguenza il condensatore C e’ carico alla tensione Vcc e tale tensione e’ applicata all’ingresso

invertente del comparatore. All’ingresso non invertente e’ invece applicata la tensione

β Vcc =

R2

.Vcc

R1 + R 2

L’uscita del comparatore si trova quindi al livello basso – Vo.

Si supponga ora di applicare all’ingresso del JFET un impulso positivo tale da portarlo in

conduzione. Il condensatore allora si scarica attraverso il JFET, con una corrente anche rilevante e

con un andamento inizialmente a rampa, che diventa esponenziale quando il JFET entra nella zona

di funzionamento resistiva. Non appena la tensione vc scende al di sotto di βVcc il comparatore

commuta e la sua uscita si porta a + Vo.

L’impulso di trigger sia sufficientemente lungo da scaricare in maniera pressocche’ completa

il condensatore. Alla fine dell’impulso, quest’ultimo iniziera’ a caricarsi esponenzialmente, con costante di tempo RC verso il valore Vcc e non appena sara’ raggiunta le tensioni di soglia βVcc il

comparatore tornera’ a commutare riportando la sua uscita al valore – Vo.

La durata T dell’impulso d’uscita e’ evidentemente data da:

R

T = R.C. ln1 + 2

R1

L’espressione ricavata e’ evidentemente approssimata in quanto non tiene conto

dell’intervallo che intercorre tra l’istante in cui vc scende al di sotto di βVcc e quello Tp in cui

l’impulso d’ingresso ritorna a zero, tuttavia se le ipotesi fatte sono rispettate e se Tp <<T non si

commette un grande errore.

Un aspetto interessante tuttavia risiede nel fatto che nel caso in esame non e’ piu’ necessario

attendere che il condensatore C sia ritornato nella condizione di riposo prima di applicare un successivo impulso di trigger. Il nuovo impulso puo’ essere fornito immediatamente dopo l’intervallo

T o addirittura quando l’impulso d’uscita e’ ancora presente. In ambedue i casi il condensatore C

viene immediatamente scaricato dando origine ad un nuovo intervallo T durante il quale l’uscita si

trovera’ al valore alto + Vo.

Un monostabile retriggerabile puo’ venir impiegato, ad esempio, per rivelare se al suo ingresso sia o no presente un’onda quadra di periodo inferiore a T.

Unica condizione da rispettare per un corretto funzionamento e’ che la costante di tempo RC

del circuito di ingresso sia molto minore del periodo T dell’onda quadra in modo da applicare al

gate del JFET impulsi molto stretti e tali che il periodo di tenuta del monostabile sia effettivamente

rappresentato dalla relazione approssimata precedentemente ricavata.

5.2) I multivibratori.

I circuiti illustrati ai paragrafi precedenti possono venir facilmente realizzati ricorrendo a

porte logiche anziche a comparatori.

200

Capitolo V

Comparatori, multivibratori e bistabili.

Nei paragrafi successivi verranno prese in considerazione le principali caratteristiche di tali

circuiti, esaminandone, sia pure sommariamente il funzionamento.

5.2.1) Il multivibratore bistabile.

Un semplice multivibratore bistabile (comunemente detto anche flip-flop), cioe’ un circuito

che possiede due stati stabili, si puo’ ottenere interconnettendo secondo lo schema di figura 5.13

due porte logiche di tipo NOR. Nella stessa figura sono riportati anche i diagrammi di temporizzazione dei segnali idealizzati presenti nei vari punti del circuito.

S

s

x

C

y

c

y

x

t2

t1 t3 t4

t7

t5t6 t8

figura 5.13

All'istante iniziale ambedue gli ingressi siano 0, l'uscita Y sia 0, quella X sia 1; poiche' le

uscite sono riportate agli ingressi delle porte NOR, la condizione ipotizzata e' una condizione stabile. Infatti, il NOR 2 ha come ingressi C=0 e X=1 e quindi la sua uscita e' Y=0, mentre il NOR 1

avendo ambedue gli ingressi nulli ha come uscita X=1.All'istante t1 l'ingresso S vada a 1. Gli ingressi del NOR 1 passano percio' da 00 a 01 e dopo un ritardo pari a t2 - t1 la sua uscita X passa a 0.

Questo fatto fa cambiare gli ingressi del NOR 2 da 01 a 00 in modo che, dopo un ritardo pari a t3

- t2, l'uscita Y passa a 1. Non si ha alcun ulteriore effetto, ne' per la commutazione a 11 degli ingressi del NOR 1, ne' per il passaggio di S a 0 all'istante t4. La nuova condizione raggiunta e' stabile.

Una sequenza analoga, ma inversa, ha luogo quando l'ingresso C passa a 1, riportando il circuito nella condizione iniziale.

Un flip-flop che operi nel modo descritto prende il nome di flip-flop set-reset, viene indicato

con il simbolo RS ed e' rappresentato con il simbolo di fig. 5.14 (a).

Gli ingressi S e R corrispondono a quelli S e C di fig. 5.13, mentre l'uscita Q corrisponde a Y ,

quella Q a X .

Il funzionamento del circuito e' riassunto in modo completo nella tabella di fig. 5.14 (b). S, R

e Qn indicano il valore degli ingressi e dell'uscita all'arbitrario istante tn, mentre Qn+1 indica il valore assunto dall'uscita nell'istante immediatamente successivo per effetto degli ingressi applicati

all'istante tn.

Le condizioni delle ultime due righe indicano che nel normale funzionamento non e' permesso

che ambedue gli ingressi diventino 1 allo stesso tempo.

201

Capitolo V

Comparatori, multivibratori e bistabili.

S

Q

R

S

R

Qn

Q n+1

0

0

0

0

0

0

1

1

0

1

0

1

0

1

0

0

1

0

0

1

1

1

1

0

1

1

1

0

1

1

-

(a)

(b)

figura 5.14

E' immediato verificare che la tabella di fig. 5.14 e' retta dall'equazione

Q n +1 = S+ Q n .R

ottenuta sfruttando le condizioni delle ultime due righe e imponendo il vincolo

S. R = 0

Gli ingressi S e R corrispondono a quelli S e C di fig. 5.13, mentre l'uscita Q corrisponde a Y ,

quella Q a X .

Il funzionamento del circuito e' riassunto in modo completo nella tabella di fig. 5.14 (b). S, R

e Qn indicano il valore degli ingressi e dell'uscita all'arbitrario istante tn, mentre Qn+1 indica il valore assunto dall'uscita nell'istante immediatamente successivo per effetto degli ingressi applicati

all'istante tn.

Le condizioni delle ultime due righe indicano che nel normale funzionamento non e' permesso

che ambedue gli ingressi diventino 1 allo stesso tempo.

La ragione per cui i due ingressi non possono essere contemporaneamente 1 e' duplice; in

primo luogo perche' essi porterebbero ambedue le uscite a 0 violando la condizione base di funzionamento di un flip-flop, secondo la quale le due uscite devono essere sempre complementari. In secondo luogo, se ambedue gli ingressi tornassero a 0 al medesimo istante lo stato in cui il flip-flop si

porterebbe non sarebbe prevedibile e al limite potrebbe realizzarsi una condizione d’oscillazione.

Quello che e’ sicuro e’ che lo stato in cui il flip-flop si porta dopo che i due ingressi sono stati

riportati al valore logico 0 viene a dipendere da quale dei due NOR ha un tempo di propagazione

minore. Considerazioni anche intuitive permettono di convincersi di cio’ rendendo evidente che la

condizione descritta porta ad una perdita di controllo.

Con il vincolo S.R = 0 il flip-flop RS realizza invece un dispositivo di memorizzazione affidabile, in cui lo stato delle uscite indica quale dei due ingressi si e' trovato per ultimo al livello 1.

E' abbastanza evidente da questa analisi qualitativa del funzionamento del flip-flop RS che un

impulso d’ingresso deve avere una durata minima se si vuole che la commutazione avvenga con si202

Capitolo V

Comparatori, multivibratori e bistabili.

curezza; si supponga, infatti, che S ritorni a zero prima dell'istante t3; ambedue gli ingressi del NOR

1 si troverebbero allora, almeno momentaneamente, a 0 e tenderebbero a far tornare X a 1. Il verificarsi di tale condizione renderebbe evidentemente incerto il funzionamento del circuito.

Esistono ovviamente strutture piu’ complesse che non quella del flip-flop preso in considerazione. In particolare esistono i flip-flop sincroni, la cui commutazione puo’ avvenire solo in determinati istanti fissati da un segnale di sincronizzazione (clock).

5.2.2) Il multivibratore monostabile.

In figura 5.15 e’ riportato lo schema di un multivibratore monostabile ottenuto utilizzando

porte NOR. Per semplicita’ d’analisi si supporra’ che esse siano realizzate in tecnologia CMOS

cioe’ tali da avere impedenze d’ingresso elevatissime.

Si noti che l’accoppiamento tra la prima e la seconda porta e’ di tipo capacitivo, mentre

quella tra la seconda e la prima e’ di tipo resistivo (nel caso in esame e’ addirittura un cortocircuito). Si ricordi poi che i MOS utilizzati (ad arricchimento) necessitano per passare in conduzione

che al loro ingresso sia applicata una tensione superiore alla tensione di soglia VT>0.

+VDD

R

vin

vo1

vx

vo2

C

figura 5.15

All’istante iniziale sia Vin = 0; di conseguenza vo1 = VDD se anche l’altro ingresso si

trova a tensione nulla. L’ingresso vx della seconda porta si trova, nelle condizioni prospettate, alla

tensione VDD poiche’, se la situazione ipotizzata si e’ mantenuta inalterata per un tempo sufficientemente lungo, il condensatore C si sara’ caricato a tale tensione attraverso la resistenza R. Di conseguenza la sua uscita si trova ad un valore nullo confermando le ipotesi precedenti e permettendo

di affermare che la condizione descritta e’ stabile.

Se ora all’ingresso Vin è applicato un impulso positivo di trigger di ampiezza superiore a

VT, l’uscita della relativa porta passa a 0. Poiche’ la tensione ai capi del condensatore non puo’

cambiare istantaneamente anche vx passa a 0 determinando la commutazione del secondo gate, la

cui uscita vo2 passa a VDD.

Questo segnale, riportato all’ingresso della prima porta, fa si’ che la relativa uscita rimanga

a 0 anche quando l’impulso di trigger e’ terminato. A partire da tale istante tuttavia il condensatore

inizia a caricarsi attraverso la resistenza R e quindi Vx tende a VDD secondo la:

203

Capitolo V

Comparatori, multivibratori e bistabili.

t

−

v x (t ) = VDD .1 − e R .C

Quando vx raggiunge la tensione di soglia VT, la seconda porta commuta e vo2 passa a 0, causando a sua volta la commutazione della prima porta, secondo quanto indicato in figura 5.16.

v in

v o1

VDD=V(1)

V>VT

t

t

T<T1

T1

v o2

vx

VDD+ V

T

VDD

V DD

VT

t

T1

T1

figura 5.16

La commutazione avviene quando:

T

− 1

v x (T1 ) = VDD .1 − e R .C = VT

Risolvendo tale equazione rispetto T1 si ottiene:

T1 = R.C. ln

VDD

VDD − VT

Se VT = VDD/2, come spesso avviene con le porte CMOS, si ha:

T1 = 0,69.R.C

204

t

Capitolo V

Comparatori, multivibratori e bistabili.

Indicando con vc = vo1 – vx la tensione ai capi del condensatore C si puo’ osservare che immediatamente prima della commutazione vc =-VT. Poiche, come detto, la tensione ai capi di un

condensatore non puo’ variare istantaneamente, affinche’ tale situazione si conservi dopo la commutazione, quando vo1 = VDD, si deve avere:

v c = VDD − v x = − VT

e pertanto vx = VDD + VT. A partire da queste condizioni iniziali il condensatore C si scarica attraverso la resistenza R con costante di tempo RC fino a che vc = 0.

Per un corretto funzionamento sarebbe necessario attendere che la scarica di C si fosse completata, imponendo pertanto un vincolo abbastanza pesante alla massima frequenza degli impulsi di

trigger. Inoltre la tensione che si presenta all’ingresso della seconda porta all’istante T1 e’ VDD +

VT e in alcuni casi essa potrebbe essere superiore al massimo valore ammissibile. Per tali motivi

molto spesso in parallelo alla resistenza R viene posto un diodo D, come illustrato in figura 5.17.

+VDD

R

D

vx

C

figura 5.17

Questo arrangiamento circuitale contiene il massimo valore di vx a VDD + Vγ, dove con Vγ si

e’ indicata la tensione di soglia del diodo D. Se esso e’ un diodo al silicio il massimo valore di vx

sara’ approssimativamente pari a VDD + 0,6 volt. Il diodo tuttavia ha anche un altro effetto positivo;

esso permette infatti la scarica rapida di C riducendo pertanto l’intervallo di tempo che e’ necessario

attendere prima di poter applicare il successivo impulso di trigger.

5.2.3) Il multivibratore astabile.

Le porte logiche possono essere utilizzate anche per realizzare circuiti autoscillanti con

uscita in onda quadra (multivibratori astabili). Si prenda, infatti, in considerazione il semplice circuito illustrato in figura 5.18, realizzato con due porte NOR utilizzate peraltro come semplici invertitori.

205

Capitolo V

Comparatori, multivibratori e bistabili.

vx

vo1

vo2

R

C

vc

figura 5.18

Si supponga per semplicita’ che la tensione di soglia VT sia pari a VDD/2. Si faccia poi

l’ipotesi che all’istante iniziale la tensione d’uscita del primo gate vo1 commuti da VDD a 0, come

e’ anche illustrato nelle forme d’onda di figura 5.19.

vo2

vo1

VDD

VDD

T1

2T1

t

T1

t

vc

vx

VDD+ VT

VDD

VT

VT = VDD /2

-VT

2T1

T1

2T1

T1

t

2T1

t

-VT

-VDD

figura 5.19

L’ipotesi fatta sta anche ad indicare che nel medesimo istante la tensione di ingresso del

primo gate vx e' pari a VT. Poiche’ immediatamente prima della commutazione vo2 = 0, la tensione

ai capi di C in queste condizioni e’ 0 data da:

v c = v x − v o2 =

206

VDD

− 0 = VT

2

Capitolo V

Comparatori, multivibratori e bistabili.

Immediatamente dopo la commutazione vo1 = 0 e vo2 =VDD. Di conseguenza, poiche’ vc non

puo’ variare istantaneamente, la tensione vx passa al valore VT + VDD. In queste condizioni la tensione ai capi del condensatore, essendo vo1 = 0 e vo2 = VDD, tende esponenzialmente al valore –

VDD con costante di tempo RC.

t

−

v c (t ) = VT − (VDD + VT ).1 − e RC

La tensione vx evolvera’ quindi a partire dal valore iniziale VDD + VT verso 0 con la medesima costante di tempo.

t

t

−

−

v x = vo 2 + v c = VDD + VT − (VDD + VT ).1 − e RC = (VDD + VT ).1 − e RC

Nell’istante T1 in cui vx raggiunge il valore VT, la prima porta commuta nuovamente riportando la sua uscita al valore VDD e facendo di conseguenza passare l’uscita vo2 nuovamente a 0. Per

le medesime ragioni gia’ viste in precedenza la tensione vx si porta al valore VT – VDD e la tensione

vc tende, a partire da quest’istante, al valore VDD con costante di tempo RC. La stessa cosa avviene

ovviamente per vx e al tempo T2, quando vx raggiunge nuovamente il valore VT, si ha una nuova

commutazione che riporta il circuito nelle condizioni iniziali, chiudendo il ciclo.

I due semiperiodi, T1 e T2, possono venir facilmente determinati tenendo presente che nel

primo semiperiodo

v x = (VDD − VT ).e

−

T

RC

Imponendo pertanto che al tempo T1 vx = VT e risolvendo rispetto T1 si ottiene:

T1 = R.C. ln

VDD − VT

VT

Nel secondo semiperiodo

v x = VDD + (VT − 2.VDD ).e

e poiche’ ancora al tempo T2 vx = VT si ottiene

T2 = R.C. ln

VT − 2.VDD

VT − VDD

207

−

t

RC

Capitolo V

Comparatori, multivibratori e bistabili.

Nella realta’ tuttavia si limita l’escursione di vx tra 0 e VDD per ragioni di sicurezza utilizzando diodi di protezione. In tal caso:

T1 = R.C. ln

T2 = R.C. ln

VDD

VT

VDD

VDD − VT

Se poi VT, come precedentemente gia’ ipotizzato, risulta pari a VDD/2 si ottiene finalmente:

T1 = T2 = R.C. ln 2 = 0,693.R.C

T = T1 + T2 = 1,39.R.C

Il circuito puo’ evidentemente produrre anche forme d’onda a duty cycle variabile, agendo sul

valore di VDD o VT in modo che VT ≠ VDD/2, o in alternativa utilizzando il circuito di figura 5.20,

che permette di caricare e scaricare il condensatore C con due costanti di tempo diverse.

vx

vo1

vo2

R1

R2

figura 5.20

208

C