Amplificatori

Sample and Hold

(Appunti forniti dal prof. Pasquale Daponte)

INDICE

1. PRINCIPI OPERATIVI DI UN SAMPLE AND HOLD (SHA) AMPLIFER IDEALE ................ 2

2. PRINCIPALI PARAMETRI CHE CARATTERIZZANO LE PRESTAZIONI DI UN SHA REALE. 5

2.1 Modo track........................................................................................................... 6

2.2 Transizione track a hold ..................................................................................... 7

2.3 Modo hold.......................................................................................................... 11

2.4 Transizione hold-to-sample............................................................................... 13

2.5 Modo sample...................................................................................................... 17

3. ALCUNE STRUTTURE CIRCUITALI CHE PERMETTONO DI REALIZZARE UN SHA. ....... 18

3.1 Configurazione in cascata ................................................................................ 19

3.2 Configurazione in retroazione .......................................................................... 20

3.3 SHA con integratore.......................................................................................... 22

3.4 TRANSIZIONE SAMPLE→HOLD (S→H).................................................... 24

4. APPLICAZIONI .......................................................................................................... 24

5. SHA SELETTIVI E USATI ........................................................................................... 27

1

AMPLIFICATORI SAMPLE AND HOLD

1. Principi operativi di un Sample and Hold (SHA) Amplifer ideale

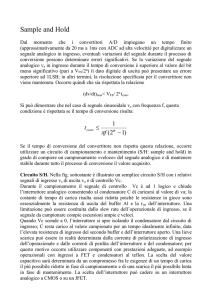

Per eseguire correttamente una conversione analogica/numerica (A/D) la tensione

all’ingresso (Vx) del convertitore analogico/numerico (ADC) deve rimanere costante per

tutta la durata TADC della conversione stessa. Affinché si verifichi ciò è necessario :

Fmax << 1/ TADC

(1.1)

con Fmax corrispondente alla massima frequenza presente nel segnale analogico da

acquisire.

In tal caso il segnale può essere ritenuto con buona approssimazione costante durante

l’intera durata della conversione.

Se la 1.1 non è soddisfatta si deve impiegare un circuito che campioni la Vx in istanti di

tempo prefissati e mantenga il valore campionato per tutto il tempo necessario affinché

l’ADC posto a valle di esso esegua la conversione.

Tale circuito prende il nome di amplificatore Sample and Hold (SHA), letteralmente

“campionatore a tratti”. Il corrispondente schema a blocchi è illustrato in Fig.1a.

Un SHA ideale presenta due modi di funzionamento: il modo sample (livello logico 1) e

il modo hold (livello logico 0). Applicando dall’esterno un segnale binario all’ingresso

di controllo si può comandare la transizione da un modo di funzionamento all’altro.

In Fig. 1b sono riportati il segnale di ingresso (Vx) e quello di uscita (Vy) di un SHA

ideale. Nella fig. 1c è invece riportato il corrispondente ingresso di controllo (VC).

Durante il modo sample la tensione di uscita Vy

riproduce esattamente quella di

ingresso Vx, di solito con guadagno unitario. Nel modo hold, invece, l’uscita mantiene

il valore che aveva all’istante in cui è avvenuta la transizione dal modo sample a quello

hold ; questo valore è mantenuto finché non viene dato un successivo comando di

sample. È durante l’intervallo di hold che l’ADC posto in cascata al SHA esegue la

conversione.

2

Fig. 1. Schema di principio di un SHA (a); confronto tra i segnali applicati all’ingresso

e all’uscita in un SHA ideale (b) ; andamento temporale del corrispondente segnale

binario di controllo (c).

Più precisamente il circuito campionatore viene detto sample-and-hold se è costruito in

modo tale che l’intervallo di sample sia una piccola frazione di quello di hold; quando si

verifica la condizione opposta, invece, il circuito prende il nome di track-and-hold

(THA).

Spesso, comunque, viene utilizzato il nome generico di SHA per indicare entrambi

questi circuiti.

Le due diverse modalità di funzionamento sono poste in evidenza in Fig.2.

Fig.2. Modalità di funzionamento di un track-and-hold e un sample-and-hold.

3

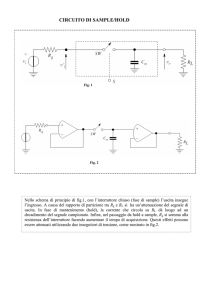

I componenti fondamentali di un SHA sono schematizzati in Fig.3. Da un punto di vista

di principio, infatti, un SHA è costituito da un interruttore comandato e da un

condensatore, il quale memorizza il valore assunto dal segnale di ingresso all’istante in

cui l’interruttore I viene aperto (istante di campionamento).

La capacità Ch svolge quindi la funzione di memoria temporanea (hold) della tensione

da convertire.

In un track-and-hold l’interruttore I è normalmente chiuso, mentre in un sample-andhold è chiuso solamente durante il breve intervallo di tempo necessario ad acquisire il

segnale di ingresso.

Fig. 3. Componenti fondamentali di un SHA.

4

2. Principali parametri che caratterizzano le prestazioni di un SHA reale

Tutti i dispositivi SHA hanno quattro componenti principali: l’amplificatore di ingresso,

il dispositivo a immagazzinamento di energia (condensatore per la fase hold), il buffer

di uscita, i circuiti di interruzione (switch) (Fig. 4).

Fig.4. Struttura di base di un amplificatore sample-and-hold.

Il dispositivo a immagazzinamento di energia (il cuore di un SHA) è quasi sempre un

condensatore. L’amplificatore

di ingresso memorizza l’ingresso presentando una

elevata impedenza alla sorgente di segnale e fornendo un guadagno di corrente per

caricare il condensatore di hold..

Nel modo track, il condensatore di hold di solito determina la risposta in frequenza del

dispositivo; nel modo hold il condensatore conserva la tensione esistente prima che sia

disconnesso dal buffer di ingresso. Il buffer di uscita offre un elevata impedenza al

condensatore di hold per conservare la tensione determinata dalla scarica

prematuramente. Il circuito di interruzione e il suo driver costituiscono il meccanismo

attraverso cui il condensatore di hold è alternativamente posto dalla fase di sample alla

fase di hold.

Il termine sample and hold implica che il dispositivo campioni l’ingresso per un breve

periodo e stia in modo hold per la durata del ciclo di lavoro.

Un track and hold trascorre la maggior parte del tempo seguendo l’ingresso ed è posto

in modo hold solo per un breve intervallo.

5

Nei sistemi di acquisizione dati che operano a velocità elevate(superiori a 1MHz) i

termini

sample and hold e track and hold perdono la loro distinzione.

Per descrivere metrologicamente il comportamento di un SHA reale è necessario fornire

le caratteristiche statiche e dinamiche per ciascuno dei due modi di funzionamento e per

le transizioni da un modo all’altro. Saranno ora presi in esame i principali parametri che

consentono tale descrizione.

2.1 Modo track

Poiché in questo caso il SHA è semplicemente un amplificatore ad ampiezza di banda

limitata che può o non può fornire guadagno, le sue caratteristiche sono le stesse di un

amplificatore analogico.

Si ricorda che un SHA può essere rappresentato con un amplificatore operazionale con

un condensatore e un interruttore.

Le principali specifiche usate per descrivere l’operazione in modo sample sono:

Offset: per segnale di ingresso nullo , esso rappresenta l’estensione di cui l’uscita devia

dallo zero, nel tempo ed al variare della temperatura;

Non linearità: la quantità di cui il grafico dell’uscita in funzione dell’ingresso devia

dalla ‘linea retta ottimale’. Di solito è specificato come percentuale del fondo scala del

SHA;

Tempo di assestamento: il tempo richiesto affinché l’uscita si assesti al suo valore

finale entro la banda di errore ossia entro una frazione fissata del fondo scala quando è

applicato un gradino analogico in ingresso (da 0 a ±FS, -FS a +FS, o da +FS a –FS);

Guadagno: il fattore di moltiplicazione rappresentante la funzione di trasferimento

ingresso/uscita in continua;

Ampiezza di banda: descrive la risposta in frequenza in termini di attenuazione

dell’uscita, di solito è caratterizzato dal valore a 3dB;

Velocità di deviazione: la massima velocità di cambiamento della tensione di uscita

quando è applicato un gradino analogico sia come gradino iniziale che come una

transizione hold a sample;

6

2.2 Transizione track a hold

I principali parametri forniti per descrivere le prestazioni del SHA durante questa fase di

transizione sono:

Tempo di apertura: rappresenta l’intervallo di tempo tra l’istante in cui viene fornito

all’ingresso di controllo il comando di hold e l’istante in cui avviene l’effettiva apertura

dell’interruttore, come illustrato in Fig. 5.

Figura 5. Specifiche durante la fase di transizione S→H

In realtà, per circuiti aventi la stessa sigla commerciale, il tempo di apertura varia al

variare dello specifico dispositivo considerato. Per un dato dispositivo, inoltre, esso

varia da un’operazione di campionamento all’altra: quest’ultima fluttuazione aleatoria

dell’istante di campionamento prende il nome di Jitter di apertura Tj (aperture Jitter).

L’effettivo tempo di apertura Tap è dato pertanto dalla somma del ritardo normale di

apertura Tap e dell’incertezza ∆Tap sull’effettivo istante di apertura dell’interruttore,

dovuta sia allo specifico componente, sia al Jitter temporale. Si ha cioè:

Tap = Tap + ∆ Tap

Il ritardo Tap tra l’effettivo istante di campionamento e l’istante di comando può quindi

essere in parte compensato anticipando il segnale di comando dal valore nominale Tap,

rispetto all’istante in cui si desidera campionare il segnale. Nelle applicazioni in cui non

interessa la relazione temporale tra il segnale di ingresso e gli istanti di campionamento,

ma solamente la costanza dell’intervallo di tempo tra questi ultimi, il ritardo nominale

7

Tp e la componente dell’incertezza di apertura dovuta allo specifico componente,

essendo costanti, perdono interesse.

Ciò accade quando si desidera stimare l’autocorrelazione o lo spettro (di ampiezza) di

un segnale.

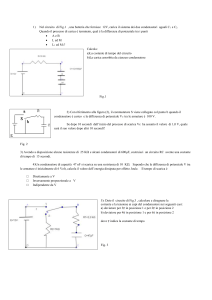

Esempio:

Supposto che il segnale da campionare presenti una variazione massima pari a 1 V/µs, e

che il SHA abbia una incertezza di apertura inferiore a ±10 ns, l’incertezza sul valore

campionato è inferiore a ±1 V/µs ⋅ 10 ns = 10 mV. Se il valore della tensione di fondo

scala è pari 5 V, l’accuratezza del SHA è pertanto superiore allo 0.2%.

Offset da sample a hold (Pedestal): c’è un errore di gradino che fa si’ che il valore

ottenuto sia differente dall’ultimo valore nel campione ; esso è causato dalla carica

scaricata sul condensatore hold attraverso una capacità di dispersione dal circuito

switch- control.

L’obiettivo del progetto è gestire l’errore dovuto ad un switch non ideale indipendente

dal livello del segnale di ingresso; la misura di cui devia da una costante in tutto il

range del segnale di ingresso può risultare in non linearità nell’uscita rispetto al segnale

di ingresso.

La porzione costante d’offset dell’errore chiamata trasferimento di carica (passo

d’offset) può essere compensata accoppiando un segnale di fase opposta sul

condensatore hold attraverso un circuito switching ausiliare e un condensatore di

compensazione.

Così il sample to hold (Pedestal), dipendono dalla configurazione del dispositivo reale.

Per SHA aventi condensatori hold interni fissi esso include il gradino residuo incorretto

e la nonlinearità offset.

Per i circuiti SHA integrati, richiedenti condensatori esterni, il pedestal è l’errore di

gradino residuo dopo che è stato influenzato il trasferimento di carica per essere

cancellato.

.In un dispositivo in cui il condensatore può essere scelto dall’utente questi effetti

possono essere ridotti aumentando in proporzione la capacità. Tutto ciò, però, si

ottiene al prezzo dell’aumento del tempo di acquisizione.

8

Tempo di assestamento (setting time Ts) , ossia il tempo richiesto, dall’istante di

apertura dell’interruttore, affinché l’uscita raggiunga il valore finale entro una frazione

specifica del fondo scala;

Ritardo di apertura (o più precisamente Tempo effettivo di ritardo dell’apertura ):

questa caratteristica è importante perché aiuta l’utente SHA a sapere quando bloccare il

dispositivo rispetto alla sincronizzazione del segnale di ingresso. La Fig. 6 mostra la

sequenza di ciò che accade quando il comando hold è applicato con un segnale di

ingresso di pendenza arbitraria (per semplicità l’errore di offset SHA ed il transitorio di

apertura dell’interruttore sono stati ignorati).

Il valore che infine si ottiene è una versione ritardata del segnale di ingresso, mediata

sul tempo di apertura dell’interruttore.

L’effettivo tempo di ritardo di apertura è definito come l’intervallo tra il fronte di salita

del comando di hold e l’istante in cui il segnale di input è uguale al valore calcolato.

Questa caratteristica è più utile del tempo di apertura stesso, perché include gli effetti

del ritardo di propagazione digitale e analogico, così come il tempo di apertura.

Fig. 6. Errori introdotti dal SHA in fase di apertura

La formula in Fig. 6 è basata sull’ipotesi che il valore di tensione ai capi del

condensatore di hold è approssimativamente uguale al valore medio del segnale

applicato ai capi dello switch nell’intervallo durante il quale lo switch cambia da una

bassa ad un’alta impedenza (tempo di apertura);

9

Jitter (incertezza di apertura): è il risultato del rumore che modula la fase del

comando hold.

Il Jitter si manifesta come variazione campione-campione nel valore del segnale

analogico che è stato ‘congelato’ .

In un SHA è la variazione del tempo nell’apertura dell’interruttore di campionamento.

Inoltre è la variazione nel tempo di ritardo di apertura da campione a campione.

L’incertezza d’apertura si manifesta con un errore di apertura come mostrato in Fig.7.

L’ampiezza dell’errore è correlata alla velocità di cambio dell’ingresso analogico. Per

ogni assegnato valore dell’incertezza di apertura, l’errore di apertura aumenterà come

l’ingresso aumenta la derivata del segnale in ingresso al SHA;

Switching Transient: come mostrato in Fig.7 la maggior parte delle caratteristiche di

un SHA include l’ampiezza massima e la durata del transitorio che appare all’uscita

come risultato della transizione sample-to-hold.

Un transitorio simile appare anche durante la transizione hold-to-sample, ma è di solito

non rilevante, a causa dell’effetto dominante del tempo di acquisizione.

Switch Delay Time (tempo di ritardo dello switch): l’intervallo tra i fronti del

comando hold e l’inizio del cambiamento dello stato all’uscita analogica del SHA.

Questo ritardo come mostrato in Fig.7 avviene per entrambe le transizioni sample-tohold e hold-to-sample.

Fig.7. Incertezza nell’istante di apertura.

10

2.3 Modo hold

Durante il modo hold la tensione di uscita dovrebbe essere costante. Lo scostamento da

tale situazione ideale è dovuto essenzialmente a due fenomeni: il feedthrough e il droop,

entrambi evidenziati in fig. 8.

Fig 8 Feedthrough e droop durante il modo hold

Droop (abbassamento) La rapidità di variazione (droop rate DR) della tensione di

uscita è legata al fatto che il condensatore di hold non è chiuso su una resistenza infinita

e, quindi, si scarica, sia pure lentamente. Tale resistenza è dovuta alle correnti di

dispersione attraverso l’interruttore a FET e alla corrente di bias dell’amplificatore di

uscita. La polarità del droop dipende dal verso delle correnti di dispersione; comunque,

se il SHA è ben progettato, ha influenza rilevante solamente la corrente attraverso

l’interruttore. Poiché per una data corrente di dispersione Id attraverso il condensatore si

ha un droop rate pari a:

dVy/dt = Id/ Ch

ne consegue che la variazione della tensione in uscita dal SHA può essere ridotta

adottando elevati valori di capacità: un elevato valore di Ch limita però la velocità di

carica del condensatore durante il modo sample. In pratica, pertanto, il valore di Ch è

fissato dal costruttore in modo da ottimizzare le prestazioni del SHA in date condizioni

di funzionamento. In alcuni SHA, comunque, il costruttore lascia all’utilizzatore la

libertà di scegliere il valore più opportuno della capacità; in questi casi, nelle specifiche

11

il droop rate è definito mediante la corrente di dispersione Id anziché mediante il valore

di dVy/dt. Ad esempio si supponga che il SHA in esame abbia una corrente di

dispersione pari a 10 pA a 20°C; se si desidera ottenere un droop rate massimo di 5

mV/S, si deve scegliere Ch =[Id/(dVy/dt)]≥2nF

Feedthrough: Il feedthrough (FT) è la frazione del segnale di ingresso che appare in

uscita quando l’interruttore è aperto. Esso è dovuto essenzialmente alla capacità

parassita che esiste tra i due terminali dell’interruttore aperto, di solito realizzato con

transistor a effetto di campo (FET) aventi il gate collegato all’ingresso di controllo.

Vengono spesso forniti valori di relazione di feedthrough a varie frequenze; questi

valori sono ottenuti applicando all’ingresso un’onda sinusoidale a una data frequenza e

di ampiezza pari al fondo scala. Si possono ad esempio avere relazioni pari a –90db a

basse frequenze e a –60dB ad alte frequenze (MHz).

Assorbimento dielettrico: la tendenza delle cariche entro un condensatore a

ridistribuirsi in un periodo di tempo, risultante in un salto (“creep”) ad un nuovo livello

quando è permesso riposarsi dopo cambiamenti larghi e veloci..

12

2.4 Transizione hold-to-sample

Per descrivere le prestazione del SHA durante questa fase di transizione viene utilizzato

un unico parametro:

-

il tempo di acquisizione Tacq è definito come l’intervallo di tempo tra l’istante in cui

l’ingresso di controllo passa da Hold a Sample e l’istante in cui l’uscita raggiunge

una frazione specifica del segnale di ingresso (Fig. 9); il caso peggiore si manifesta

quando il segnale di ingresso consiste in un gradino di ampiezza pari al fondo scala.

Fig. 9 Tempo di acquisizione.

Il tempo di acquisizione rappresenta pertanto un limite inferiore al tempo in cui il

segnale di ingresso deve essere applicato al SHA affinché il valore ottenuto in uscita

abbia una prefissata accuratezza. Esso è dovuto essenzialmente a tre cause:

-

il ritardo nella chiusura dell’interruttore (Ti);

-

il ritardo legato allo slow-rate degli amplificatori e alla velocità di carica del

condensatore (Tq) di hold, il quale dipende dalla variazione della tensione di uscita;

-

il tempo di assestamento (ts) che dipende anch’esso dalla variazione della tensione

di uscita.

13

Se Rs è la resistenza vista dal condensatore di hold quando l’interruttore è chiuso, la

tensione Vy ai capi di tale condensatore quando la tensione d’ingresso varia a gradino è

data da:

Vy(t)=V∞ - ∆V exp(-t / Rs Ch)

Dove V∞ rappresenta il valore a regime e ∆V è l’ampiezza del gradino. Il tempo

richiesto per caricare il condensatore alla tensione (1-p)V∞ è pertanto pari a:

Tq= -RsCh * Ln( p * abs(V∞/∆V) )

In particolare se si suppone che il condensatore sia inizialmente scarico si ha ∆V= -V∞,

per cui si ottiene :

Tq = - Rs Ch * Ln( p)

Che fornisce

4.6 Rs Ch p=1%

Tq =

6.9 Rs Ch p=0.1%

Si definisce efficienza η di un SHA il rapporto fra la tensione ai capi di Ch all’istante di

apertura dell’interruttore I e la tensione di ingresso, ossia:

η = 1-p = 1-exp (-Tq / Rs Ch)

14

Per aumentare η si deve ridurre la costante di tempo di carica RsCh, o aumentere il

tempo Tq di chiusura dell’interruttore. Si noti però che, una volta minimizzato il valore

di Rs, la prima soluzione richiede una riduzione di Ch, la quale comporta un aumento del

droop rate durante la fase di hold. La seconda soluzione invece richiedendo un aumento

della durata della fase di sample, comporta una riduzione del segnale di ingresso.

In prima approssimazione si può supporre che, fissata l’accuratezza p con cui il valore

finale deve essere acquisito, anche il tempo di acquisizione Tacq sia proporzionale a

RsCh:

Tacq= Kacq Rs Ch

Una rozza figura di merito per un SHA e pertanto data dal prodotto:

ß ≅ droop * Tacq = (Id/ Ch) Kacq Rs Ch = Kacq RsId

Si ricorda infine che, durante le transizioni possono apparire dei fenomeni transitori

causati da squilibri dinamici all’interno del SHA o da accoppiamenti capacitivi con il

segnale di controllo. In Fig.10 sono riportate le principali caratteristiche dinamiche di

un SHA.

Figura10. Caratteristiche dinamiche di un SHA

15

La massima velocità di campionamento di un SHA è limitata dalla somma di un

intervallo di tempo richiesta per il modo Sample and Hold. L’intervallo trascorso nel

modo hold (dopo che il transitorio si è stabilizzato) è soprattutto determinato dal sistema

in cui un SHA è usato. Il tempo minimo trascorso nel modo sample comunque è

determinato dal tempo di acquisizione sample-hold per un dato grado di accuratezza.

Quando il tempo di acquisizione è misurato come l’intervallo dalla transizione holdsample all’istante in cui il buffer di uscita si è stabilizzato, il valore risultante del tempo

di acquisizione è generalmente pessimistico. Come definito il tempo di acquisizione

misura il tempo richiesto per acquisire il segnale al condensatore di hold non

necessariamente all’uscita del buffer (nonostante essi siano gli stessi). Per i dispositivi

in cui il condensatore di hold è memorizzato da un inseguitore, piuttosto che usato come

un integratore, la misura dell’uscita include il buffer di uscita (fissato il tempo così

come il tempo di ritardo dello switch). In pratica la tensione è stata già fissata dal

condensatore hold, ed un comando hold può essere applicato prima che il buffer di

uscita si sia stabilizzato completamente. La Fig 11 illustra

un metodo per la

determinazione del tempo di acquisizione che è indipendente dagli effetti del buffer di

uscita. L’onda quadra analogica in ingresso è campionata e convertita ad una frequenza

doppia dell’onda quadra analogica con impulsi sample strettamente vicini. Per una

transizione a Sample la figura indica che l’uscita incomincia a cambiare in modo da

seguire il gradino iniziale.

Inizialmente (fissata l’ampiezza sufficiente per acquisire il segnale accuratamente)

l’ampiezza dell’impulso taq è ridotta fino a che il segnale di uscita, misurato

digitalmente, cominci a collassare per qualche percentuale definita del fondo scala.

Quando ciò accade l’ampiezza dell’impulso è uguale al tempo di acquisizione, perché il

condensatore hold di non può acquisire più a lungo il segnale in maniera accurata con

un ulteriore riduzione di taq .

Fig. 11. Determinazione del tempo di acquisizione

16

2.5 Modo sample

Durante la fase di campionamento, una volta terminato il transitorio, il SHA è

semplicemente un amplificatore inseguitore, la cui caratteristica di trasferimento

dovrebbe essere una retta passante per l’origine e pendenza unitaria. Per indicare gli

scostamenti dalla idealità vengono fornite le seguenti specifiche di tipo statico, che

sono riportate in fig.12(a):

-

la tensione di offset in uscita, ossia la tensione con ingresso nullo e la sua

dipendenza dal tempo e dalla temperatura;

-

la non linearità della caratteristica di trasferimento statica, di solito fornita mediante

il massimo scostamento tra la retta che “meglio” approssima tale caratteristica e la

caratteristica stessa;

-

lo scostamento di guadagno, ossia il valore del coefficiente angolare della retta

approssimante la caratteristica di trasferimento.

Tali caratteristiche sono dovute a imperfezioni dell’interruttore e degli amplificatori di

ingresso e uscita; per la loro compensazione sono talvolta previsti adeguati circuiti.

Figura 12. Specifiche statiche di un SHA durante la fase sample.

Vengono inoltre fornite le caratteristiche di tipo dinamico tipiche degli amplificatori

inseguitori, come ad esempio:

-

la banda passante sia per piccoli segnali, sia per grandi segnali. Infatti, se Rs

rappresenta la resistenza vista dal condensatore di hold quando l’interruttore I è

chiuso, nella fase di sample la cella Rs Ch funziona da filtro passa basso, limitando

17

in tal modo la frequenza massima della tensione di ingresso. D’altra parte, poiché

per garantire la costanza della tensione di uscita durante la fase di hold non è

possibile ridurre a valori troppo bassi la capacità Ch, per aumentare la frequenza di

taglio di tale filtro è necessario che Rs assuma valori ridotti;

-

il ritardo di fase (phase shift), ossia lo sfasamento tra la tensione di uscita e quello di

ingresso;

-

lo slow-rate (SR), ossia la massima rapidità di variazioni dell’ uscita;

-

il tempo di assestamento (setting time Ts), ossia il tempo richiesto affinché l’uscita

raggiunga una frazione specificata dal valore di regime quando all’ingresso è

applicato un gradino di tensione di ampiezza specificata, come mostrato in fig. 12

(b).

3. Alcune strutture circuitali che permettono di realizzare un SHA.

I circuiti SHA possono essere a ciclo chiuso o aperto. I primi utilizzano l’accuratezza,

bassa deriva, e flessibilità di guadagno adatti all’amplificatore operazionale. I secondi

traggono vantaggio dalle caratteristiche di elevata velocità degli amplificatori buffer a

guadagno unitario.

Fig 13 .SHA structure-simple follower

Un SHA ideale dovrebbe riprodurre in uscita il segnale di ingresso senza incertezze,

avere tempi di transizione nulli, ed essere in grado di mantenere in uscita il valore

campionato per un tempo infinito. Poiché in pratica ciò può essere ottenuto solamente

con un certo grado di approssimazione,

è importante specificare come e di quanto il comportamento del circuito reale si scosta

da quello del circuito ideale .

18

Nella modalità sample la capacità Ch del SHA si carica attraverso la resistenza Rs della

sorgente.

Per ottenere una carica veloce del condensatore, ossia una veloce acquisizione del

segnale, la costante di tempo di carica RsCh deve essere ridotta; pertanto, sia Rs che Ch

devono risultare molto piccole.

Sempre nella fase di sample, una volta a regime, il circuito si comporta come un filtro

passa-basso con pulsazione di taglio ωo=1/(RsCh); affinché la tensione ai capi del

condensatore riproduca fedelmente la tensione di ingresso, è necessario che ωo sia

sufficientemente maggiore della banda del segnale di ingresso. Anche in questo caso si

evince che sia Rs, sia Ch devono essere molto piccole.

Al contrario, per mantenere costante la tensione ai capi del condensatore durante il

modo hold, è necessario realizzare elevate costanti di tempo di scarica. Se RL

rappresenta il parallelo fra la resistenza di carico e quella connessa a tutte le perdite del

condensatore, tale costante di tempo vale RLCh Per mantenere costante il segnale di

uscita è quindi necessari massimizzare il prodotto RLCh; ciò richiede l’impiego di

elevare resistenze di carico e di condensatori di elevata capacità. Si noti, in particolare,

che la condizione sul valore della capacità è opposta a quella richiesta nella fase di

sample. Gli schemi circuitali impiegati per realizzare un SHA devono pertanto rendere

minima la resistenza Rs: per la capacità Ch si adotta invece una soluzione di

compromesso scelta in base alle prestazioni desiderate. La struttura del circuito varia

inoltre a seconda che il principale obiettivo da raggiungere sia la velocità oppure

l’accuratezza o infine una soluzione di compromesso.

3.1 Configurazione in cascata

L’ingresso e l’uscita sono isolati dall’interruttore e dalla capacità di memoria mediante

due inseguitori di tensione, spesso aventi lo stadio di ingresso a FET, come mostrato in

Fig.14.

19

Fig 14. Configurazione in cascata

L’amplificatore di ingresso consente di ridurre la resistenza Rs vista dal condensatore

quando l’interruttore è chiuso; ciò è utile specialmente nei casi in cui la sorgente di

segnale ha un’impedenza elevata.

A causa delle imperfezioni degli amplificatori, questo tipo di realizzazione, pur

consentendo elevate velocità, è poco accurata.

In particolare, le tensioni di offset dei due amplificatori in cascata si sommano tra loro

causando uno scostamento sull’uscita.

3.2 Configurazione in retroazione

Quando è richiesta un’elevata precisione, sia pure a scapito della velocità, conviene

adottare uno schema a retroazione del tipo rappresentato in Fig. 15. In questo tipo di

realizzazione l’effetto sull’uscita delle tensioni di offset degli amplificatori e dei rumori

di

modo

comune

viene

notevolmente

ridotto.

Purtroppo

il

miglioramento

dell’accuratezza del dispositivo avviene a scapito di un aumento del tempo richiesto per

la carica della capacità. Durante il modo hold, l’amplificatore d’ingresso è saturato in

quanto mentre all’ingresso invertente è applicata la tensione costante presente all’uscita,

all’ingresso non invertente è applicato il segnale variabile da campionare. Durante la

fase di sample successiva l’amplificatore richiederà un certo tempo per uscire dalla

saturazione, con una conseguente riduzione della velocità del componente rispetto alla

realizzazione a catena aperta.

20

Fig.15. Configurazione in retroazione.

La saturazione può essere prevenuta impiegando il circuito di Fig. 16 che presenta oltre

all’interruttore I altri due interruttori. In questo caso se durante il modo hold viene

chiuso I1 e aperto I2 l’amplificatore d’ingresso può essere sconnesso dl circuito

prevenendo così la sua saturazione. Durante la fase di hold, pertanto, il funzionamento

di questa struttura è simile a quello del circuito di Fig. 14; nella fase di sample, invece il

circuito di Fig. 16 si comporta in modo simile a quello di fig. 15.

Fig. 16. Schema per la prevenzione della saturazione nell’amplificatore di ingresso con

l’ impiego di due interruttori

In Fig.17 è mostrato un altro circuito che consente di evitate la saturazione

dell’amplificatore di ingresso impegnando due diodi. Durante la fase di sample l’intero

circuito si comporta come un inseguitore. I due diodi non conducono in quanto la

tensione ai loro morsetti è inferiore alla tensione di soglia. Quando l’interruttore viene

aperto, uno dei due diodi è senz’altro in conduzione, pertanto la maglia di retroazione

dell’amplificatore di ingresso viene chiusa. La resistenza R è impiegata per l’imitare la

21

corrente sulla maglia di retroazione dovuta alla d.d.p. tra l’uscita e l’ingresso, che viene

vista come un carico dell’amplificatore di uscita.

Fig. 17. Prevenzione della saturazione nell’amplificatore di ingresso con l’ impiego di

due diodi.

3.3 SHA con integratore

Invece di utilizzare un condensatore collegato a massa seguito da un inseguitore di

tensione, è possibile impiegare come elemento di memorizzazione un inseguitore come

illustrato in Fig. 18. In questo caso l’interruttore lavora al potenziale di massa. Durante

la fase di sample l’intero circuito si comporta sempre come un inseguitore. Durante la

fase di hold, però, l’amplificatore di ingresso è saturo.

Fig. 18. SHA con integratore.

22

La saturazione dell’amplificatore d’ingresso del circuito di Fig. 18 può comunque

essere evitata adottando lo schema di Fig. 19. Durante la fase di sample tale circuito si

comporta come un inseguitore in cascata con un integratore e presenta una risposta in

frequenza pari a:

G(ω ) = −

1

(1 + jωRCh )

Pertanto, se la frequenza del segnale di ingresso è sufficientemente minore di 1/(2RCh)

l’intero circuito si comporta come un semplice inseguitore. Questo tipo di schema

consente di realizzare SHA molto veloci.

Fig. 19. SHA con integratore e prevenzione della saturazione nell’amplificatore di

ingresso.

23

3.4 TRANSIZIONE SAMPLE→HOLD (S→H)

-

l’offset di carica ∆Q è dovuto alla frazione di carica del componente di memoria Ch

che viene immagazzinata nelle capacità parassite Cl dell’interruttore a causa

dell’apertura di quest’ultimo. In prima approssimazione si può porre

∆Q = Vy (Cl/Ch)

4. Applicazioni

Senza dubbio il principale uso degli SHA è in testa ai convertitori analogico digitali. Il

tempo di apertura, in un sistema a conversione A/D differisce dalla caratteristica del

SHA.

In una conversione A/D, il tempo di apertura si riferisce al periodo di tempo in cui

l’ingresso analogico deve rimanere stabile in maniera tale che avvenga una conversione

accurata . E’ questo intervallo che limita l’ampiezza analogica (massimo dV/dt) del

convertitore A/D.

Lo scopo del SHA è di fatto ridurre il tempo di apertura del convertitore A/D.

Mantenendo l’ingresso analogico cambiato rapidamente per il periodo richiesto

dall’ADC, l’ampiezza di banda del sistema può essere aumentata sostanzialmente. In

aggiunta, accuratezza linearità – anche di segnali a bassa frequenza – sono migliorate.

La maggior parte dei convertitori A/D a successive approssimazioni e dei convertitori

A/D di tipo subranging richiedono un SHA per tutto ma con ampiezze analogiche più

basse. Per questo motivo alcuni convertitori sono offerti con gli SHA incorporati nel

progetto. Questo rende capace il progettista del sistema a creare una combinazione

ADC-SHA in cui la sincronizzazione è stata già ottimizzata per la migliori prestazioni.

Dall’altro lato molti convertitori A/D, tipicamente flash, offrono tempi di apertura

estremamente bassi; l’inclusione di un SHA con tali dispositivi può migliorare le

prestazioni ad alta frequenza ma può degradare quelle a bassa frequenza a causa

dell’abbassamento associato con i capacitori necessariamente più piccoli.

24

I circuiti sample-hold vengono inoltre, largamente usati nei sistemi di acquisizione dati

come mostrato in Fig.20.

Fig. 20. Schema a blocchi di un sistema di acquisizione impiegante un SHA

Il sample hold mantiene costante l’ingresso al convertitore A/D durante l’intervallo di

conversione. Intanto il multiplexer collega la sua uscita al canale da convertire. Questa

operazione può avvenire sia randomaticamente che sequenzialmente. Non appena la

conversione è terminata, il sample-hold campiona il nuovo ingresso e il ciclo si ripete.

Questo modo di operare è conosciuto come campionamento sincrono; il sample-hold

opera in sincronia con diversi elementi di sistemi.

Nel modo asincrono un largo numero di sample-hold può essere usato per acquisire e

memorizzare dati a velocità pertinenti ad ogni singolo canale . Essi sono allora o

interrogati dai multiplexers analogici, o i segnali sono convertiti in maniera asincrona

singolarmente, e allora moltiplicati digitalmente.

In una distribuzione di dati, lo 0.01% dei sample-hold è meno costoso del più ampio

numero di convertitori D/A che hanno accuratezza paragonabile. Un tipico sistema di

distribuzione dati è mostrato in Fig. 21.

Un convertitore D/A veloce ed accurato aggiorna un numero di sample-hold ad una

velocità e a un livello di accuratezza appropriato ai singoli canali.

25

Fig. 21 Schema a blocchi di un sistema di generazione di segnale con l’ausilio di SHA.

I Sample and Hold sono inoltre usati per modulare i convertitori D/A (DAC) nei sistemi

che sono sensibili alle anomalie di funzionamento dei convertitori D/A che avvengono

nei punti di transizione.

La Fig.22 mostra la tempificazione usata per evitare ia propagarsi a valle del DAC dei

suoi impulsi di commutazione (glitchs).

Poco prima di inserire i nuovi dati nel DAC l’SHA è messo nel modo hold, così che le

anomalie D/A sono separate dall’uscita. Gli SHA usati devono avere dei transitori molto

piccoli di sample to hold o hold to sample e errori pedestal, così come i tempi di

acquisizione veloci.

Fig. 22. Uso del SHA per evitare la presenza di impulsi di commutazione prodotti da

un convertitore D/A a valle del convertitore stesso.

26

Un'altra applicazione di un SHA è un rivelatore di picco. Un tipico esempio è mostrato

in Fig 23.

Quando l’ingresso è più grande dell’uscita dell’SHA, l’uscita positiva del comparatore

costringe l’SHA a inseguire l’ingresso.

Quando l’ingresso diminuisce e diviene più piccolo dell’uscita del SHA, l’uscita “0” del

comparatore costringe l’SHA a mantenere l’ingresso finchè l’ingresso diventa di nuovo

più grande dell’uscita.

Per resettare, l’input di controllo è arbitrariamente acceso in sample e un livello minore

è applicato in ingresso.

L’uscita del SHA (o l’ingresso del comparatore) è polarizzato da 5mV di isteresi per

evitare ambiguità durante gli ingressi a gradino e minimizzare falsi denti di sega

(triggering) dovuti al rumore.

Fig. 23. Schema a blocchi di un rilevatore di picco ed esempio di funzionamento.

5. SHA selettivi e usati

In un sistema di acquisizione dati, il punto dove il campione analogico è preso è spesso

il collegamento più debole, perché molti progettisti di sistema trascurano la natura

contrastante delle esigenze su entrambe le performance statiche e dinamiche.

Come esempio della varietà di SHA a disposizione, in tabella 1 si riportano le

caratteristiche di alcuni SHA.

27

In qui dispositivi che richiedono un condensatore di hold esterno, il trasferimento di

carica è dato in picocolumb (pC). L’errore di offset reale (sample-hold) è dato da:

Verror = Q/C = trasferimento di carica(pC)/capacità hold(pF)

Nello scegliere i condensatori per i dispositivi con questa opzione, l’errore pedestal è

soltanto una delle specifiche da considerare.

Il tempo di assestamento, la velocità di droop, e il tempo di acquisizione sono tutte

funzioni del condensatore di hold.

Quando si confrontano le specifiche di un SHA, si deve essere sicuri di portare in conto

le misurazioni effettuate. Per esempio, la misura del tempo di assestamento

fatta

quando si pilota un carico capacitivo grande sarà raramente cosi buona come le

specifiche definite dal produttore, basate su misure con un semplice carico resistivo. In

breve i progetti di sistema che incorporano SHA richiedono in aggiunta alcune

considerazioni sui circuiti associati e sul layout, per capire e apprezzare le specifiche del

dispositivo.

Con tutto ciò che l’utente deve considerare, fa poca meraviglia che molte fabbriche

offrono pacchetti con ADC e SHA insieme.

Questa è un’altra possibilità di scelta per i progettisti di sistema: i vantaggi di un ADC

completo con un SHA; o la flessibilità offerta dall’immensa varietà di SHA e ADC

utilizzabili singolarmente.

Tabella 1. Caratteristiche di alcuni SHA disponibili sul mercato.

28