Memory Fault Simulator

1

User’s Requirements

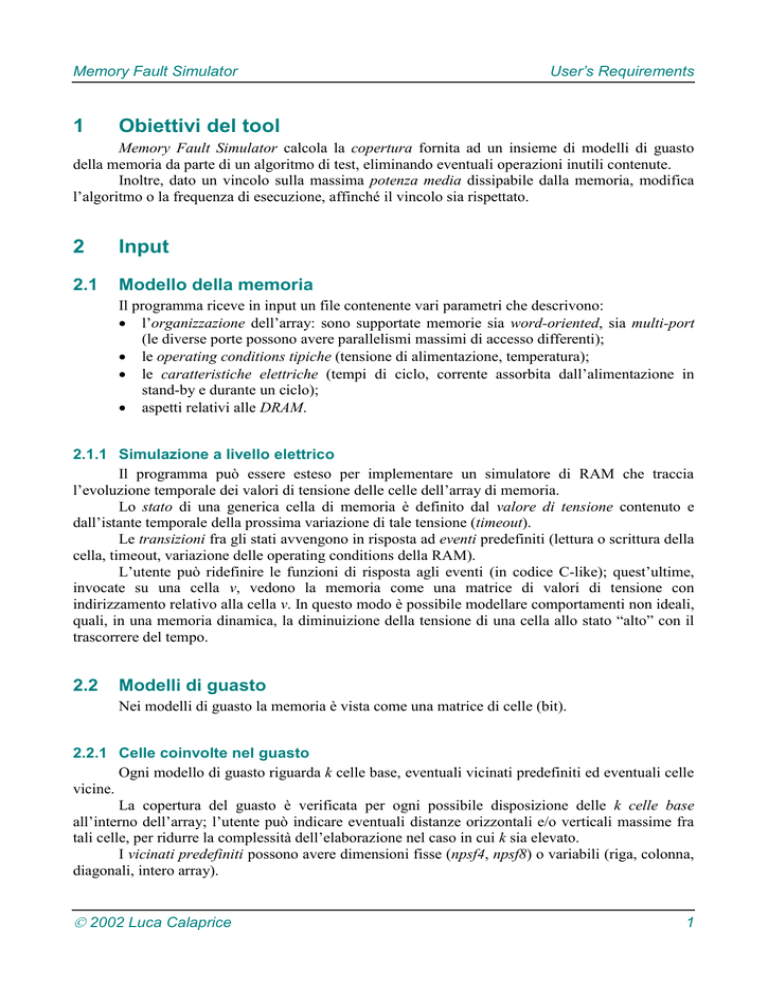

Obiettivi del tool

Memory Fault Simulator calcola la copertura fornita ad un insieme di modelli di guasto

della memoria da parte di un algoritmo di test, eliminando eventuali operazioni inutili contenute.

Inoltre, dato un vincolo sulla massima potenza media dissipabile dalla memoria, modifica

l’algoritmo o la frequenza di esecuzione, affinché il vincolo sia rispettato.

2

Input

2.1

Modello della memoria

Il programma riceve in input un file contenente vari parametri che descrivono:

l’organizzazione dell’array: sono supportate memorie sia word-oriented, sia multi-port

(le diverse porte possono avere parallelismi massimi di accesso differenti);

le operating conditions tipiche (tensione di alimentazione, temperatura);

le caratteristiche elettriche (tempi di ciclo, corrente assorbita dall’alimentazione in

stand-by e durante un ciclo);

aspetti relativi alle DRAM.

2.1.1 Simulazione a livello elettrico

Il programma può essere esteso per implementare un simulatore di RAM che traccia

l’evoluzione temporale dei valori di tensione delle celle dell’array di memoria.

Lo stato di una generica cella di memoria è definito dal valore di tensione contenuto e

dall’istante temporale della prossima variazione di tale tensione (timeout).

Le transizioni fra gli stati avvengono in risposta ad eventi predefiniti (lettura o scrittura della

cella, timeout, variazione delle operating conditions della RAM).

L’utente può ridefinire le funzioni di risposta agli eventi (in codice C-like); quest’ultime,

invocate su una cella v, vedono la memoria come una matrice di valori di tensione con

indirizzamento relativo alla cella v. In questo modo è possibile modellare comportamenti non ideali,

quali, in una memoria dinamica, la diminuizione della tensione di una cella allo stato “alto” con il

trascorrere del tempo.

2.2

Modelli di guasto

Nei modelli di guasto la memoria è vista come una matrice di celle (bit).

2.2.1 Celle coinvolte nel guasto

Ogni modello di guasto riguarda k celle base, eventuali vicinati predefiniti ed eventuali celle

vicine.

La copertura del guasto è verificata per ogni possibile disposizione delle k celle base

all’interno dell’array; l’utente può indicare eventuali distanze orizzontali e/o verticali massime fra

tali celle, per ridurre la complessità dell’elaborazione nel caso in cui k sia elevato.

I vicinati predefiniti possono avere dimensioni fisse (npsf4, npsf8) o variabili (riga, colonna,

diagonali, intero array).

2002 Luca Calaprice

1

Memory Fault Simulator

User’s Requirements

Le celle vicine sono indicate per mezzo di offset di riga e colonna rispetto alla cella base;

sono utili per modellare vicinati di dimensioni fisse definiti dall’utente.

2.2.2 Blocchi e sequenze

Un modello di guasto è un blocco; ciascun blocco contiene una o più sequenze; ciascuna

sequenza contiene una o più operazioni elementari e/o blocchi. Affinché il guasto sia rilevato è

necessario che l’algoritmo di test esegua le operazioni nell’ordine in cui compaiono nelle sequenze

di appartenenza, ma non importa l’ordine relativo di esecuzione fra sequenze di uno stesso blocco.

Per garantire il determinismo del modello di guasto, si richiede che una stessa cella non sia

indirizzata da sequenze appartenenti (anche ricorsivamente) ad uno stesso blocco.

In questo modo si possono trattare casi in cui l’ordine delle operazioni compiute su celle

diverse può essere qualunque (inizializzazione, operazioni sulle celle di un vicinato).

2.2.3 Operazioni elementari

Le operazioni elementari contenute in un modello di guasto possono essere:

la verifica di una condizione riguardante le operating conditions della RAM (per

modellare guasti che occorrono in condizioni operative particolari);

la scrittura o la lettura (con o senza verifica) di una cella base o di una sua vicina,

eventualmente raggruppate per formare un’operazione multi-port;

Una lista di operazioni elementari può essere associata ad un vicinato predefinito di una

cella base (o sua vicina).

2.2.4 Delay ed operazioni non appartenenti al modello di guasto

Davanti ad un’operazione multi-port è possibile porre un prefisso di ripetizione e/o un

vincolo temporale (delay minimo o massimo dall’operazione precedente del modello di guasto).

Davanti ad ogni singola operazione single-port è possibile porre un vincolo temporale (delay

minimo o massimo dall’operazione precedente del modello di guasto sulla stessa cella).

Infine, ad ogni cella coinvolta nel guasto sono associati i permessi di operazioni di lettura

e/o scrittura (del valore presunto) non appartenenti al modello di guasto, abilitabili o disabilitabili in

ogni punto del modello.

2.3

Algoritmo di test

L’algoritmo di test vede la memoria come una matrice di parole, di ampiezza pari al

parallelismo massimo della porta di accesso considerata. Può contenere espressioni che riferiscono

variabili intere utente, costanti simboliche del modello della RAM e le operating conditions attuali.

2.3.1 Statements

I costrutti utilizzabili nell’algoritmo di test sono:

statements C-like (blocchi, cicli for, if-else, valutazione di un’espressione);

march elements: ripetizione delle operazioni contenute su tutte le parole della memoria;

vicinati: ripetizione delle operazioni contenute su un vicinato predefinito di una parola;

cicli burst: sequenza di letture e/o scritture in modalità burst;

ridefinizione dei background patterns.

2002 Luca Calaprice

2

Memory Fault Simulator

User’s Requirements

2.3.2 Operazioni elementari

Le operazioni elementari contenute negli statements dell’algoritmo di test possono essere:

attese temporali;

modifica delle operating conditions della RAM;

letture e scritture di parole di memoria, con un valore immediato o un background

pattern, ad un indirizzo implicito o esplicito (statements C-like), eventualmente

raggruppate in operazioni multi-port. Sono supportati i test trasparenti (valori p’, p).

3

Analisi della potenza media dissipata

Il vincolo sulla potenza è espresso come potenza media massima dissipabile in un dato

intervallo di tempo. Scegliendo il protocollo semisincrono, il programma calcola la massima

frequenza di clock del sistema di elaborazione che esegue l’algoritmo di test affinchè il vincolo sia

soddisfatto. Altrimenti, con il protocollo asincrono, il programma inserisce istruzioni di attesa

temporale in opportuni punti dell’algoritmo di test (cercando di non penalizzare i cicli più interni).

4

Fault simulation

La prima fase della fault simulation analizza la modularità dell’algoritmo di test. Se

possibile, si suddivide l’array di memoria in insiemi di celle che subiscono la stessa sequenza di

operazioni, esprimendone gli istanti di inizio come funzioni lineari degli indirizzi di riga e colonna.

Inoltre si determina la dimensione massima del rettangolo di vicinato su cui opera l’algoritmo.

Dato un modello di guasto, il numero di disposizioni di celle su cui si calcola la copertura

dipende dal numero k di celle base e dalla presenza di eventuali vicinati; ad esempio:

k = 1, senza vicinati: si considera una generica cella per ogni insieme (in presenza di

vincoli temporali, si calcolano i range di indirizzi in cui sono soddisfatti);

k = 2, senza vicinati: si considera ogni possibile combinazione degli insiemi di

appartenenza delle due celle. Per ognuna, fissata una delle due celle, si calcola la

copertura per i casi seguenti:

la seconda cella ha una posizione generica, ma la distanza verticale fra le due celle è

maggiore della dimensione del rettangolo di vicinato;

la seconda cella occupa una qualsiasi posizione in ogni riga a sinistra e a destra del

rettangolo di vicinato della prima;

la seconda cella occupa ogni possibile posizione nel rettangolo di vicinato della

prima.

Infine, avviene la minimizzazione dell’algoritmo di test (eliminazione delle operazioni inutili

contenute).

5

Output

In output si ottiene:

l’elenco dei modelli di guasto, con la copertura % di ciascuno (opzionalmente è

possibile avere l’elenco delle celle dell’array su cui ciascun guasto non è rilevato);

il testo dell’algoritmo di test, modificato con l’eventuale inserimento di attese temporali

(protocollo asincrono) e la cancellazione delle operazioni inutili;

la frequenza di clock massima (protocollo semisincrono).

2002 Luca Calaprice

3