ESERCIZIO 3

Si valuti il ritardo di propagazione di un inverter CMOS, considerando sia il

transitorio alto-basso che quello basso-alto della tensione di uscita, con una

tensione di ingresso a gradino. In particolare, si approssimi la corrente fornita dal

transistore che effettua la carica/scarica della capacità al nodo di uscita alla

corrente di saturazione (valutata negli esercizi 1 e 2).

Si supponga che la capacità di carico sia CL=1 pF, la tensione di alimentazione sia

VDD=3.3 V e che i transistori abbiano dimensioni minime (ovvero W/L=2/0.8).

Essendo la capacità di carico molto elevata rispetto alle capacità parassite dei

transistori, si trascurino queste ultime.

Si verifichi la correttezza delle approssimazioni introdotte mediante simulazione

SPICE.

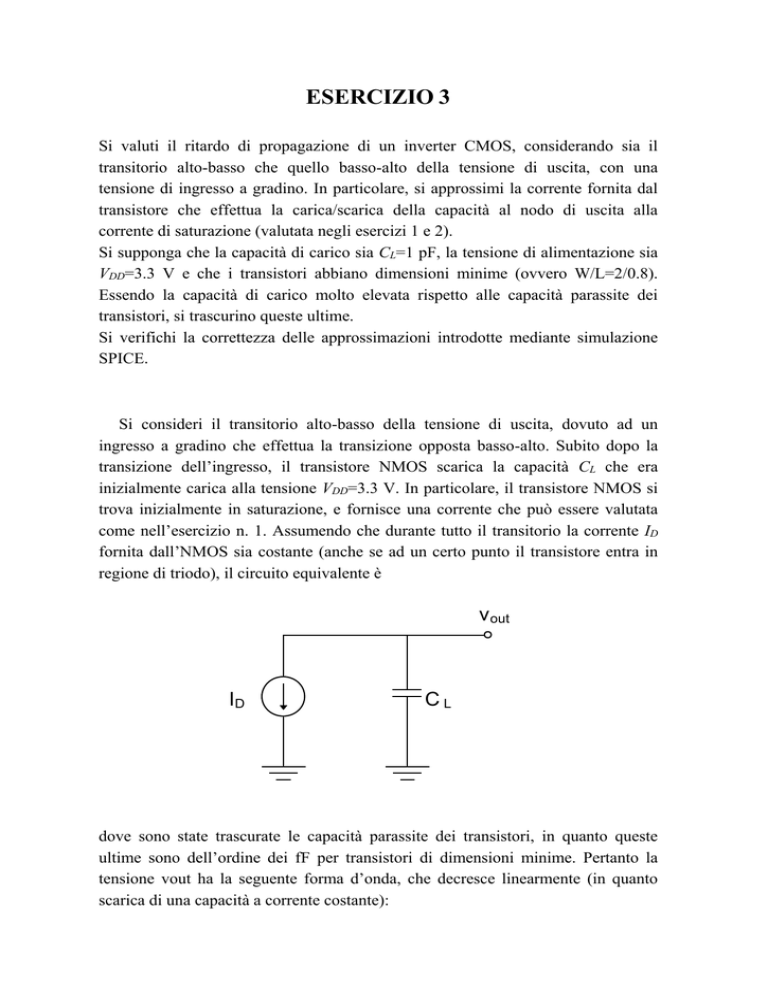

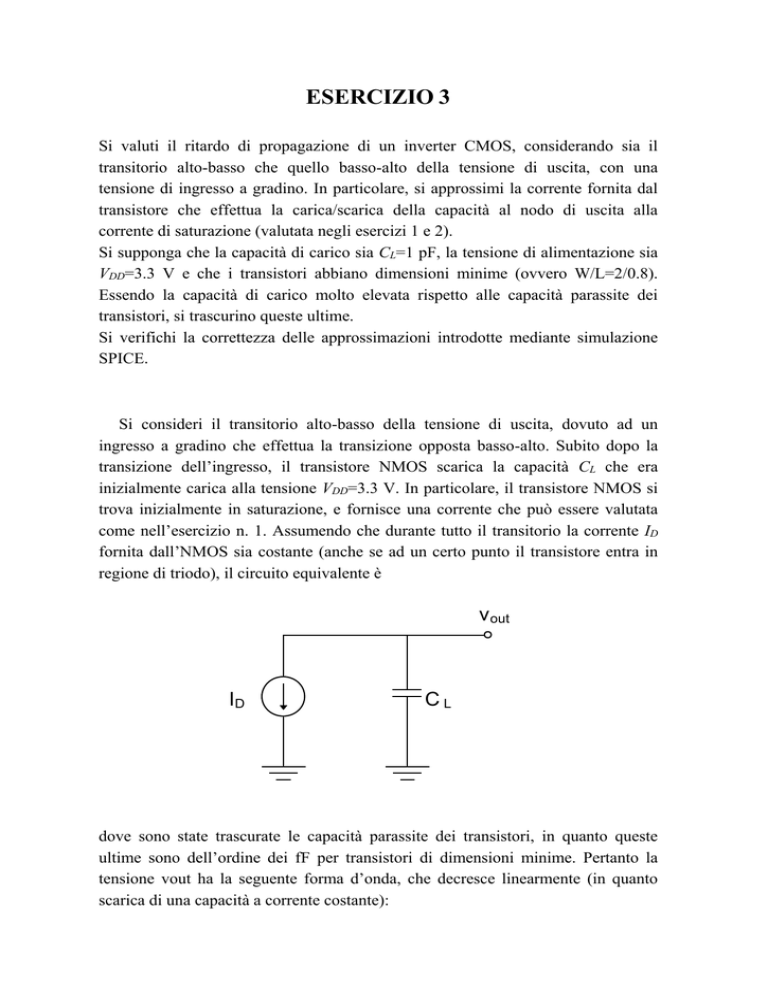

Si consideri il transitorio alto-basso della tensione di uscita, dovuto ad un

ingresso a gradino che effettua la transizione opposta basso-alto. Subito dopo la

transizione dell’ingresso, il transistore NMOS scarica la capacità CL che era

inizialmente carica alla tensione VDD=3.3 V. In particolare, il transistore NMOS si

trova inizialmente in saturazione, e fornisce una corrente che può essere valutata

come nell’esercizio n. 1. Assumendo che durante tutto il transitorio la corrente ID

fornita dall’NMOS sia costante (anche se ad un certo punto il transistore entra in

regione di triodo), il circuito equivalente è

v out

ID

CL

dove sono state trascurate le capacità parassite dei transistori, in quanto queste

ultime sono dell’ordine dei fF per transistori di dimensioni minime. Pertanto la

tensione vout ha la seguente forma d’onda, che decresce linearmente (in quanto

scarica di una capacità a corrente costante):

vout (t ) VDD

ID

t

CL

(3.1)

Per definizione, il ritardo di propagazione PD è l’intervallo necessario affinchè la

tensione di uscita attraversi il valore pari al 50% dell’intero swing, ovvero VDD/2.

Pertanto, imponendo vout(PD)=VDD/2 , dalla (3.1) si ottiene

PD

C L VDD

ID 2

(3.2)

Sostituendo nella (3.2) il valore della corrente di saturazione di ID=181.3 A

ottenuta nell’esercizio n. 1, il ritardo di propagazione nel transitorio alto-basso

della tensione di uscita risulta pari a 9.1 ns.

Per quanto riguarda il transitorio basso-alto della tensione di uscita, questo è

dovuto ad un ingresso che si suppone a gradino con tensione che va dall’alto al

basso (ovvero da 3.3 V a 0 V). Stavolta, il PMOS carica la capacità CL da 0 V a 3.3

V con una corrente che si può assumere circa costante e pari al valore di

saturazione, come discusso nell’esercizio n. 2. Il ritardo di propagazione è ancora

dato dalla (3.2), dove però la corrente ID si riferisce al PMOS, ed è pari al valore di

127.6 A, come discusso nell’esercizio n. 2. Il valore predetto dalla (3.2) è di 12.9

ns.

I valori del ritardo nelle due possibili transizioni della tensione di uscita

calcolati mediante la (3.2) sono stati ricavati introducendo varie approssimazioni.

Una verifica mediante simulazioni SPICE in transitorio è quindi opportuna, per

controllare la correttezza delle semplificazioni. A tal fine, si considera il seguente

circuito

V1

3.3Vdc

1Vac

TRAN =

M3

0A

MbreakP

V1 = 3.3

V2 = 0

TD = 0

TR = 10p

TF = 10p

PW = 100n

PER = 200n

0

M4

V

C1

V

1p

0A

MbreakN

0

0

0

dove la tensione di ingresso è scelta di tipo vpulse (consultare il manuale allegato

per avere maggiori dettagli), ovvero un’onda quadra. Essendo stato considerato nei

calcoli un segnale a gradino, è necessario impostare un tempo di salita e di discesa

molto breve rispetto al ritardo. In particolare è stato scelto un valore di 10 ps. Il

primo periodo viene ignorato, in quanto consente solo di caricare al valore di 3.3 V

la tensione di CL nel transitorio di ingresso da basso ad alto che si verifica all’inizio

del secondo periodo.

Il transitorio di scarica di CL avviene durante la frazione del periodo in cui

l’ingresso ha una tensione alta, ed è in questo intervallo di tempo che viene

valutato il ritardo di propagazione del transitorio alto-basso della tensione di uscita.

Nella frazione del periodo in cui l’ingresso ha una tensione bassa, la capacità CL

viene caricata ad una tensione di 3.3 V, ed è in questo intervallo di tempo che viene

valutato il ritardo di propagazione del transitorio basso-alto della tensione di uscita.

È utile notare che, per una misura attendibile di quest’ultimo ritardo, è necessario

che la tensione di uscita sia assestata al valore di 3.3 V di regime all’inizio del

transitorio; affinchè sia verificata tale condizione, è necessario che la frazione del

periodo precedente abbia una durata molto maggiore del ritardo, in modo che il

transitorio si possa considerare estinto. La stessa considerazione vale per la

frazione di periodo in cui l’ingresso è allo stato alto. Dato che il ritardo atteso è

dell’ordine dei 10 ns, è opportuno impostare la durata di ciascun semiperiodo in

modo che sia un ordine di grandezza superiore, ovvero 100 ns (quindi il periodo

della tensione di ingresso è di 200 ns).

In accordo con le considerazioni riportate sopra, la forma d’onda d’ingresso è la

seguente

La risposta ottenuta è

Utilizzando il cursore, dall’analisi del secondo periodo il valore del ritardo durante

il transitorio alto-basso e basso-alto è di 9.41 ns e 14 ns, rispettivamente. Si noti

che i valori predetti dall’analisi approssimata, di 9.1 ns e 12.9ns, sono certamente

vicini a quelli esatti, il che conferma la bontà delle approssimazioni introdotte.