Rev.13/3/2014

Esercizi proposti durante le lezioni di Elettronica 2

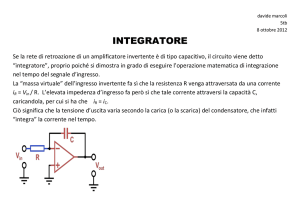

1. Ad un semplice integratore RC (R=10 kΩ, C=100 nF) viene applicato in ingresso un

segnale ad onda quadra (duty-cycle 50%) proveniente da una sorgente di tensione con

impedenza interna di 10 Ω. Disegnare in modo quantitativo la forma d’onda (a regime) del

segnale di uscita. Considerare i 4 casi relativi ad un ingresso unipolare 0-5 V, oppure

bipolare +/- 5 V, e semiperiodo di 1 ms oppure 10 ms.

2. Ripetere l’esercizio precedente per un derivatore realizzato con gli stessi componenti.

3. Ripetere l’esercizio precedente considerando un circuito passivo proporzionale-integratore

(R1=R2=10 kΩ, C=100 nF)

4. Ad un semplice derivatore RL (R=1 kΩ, L=1 mH) viene applicato in ingresso un segnale

unipolare ad onda quadra (0-5 V, duty-cycle 50%, semiperiodo pari a 10 µs) proveniente da

una sorgente di tensione con impedenza interna di 10 Ω. Determinare l’andamento

quantitativo del segnale di uscita dal momento in cui il segnale viene applicato.

5. Implementare la funzione logica (A+B)(C+D) per un sistema con quattro interruttori di

ingresso e un relé a 24 VDC in uscita (la resistenza della bobina è di 1000 Ω). Utilizzare

solo diodi e resistori.

6. Progettare un attenuatore variabile, con dinamica 10:1, per un segnale RF ampio 500

µVpp.

7. Progettare un commutatore a stato solido pilotato da un comando digitale bipolare (-5/+5

V), per collegare due antenne riceventi VHF ad un unico cavo coassiale. Il comando a -5

volt deve collegare solo la prima antenna al cavo, e il comando a +5 volt solo la seconda.

8. Per l’esercizio precedente valutare la possibilità di ottenere lo stesso funzionamento

utilizzando un comando unipolare.

9. Un trasformatore per alta tensione fornisce al suo secondario una tensione alternata di

valore efficace pari a circa 10 kV, ed è in grado si erogare una corrente di 10 mA.

Progettare il circuito raddrizzatore, ad una semionda, e il relativo filtro capacitivo.

10. Una sorgente di segnale, per un circuito di controllo elettronico alimentato a 3.3 V, ha una

impedenza interna di 10 kΩ e una normale escursione della tensione di uscita compresa tra

0 e 3 V. A causa di accidentali rumori e fluttuazioni, tale tensione può assumere, per

intervalli non superiori a 100 ms, valori negativi fino a -5 V o positivi fino a 10 V.

Condizionare il segnale in modo da proteggere l'ingresso del circuito di controllo.

11. Un trasformatore con ingresso a 220 V e uscita a 12 V (valore efficace) viene utilizzato per

misurare con precisione la frequenza di rete per mezzo di un frequenzimetro digitale avente

ingresso TTL (0-5 V). Definire il circuito di condizionamento del segnale.

12. Un indicatore di livello per un amplificatore audio è costituito da uno strumento a bobina

mobile con impedenza di 1 kΩ, una costante di tempo meccanica di 0.2 s e una tensione di

fondo scala di 10 V. Ad esso viene inviato un segnale audio unipolare con banda compresa

tra 20 Hz e 20 kHz e valori compresi tra 0 e 8 V. Condizionare il segnale affinché lo

strumento possa velocemente indicarne il valore di picco, mantenendo l'indicazione

(approssimata) per almeno 2 secondi.

13. Un elettrocardiografo genera un segnale a bassa impedenza, bipolare e ad alto livello,

compreso tra –3 e +5 V, con una banda compresa tra 0.5 e 50 Hz. Condizionare il segnale

affinché esso possa essere applicato ad un registratore a carta che necessita di un segnale

unipolare e non superiore a 10 V. L’impedenza di ingresso del registratore è di 100 kΩ .

14. Un fotodiodo ha una corrente inversa al buio pari a 1 µA, una responsivity di 0.3 A/W e una

capacità di barriera di 50 pF. Determinare il valore della resistenza di polarizzazione

necessario per ottenere un segnale ampio circa 1 V quando il fotodiodo è illuminato con un

segnale ottico modulato ON/OFF , avente potenza ottica di 100 µW durante i periodi ON.

Stimare anche la massima velocità di modulazione ammissibile per il segnale ottico, per la

resistenza calcolata.

15. Definire un espansore di scala per un voltmetro con impedenza di 5 kΩ e fondo scala di 10

V, utilizzato per misurare la tensione di un accumulatore nominalmente di 24 V, ma

tipicamente compresa tra 20 e 28 V.

16. La bobina di un invertitore a relé ha una resistenza di 1 kΩ e il contatto di uscita (in

chiusura verso massa) è collegato a 12 V tramite un resistore da 100 Ω. Assumendo per

questa “famiglia” logica ViH = 7 V e ViL= 4V, calcolare il valore di fan-out per uscita alta e il

margine di rumore in funzione del numero di ingressi collegati all’uscita.

17. Un invertitore RTL impiega un transistore 2N2222 il cui collettore è collegato alla

alimentazione (5V) tramite un resistore da 10 kΩ. La base è collegata a massa con un

resistore da 1 MΩ e alla alimentazione con un resistore da 100 kΩ. Per questa ipotetica

famiglia definire i livelli logici e i valori di fan-out. Ripetere l’esercizio assumendo che

l’uscita sia a collettore aperto. Calcolare la potenza dissipata dalla porta nei due casi, in

funzione del numero n di porte collegate all’uscita (nmax = fan-out).

18. Un invertitore RTL impiega un transistore MOS BS107 il cui drain è collegato alla

alimentazione (5V) tramite un resistore da 10 kΩ. Il gate è collegato alla alimentazione con

un resistore da 1 MΩ. Per questa ipotetica famiglia definire i livelli logici e i valori di fan-out

in funzione della frequenza massima di commutazione.

19. Studiare il data-sheet del transistore MOS BS107, con particolare attenzione al tempo di

commutazione.

20. Calcolare il numero di quadrati necessario per realizzare un resistore integrato di valore 10

kΩ utilizzando una ipotetica diffusione p a gradiente lineare tra 2*1016 cm-3 in superficie e

5*1015 cm -3 alla giunzione con il substrato n (alla profondità di 2 µm dalla superficie). Il

substrato è di tipo n, con un drogaggio uniforme di 2*1014 cm -3

21. Un traslatore di livello digitale, con ingresso 0-5 V e uscita 0-12 V, utilizza un transistore

NMOS BS107 e un resistore di drain da 10 kΩ. L’uscita del traslatore è collegata agli

ingressi di 10 porte invertenti, in logica 0-12 V, utilizzanti lo stesso transistore. Stimare il

massimo valore di clock utilizzabile.

22. Un invertitore NMOS alimentato a 9 V è realizzato per mezzo di un BS107 con carico in

configurazione pseudo-NMOS. Assumendo che il carico sia costituito da un transistore

PMOS avente caratteristiche analoghe a quelle del BS107 (opportunamente modificate nei

segni delle grandezze elettriche), tracciare la curva di carico dell’invertitore.

23. Un invertitore CMOS alimentato a 18 V è realizzato utilizzando i due transistori descritti

nell’esercizio precedente. Determinare, in forma grafica o numerica, l’energia dissipata

dalla porta quando al suo ingresso viene inviato un segnale a gradino con tempo di salita di

1 µs, trascurando tutte le capacità. Ripetere per una tensione di alimentazione di 5 V.

24. Descrivere il funzionamento di una porta di trasmissione MOS.

25. Un segnale TTL deve essere usato per pilotare una piccola lampadina al neon avente

tensione di innesco di 80 V e tensione di mantenimento di 40 V. La corrente della

lampadina deve essere compresa tra 2 e 5 mA. Dimensionare il buffer di pilotaggio della

lampadina.

26. Per una porta NAND in tecnologia DTL, realizzata con transistore 2N2222, diodi 1N4148 e

alimentata a 5 V, calcolare i valori di RB ed RC per un fan-out pari a 5.

27. Determinare la percentuale di riduzione del tempo di salita della corrente di collettore nella

risposta al gradino di un transistore bipolare, in funzione dell’entità del sovracomando di

base.

28. Dimensionare il circuito acceleratore per il pilotaggio di un invertitore realizzato con

transistore 2N2222 e resistenza di collettore pari a 1 kΩ (collegata a +5 V). ll segnale di

ingresso, è costituito da un’onda quadra tra 0 e 5 V con periodo di 10 µs.

29. Utilizzando transistori 2N2222 e 2N2907 e disponendo di un alimentatore a 12 V, realizzare

una cella in logica I2L che implementi un circuito NAND a tre ingressi compatibile TTL.

30. Descrivere il funzionamento di un invertitore BiCMOS.

31. Per un circuito differenziale ECL tipico, verificare che i valori dei componenti indicati

garantiscano il ripristino di livelli di tensione di uscita uguali a quelli di ingresso. Sostituire

poi il generatore di corrente con un resistore da 12 kΩ ed eventualmente modificare i valori

degli altri resistori affinché i livelli di uscita rimangano compatibili con quelli di ingresso.

32. Definire un circuito di interfaccia tra logica TTL ed ECL e tra ECL e TTL, assumendo che

l’alimentazione ECL sia negativa rispetto a massa.

33. In un amplificatore invertente, realizzato con operazionale, viene misurata una

amplificazione di –10 quando l’ingresso non invertente dell’operazionale viene collegato a

massa. Ricavare la relazione Vu/Vi per lo stesso circuito nel caso in cui l’uscita sia

reazionata verso l’ingresso non invertente con un partitore resistivo di valore ½.

34. Utilizzando un comparatore con isteresi, progettare un semplice regolatore ON/OFF per un

bagno termostatico avente le seguenti caratteristiche:

- segnale di uscita del sensore di temperature di valore T/20 (con T in °C);

- temperatura regolabile con un potenziometro tra 35 e 40 °C;

- isteresi di 1 °C.

35. Dimensionare un semplice oscillatore ad onda quadra a frequenza di 100 kHz utilizzando

un invertitore Schmitt trigger di tipo 74C14.

36. Dimensionare lo stesso oscillatore dell’esercizio precedente ma con un segnale di uscita

avente un duty-cycle del 20%.

37. Progettare un semplice circuito in grado di accendere un LED per un secondo, dopo 5

secondi dal rilascio di un pulsante.

38. Utilizzare uno Schmitt trigger per realizzare un semplice VCO con uscita a onda quadra e

frequenza tra 1000 e 10000 Hz in corrispondenza ad un segnale di controllo analogico

variabile tra 1 e 10 V.

39. Utilizzando il circuito AD585, realizzare i seguenti dispositivi di S&H:

- S&H con guadagno +2;

- S&H con guadagno -1;

- S&H con guadagno +1 e droop di 50 mV/s.

40. Un segnale sinusoidale ampio 5 Vpp deve essere campionato per essere acquisito in forma

numerica. Il circuito di S&H utilizzato ha un tempo di acquisizione di 50 µs, impiegando un

condensatore di tenuta da 1000 pF. Le correnti di fuga del S&H e dello stadio buffer che

segue il condensatore risultano complessivamente pari a 200 nA, entranti nel

condensatore. Il convertitore A/D che segue il circuito di S&H ha un tempo di conversione

di 200 µs. Determinare la massima frequenza del segnale utilmente applicabile all’ingresso

del circuito e la risoluzione richiesta al convertitore A/D (numero di bit da usare per la

conversione). Trascurare il fenomeno della iniezione di carica.

41. Per il circuito dell’esercizio precedente verificare la compatibilità tra la risoluzione calcolata

e l’iniezione di carica nel circuito di S&H, assumendo che questa sia pari a 100 pC.

42. Progettare un circuito attenuatore programmabile con due bit, per impieghi a frequenze

audio, avente Zin≈ ∞, Zout ≈ 0 e alimentazione a ±12V. Le attenuazioni possibili devono

essere :1, :2, :5 , :10, con una frequenza di lavoro massima di 10 kHz e massima

ampiezza del segnale di ingresso pari a 5 Vpp.

43. Progettare un multiplexer analogico avente le seguenti specifiche:

- 4 ingressi analogici e una uscita, per segnali di valore compreso tra –2 e +2 V;

- selezione digitale, a 2 bit, dell’ingresso connesso all’uscita, TTL compatibile.

44. Implementare la funzione richiesta nell’esercizio 12 tramite un diodo “ideale” realizzato con

un switch analogico.

45. Progettare un circuito con operazionale per amplificare un segnale avente valore compreso

tra 80 e 100 mV proveniente da un sensore di temperatura ambientale di precisione,. E’

richiesto un valore di amplificazione pari a 50 e una totale assenza di errore dovuto

all’offset dell’operazionale (suggerimento: eliminare l’errore di offset per mezzo di switch

analogici).

46. Un segnale audio avente ampiezza massima di 2 Vpp e dinamica di 60 dB deve essere

digitalizzato. Determinare la precisione richiesta per il convertitore A/D.

47. Per il segnale audio dell’esercizio precedente si assuma di aver scelto un ADC avente una

risoluzione di 10 mV. Valutare se con tale convertitore è opportuno un ulteriore

condizionamento del segnale di ingresso.

48. Per un DAC a resistori pesati si vuole impiegare un generatore di tensione di riferimento

avente resistenza interna pari a 1 Ω. Assumendo di utilizzare resistori di valore pari ad 1 kΩ

e suoi multipli, e che questi siano assolutamente precisi, valutare per quale massimo

numero di bit è ragionevole realizzare il DAC (assumere che i DAC abbiano i switch

orientati n modo da rendere compensabile l’offset dell’operazionale di uscita).

49. Per DAC a 10 bit calcolare la precisione richiesta ad ognuno dei resistori, sia per una

implementazione con resistori pesati sia per una struttura R-2R.

50. Il convertitore AD557 impiega tecnologia I2L per il latch di ingresso. Definire una possibile

struttura elettrica del percorso seguito da un bit, dall’ingresso TTL al switch del DAC.

51. Il comando di volume di un amplificatore audio richiede un potenziometro lineare da 100 kΩ

con cursore posizionabile in 32 punti del potenziometro. La manopola di volume

dell’amplificatore è collegata ad un disco avente 40 piccoli fori sulla sua periferia. I centri

dei fori sono tra loro spaziati del doppio del diametro dei fori. Da un lato del disco, in

corrispondenza dei fori, è posto un LED. Dall’altro lato del disco, di fronte al LED, sono

posti due fotodiodi affiancati. La distanza laterale tra i due fotodiodi è pari a metà del

diametro di un foro. Il disco, ruotando, intercetta la luce emessa dal LED verso i fotodiodi.

Definire la posizione dei fotodiodi e il circuito completo del potenziometro, assumendo che

un fotodiodo totalmente illuminato generi una corrente di 100 µA.

52. Un servoconvertitore A/D a 12 bit è costituito da un comparatore di ingresso avente un slew

rate di 1V/µs, da un contatore up/down in tecnologia TTLS e da un DAC con convertitore

corrente-tensione avente un tempo di assestamento di 500 ns (entro 0.01 del valore di

regime). Valutare il valore massimo di frequenza del segnale di ingresso che il convertitore

è in grado di agganciare e la relativa frequenza di clock da impiegare. Il segnale di ingresso

può assumere valori compresi tra –5 e +5 V.

53. Tracciare il diagramma di flusso di un programma da implementare su un microcontrollore

per la gestione di un convertitore A/D con reazione a gradini.

54. Ipotizzando di implementare la parte logica di un convertitore SAR per mezzo di un

microcontrollore, definire il diagramma di flusso del relativo programma, includendo sia la

gestione del S&H, sia del protocollo di uscita seriale RS232.

55. Il segnale generato da un sensore è variabile tra –5 e +5 volt ed ha una banda di frequenza

compresa tra 0 e 100 Hz. Il segnale deve essere digitalizzato a 10 bit con la tecnica della

doppia integrazione. Progettare un circuito ADC completo, assumendo di disporre di un

contatore CMOS a 12 bit.

56. Uno scintillatore per applicazioni nucleari impiega un fotomoltiplicatore in configurazione

integratrice. Gli impulsi generati dallo strumento hanno ampiezza variabile tra 100 mV e 2

V. Definire: (1) la struttura di un analizzatore multicanale in grado di discriminare l’ampiezza

del segnale in un campo di 20 valori; (2) il diagramma di flusso di un programma in grado di

gestire l’analizzatore e di presentare in forma matriciale (adatta alla visualizzazione tramite

istogrammi) la distribuzione di ampiezza degli impulsi.

57. La velocità di un piccolo motore in corrente continua deve essere controllata da un segnale

analogico compreso tra 1 V (veloc. Minima) e 6 V (veloc. massima). In corrispondenza a

tale escursione di valori la corrente del motore deve variare tra 100 e 600 mA. Per motivi di

efficienza energetica, la corrente nel motore viene modulata in PWM, per mezzo di un VCO

digitale realizzato con un integrato di tipo 555. Definire il circuito completo del controllore,

dall’ingresso analogico di tensione all’uscita in corrente a duty-cycle variabile.

58. Un canale di trasmissione digitale consente l’invio fedele di impulsi la cui larghezza minima

non sia inferiore a 1 µs. Progettare un modulatore Delta (ADC) e il relativo ricevitore (DAC)

adatti al canale di trasmissione disponibile, indicando la massima velocità di variazione

ammissibile (V/µs) per il segnale analogico di ingresso. Si assuma che tale segnale possa

variare tra –5 e +5 volt, e si imponga un errore di quantizzazione non superiore a 100 mV.

59. Progettare un circuito di controllo “smart” (a 2 stati o PWM) per un relé alimentato a 24 V,

con resistenza della bobina di 100 Ω e induttanza di 50 mH. Assumere una variazione di

induttanza, alla commutazione, di un fattore 2. Il relé deve essere attivato in

corrispondenza ad un livello alto TTL.

60. Un regolatore di velocità per un motore in corrente continua è controllato da un

microprocessore con bus di I/O a 8 bit, con livelli TTL. Si assuma che il motore abbia una

velocità massima di 20 giri/s quando è attraversato da una corrente di 10 A. Il motore è

dotato di una dinamo tachimetrica la cui tensione di uscita vale v/10, dove v è la velocità, in

giri/s. La resistenza dell’avvolgimento del motore e di 4 Ω. (1) Progettare una interfaccia in

grado di controllare su 256 livelli la velocità del motore. (2) Tracciare un grafico della

efficienza energetica del regolatore, in funzione della velocità. (3) Valutare la possibilità di

controllo PWM della corrente nel motore, per minimizzare la perdita di energia nel

regolatore.

61. Definire la struttura logica di un contatore per 7 e di un divisore di frequenza per 12 con

uscita simmetrica.

62. Utilizzare un DIAC per generare segnali a dente di sega esponenziale avente frequenza di

500 Hz. Il DIAC ha VBR = 100 V, IAmax = 10°, Ihold = 20 mA.