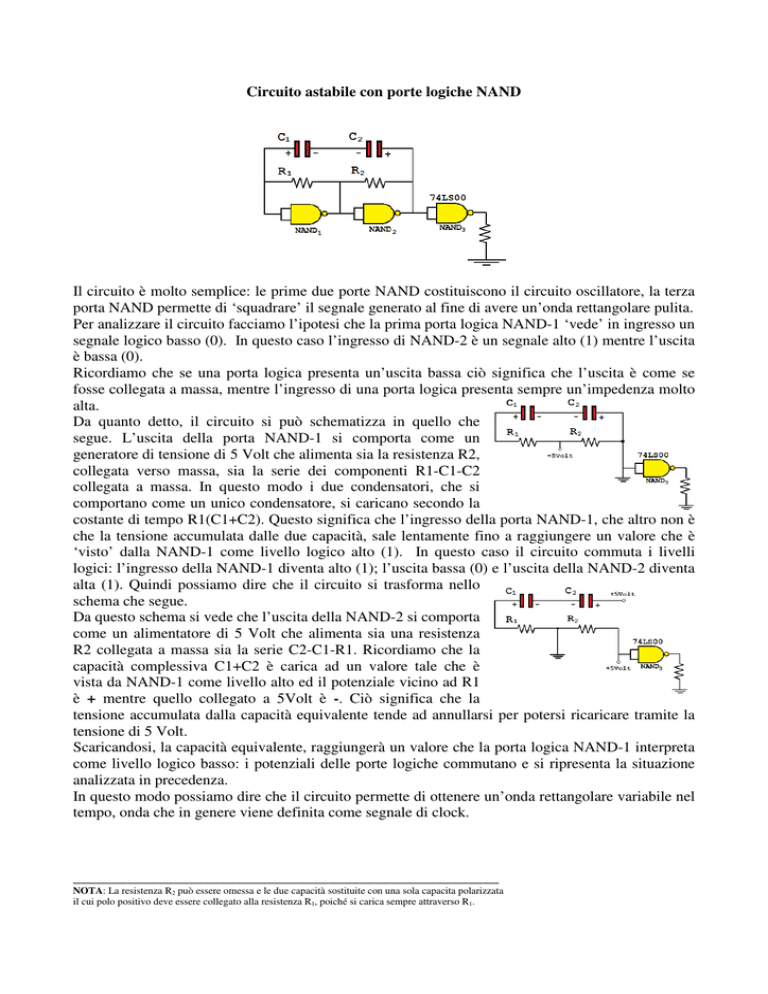

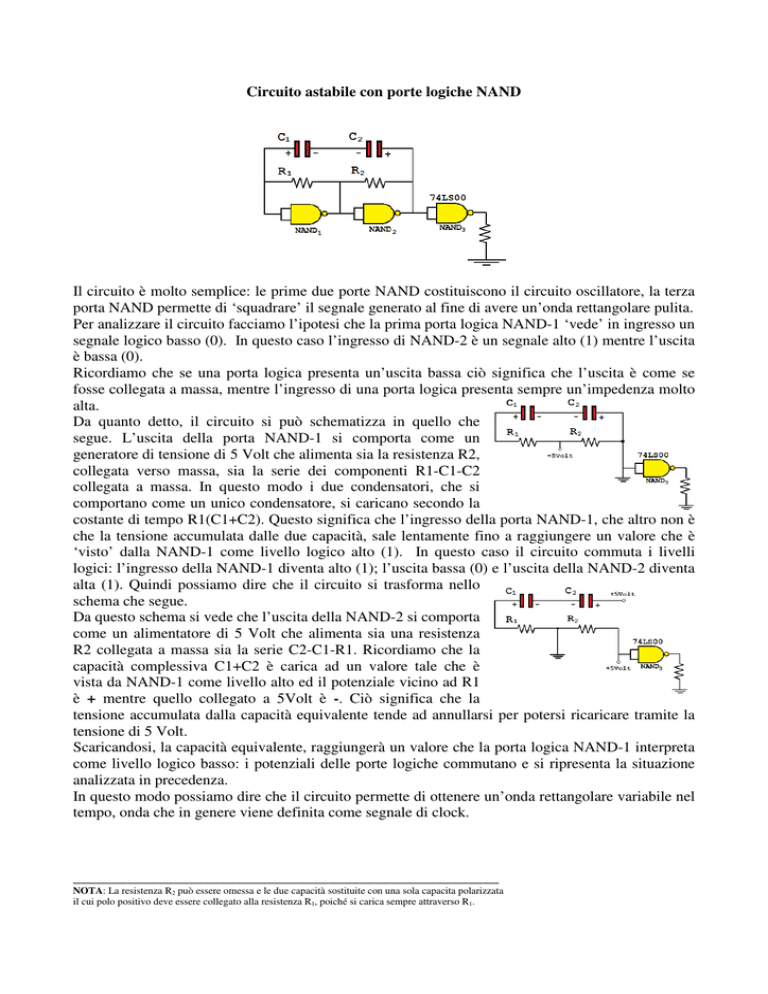

Circuito astabile con porte logiche NAND

Il circuito è molto semplice: le prime due porte NAND costituiscono il circuito oscillatore, la terza

porta NAND permette di ‘squadrare’ il segnale generato al fine di avere un’onda rettangolare pulita.

Per analizzare il circuito facciamo l’ipotesi che la prima porta logica NAND-1 ‘vede’ in ingresso un

segnale logico basso (0). In questo caso l’ingresso di NAND-2 è un segnale alto (1) mentre l’uscita

è bassa (0).

Ricordiamo che se una porta logica presenta un’uscita bassa ciò significa che l’uscita è come se

fosse collegata a massa, mentre l’ingresso di una porta logica presenta sempre un’impedenza molto

alta.

Da quanto detto, il circuito si può schematizza in quello che

segue. L’uscita della porta NAND-1 si comporta come un

generatore di tensione di 5 Volt che alimenta sia la resistenza R2,

collegata verso massa, sia la serie dei componenti R1-C1-C2

collegata a massa. In questo modo i due condensatori, che si

comportano come un unico condensatore, si caricano secondo la

costante di tempo R1(C1+C2). Questo significa che l’ingresso della porta NAND-1, che altro non è

che la tensione accumulata dalle due capacità, sale lentamente fino a raggiungere un valore che è

‘visto’ dalla NAND-1 come livello logico alto (1). In questo caso il circuito commuta i livelli

logici: l’ingresso della NAND-1 diventa alto (1); l’uscita bassa (0) e l’uscita della NAND-2 diventa

alta (1). Quindi possiamo dire che il circuito si trasforma nello

schema che segue.

Da questo schema si vede che l’uscita della NAND-2 si comporta

come un alimentatore di 5 Volt che alimenta sia una resistenza

R2 collegata a massa sia la serie C2-C1-R1. Ricordiamo che la

capacità complessiva C1+C2 è carica ad un valore tale che è

vista da NAND-1 come livello alto ed il potenziale vicino ad R1

è + mentre quello collegato a 5Volt è -. Ciò significa che la

tensione accumulata dalla capacità equivalente tende ad annullarsi per potersi ricaricare tramite la

tensione di 5 Volt.

Scaricandosi, la capacità equivalente, raggiungerà un valore che la porta logica NAND-1 interpreta

come livello logico basso: i potenziali delle porte logiche commutano e si ripresenta la situazione

analizzata in precedenza.

In questo modo possiamo dire che il circuito permette di ottenere un’onda rettangolare variabile nel

tempo, onda che in genere viene definita come segnale di clock.

_______________________________________________________

NOTA: La resistenza R2 può essere omessa e le due capacità sostituite con una sola capacita polarizzata

il cui polo positivo deve essere collegato alla resistenza R1, poiché si carica sempre attraverso R1.