Organizzazione dei calcolatori

Gerarchie di memoria

Politecnico di Milano

Gerarchia di memoria

Introduzione

Prof. William Fornaciari

Politecnico di Milano

[email protected]

www.elet.polimi.it/~fornacia

www.elet.polimi.it/~fornacia

©2004 William Fornaciari

Sommario

Le esigenze di memoria

Il principio di località dei programmi

La gerarchia di memoria

Principio di funzionamento della memoria cache

I problemi di progetto delle memorie cache

Prestazioni e ottimizzazioni (cenni)

Approfondimenti:

H&P, Hamacher, Stallings

Gerarchie di memoria

©2004 William Fornaciari

-2-

©2004 William Fornaciari

1

Organizzazione dei calcolatori

Gerarchie di memoria

Elementi di memoria di un

elaboratore

Processore

Nuovo elemento

dell’architettura

Reg

Cache

Memory-I/O bus

Memoria

I/O

controller

disk

Disk

disk

Disk

Gerarchie di memoria

I/O

controller

I/O

controller

Display

Network

-3-

©2004 William Fornaciari

La memoria di un sistema

d’elaborazione

Esigenze

Elaborazione

Archiviazione

Caratteristiche importanti

Velocità, Capacità, Persistenza, Costo

Tecnologie più comuni

Elettronica: veloce, costosa, volatile

Magnetica: lenta, economica, permanente

Ottica: lenta, economica, difficilmente modificabile

Obiettivi

Unire le tecnologie per giungere a una memoria,

veloce, capace e persistente a costi di mercato

Gerarchie di memoria

©2004 William Fornaciari

-4-

©2004 William Fornaciari

2

Organizzazione dei calcolatori

Gerarchie di memoria

Tecnologie di memoria

Capacità (quantità di bit)

nastro magnetico

Costo (in $ per bit)

disco magnetico rigido

100 Gbit

1 Gbit

disco ottico

memoria centrale

10 Mbit

cache di 2° livello

100 Kbit

cache di 1° livello

1 Kbit

disco magnetico flessibile

banco dei registri

1 bit

bistabile

< 1 ns

1 ns

5 ns

10 ns

50 ns

10 ms

1 sec

Tempo di accesso

Gerarchie di memoria

-5-

©2004 William Fornaciari

Il principio di località dei

programmi

Località spaziale

se l’istruzione di indirizzo i entra in esecuzione, con

probabilità ≈ 1 anche l’istruzione di indirizzo i + di

entrerà in esecuzione (di è un intero piccolo)

Motivazione

di solito le istruzioni sono eseguite in sequenza

i salti sono relativamente rari o comunque spesso sono

polarizzati verso un ramo

Gerarchie di memoria

©2004 William Fornaciari

-6-

©2004 William Fornaciari

3

Organizzazione dei calcolatori

Gerarchie di memoria

Il principio di località dei

programmi

Località temporale

se un’istruzione entra in esecuzione al tempo t, con

probabilità ≈ 1 la stessa istruzione sarà rieseguita al

tempo t + dt (dove dt è piccolo rispetto a t)

Motivazione

spesso le istruzioni rieseguite fanno parte di un ciclo,

la cui presenza è giustificata solo se esso viene

reiterato molte volte

se un’istruzione appartenente a un ciclo entra in

esecuzione, è molto probabile che, entro il tempo di

un’iterazione del ciclo, essa venga rieseguita

i cicli brevi generalmente sono molto più numerosi di

quelli lunghi

Gerarchie di memoria

-7-

©2004 William Fornaciari

Il principio di località dei

programmi

Località spaziale e temporale sono indipendenti

Se valgono entrambi, sono riassunti nel principio di

località spazio-temporale

se l’istruzione di indirizzo i entra in esecuzione al

tempo t, con probabilità ≈ 1 l’istruzione di indirizzo

i + di entrerà in esecuzione al tempo t + dt, dove di e

dt sono piccoli rispetto a i e t, rispettivamente

La località spazio-temporale è statisticamente ben

verificata dalla maggior parte dei programmi

la maggioranza delle istruzioni appartiene a cicli

interni, con corpo sequenziale, brevi, iterati

numerose volte e operanti su dati contigui

legge empirica: 90% del tempo è speso sul 10% codice

Gerarchie di memoria

©2004 William Fornaciari

-8-

©2004 William Fornaciari

4

Organizzazione dei calcolatori

Gerarchie di memoria

Interpretazione del principio di

località

Le istruzioni del programma si possono raggruppare

in “blocchi” di istruzioni consecutive

se un’istruzione (qualsiasi) di un blocco entra in

esecuzione, allora l’intero blocco di istruzioni verrà

eseguito

se un blocco (qualsiasi) entra in esecuzione, allora

entro breve tempo lo stesso blocco verrà rieseguito

I blocchi sono per esempio i “corpi” dei cicli più

interni al programma

Anche i dati (oltre alle istruzioni) possono soddisfare

al principio di località spazio-temporale

Gerarchie di memoria

-9-

©2004 William Fornaciari

La gerarchia di memoria

La

memoria

viene

organizzata

in

livelli

caratterizzati da velocità, dimensioni e costi diversi

I blocchi possono essere trasferiti da un livello

inferiore a uno superiore

Cerco di tenere i blocchi di informazione usati più di

frequente vicino alla CPU, per ottimizzare i tempi

Il dimensionamento del sistema e le politiche di

gestione derivano da analisi statistico/quantitative

delle applicazioni

L’obiettivo è fornire la sensazione di una memoria

con la velocità del primo livello e la capacità del

(dei) successivo(i)

Gerarchie di memoria

©2004 William Fornaciari

- 10 -

©2004 William Fornaciari

5

Organizzazione dei calcolatori

Gerarchie di memoria

La gerarchia di memoria: il livello

cache

parte di interesse per la discussione sulla cache

MEMORIA

VIRTUALE

ciclo del

programma

carica le/i

istr./dati da

eseguire/

elaborare

ciclo del

programma

MEMORIA

CACHE

carica i

blocchi

entranti

in uso

MEMORIA

CENTRALE

blocco di istr.

blocco di dati

pagina di istr.

carica le

pagine

entranti

in uso

pagina di dati

blocco di istr.

PROCESSORE

blocco di dati

registri

scarica i

risultati

elaborati

scarica i

blocchi

non più

in uso

Velocità, costi

Gerarchie di memoria

scarica le

pagine

non più

in uso

Capacità (quantità di bit)

- 11 -

©2004 William Fornaciari

Terminologia

Hit: tentativo di accesso(lett./scritt.) con successo

a un determinato livello della gerarchia

Miss: tentativo di accesso(lett./scritt.) andato a

vuoto

Hit time: tempo di accesso a livello superiore della

gerarchia (incluso rilevazione ev. fallimento)

Miss penality: tempo per sostituire un blocco nel

livello superiore con uno del livello inferiore, più il

tempo di lettura del dato cercato

Hit rate, Miss rate: percentuale dei tentativi di

accesso che hanno successo o falliscono (Mr=1-Hr)

Gerarchie di memoria

©2004 William Fornaciari

- 12 -

©2004 William Fornaciari

6

Organizzazione dei calcolatori

Gerarchie di memoria

Organizzazione di una memoria

cache

Memoria centrale e cache sono organizzate a

blocchi di parole, di uguale dimensione

La memoria cache contiene copie di blocchi della

memoria centrale, oppure blocchi liberi

Il sistema di gestione della cache è in grado di

copiare (caricare) blocchi dalla memoria centrale

alla memoria cache, oppure di ricopiare (scaricare)

blocchi dalla memoria cache alla memoria centrale,

tramite un’apposita unità funzionale

Normalmente il processore accede solo alla

memoria cache (tranne casi particolari)

La capacità del sistema è pari a quella della sola

memoria centrale (la cache contiene solo copie )

Gerarchie di memoria

- 13 -

©2004 William Fornaciari

Struttura della memoria cache

unità funzionale di

copiatura / ricopiatura

(carico /scarico)

dei blocchi di memoria

IND. DI

BLOCCO

MEMORIA

CENTRALE

512 × 32

parola

0: 000

IND. DI

PAROLA

0: 000000

63: 111111

FLAG DI IND. DI

BLOCCO BLOCCO

MEMORIA

CACHE

256 × 32

IND. DI

PAROLA

parola

1

1: 001

0: 000000

0: 00

blocco

parola

0: 000000

63: 111111

2: 010

63: 111111

1

1: 01

1

2: 10

0

3: 11

blocco

0: 000000

parola

63: 111111

parola

43: 101011

3: 011

4: 100

blocco

libero

5: 101

6: 110

2, 43: 10, 101011 = 10101011

parola

24: 011000

(indirizzo di parola completo)

memoria ausiliaria

contenente i bit di

allocazione dei blocchi

Gerarchie di memoria

©2004 William Fornaciari

6, 24: 110, 011000 = 110011000 7: 111

(indirizzo di parola completo)

- 14 -

©2004 William Fornaciari

7

Organizzazione dei calcolatori

Gerarchie di memoria

Istruzioni: funzionamento base

Il processore preleva istruzione dalla memoria cache

(non dalla memoria centrale)

Se il blocco contenente l’istruzione da prelevare si

trova nella memoria cache, l’istruzione viene letta

e il processore prosegue l’esecuzione

Se l’istruzione da prelevare non si trova nella cache

il processore sospende l’esecuzione

il blocco contenente l’istruzione da prelevare (ed

eseguire) viene caricato dalla memoria centrale in un

blocco libero della memoria cache

il processore preleva l’istruzione dalla memoria cache

e riprende l’esecuzione

Gerarchie di memoria

- 15 -

©2004 William Fornaciari

Dati: funzionamento base

Il processore deve leggere il dato dalla memoria

cache, oppure deve scrivere il dato nella memoria

cache

Se il dato da leggere/scrivere non si trova nella

memoria cache, si procede in modo simile alle

istruzioni (con qualche differenza, soprattutto nel

caso della scrittura)

Casi particolari

in determinate situazioni o sistemi è richiesto che il

processore possa accedere direttamente alla memoria

centrale, bypassando la cache

Gerarchie di memoria

©2004 William Fornaciari

- 16 -

©2004 William Fornaciari

8

Organizzazione dei calcolatori

Gerarchie di memoria

I principali problemi di progetto

Metodo di indirizzamento

come scegliere il blocco della cache in cui copiare un

dato blocco di memoria centrale (mapping)

Metodo di identificazione

come localizzare un dato blocco di istruzioni o dati

all’interno della cache

Metodo di lettura

come comportarsi quando si deve leggere una parola

contenuta in un blocco della memoria cache

Metodo di scrittura (problema della coerenza)

come comportarsi quando si deve leggere una parola

contenuta in un blocco della memoria cache

Metodo di sostituzione

Come si sostituiscono i blocchi della cache al fine di

liberare spazio per caricarne altri

Gerarchie di memoria

- 17 -

©2004 William Fornaciari

Indirizzamento diretto

Ogni blocco della memoria

centrale è caricabile in un solo

blocco della cache

Il blocco j in mem principale

è tradotto in blocco

j MOD #blocchi in cache

Alta velocità, basso costo,

numerosi conflitti di

allocazione

etichetta

Gerarchie di memoria

©2004 William Fornaciari

- 18 -

MEMORIA

CENTRALE

IND. DI

BLOCCO

0 0 0

000

B0

IND. DI

BLOCCO

Es. se debbo accedere a

informazioni in blocco B0 e B4,

anche se il resto della cache è

vuota, ho continui conflitti

# blocco

0 0 1

MEMORIA

CACHE

B1

C0

B2

C1

B3

C2

B4

C3

B5

0 1 0

00

0 1 1

01

1 0 0

10

1 0 1

11

1 1 0

B6

1 1 1

B7

©2004 William Fornaciari

9

Organizzazione dei calcolatori

Gerarchie di memoria

Indirizzamento diretto e

identificazione

Per identificare un blocco in

cache occorre memorizzare in

memoria associativa

l’etichetta dell’indirizzo di

memoria centrale

L’indirizzo di memoria centrale

e suddiviso in tre sezioni

etichetta

# blocco

MEMORIA

CENTRALE

IND. DI

BLOCCO

0 0 0

000

B0

IND. DI

BLOCCO

0 0 1

MEMORIA

CACHE

B1

C0

B2

C1

B3

C2

B4

C3

B5

0 1 0

00

0 1 1

01

1 0 0

10

1 0 1

11

etichetta

quale blocco di mem

centrale, fra i possibili,

è realmente caricato in

cache

blocco

parola

1 1 0

blocco della cache

ove memorizzare il

blocco della centale

Gerarchie di memoria

quale parola fra

quelle del blocco

B6

1 1 1

B7

- 19 -

©2004 William Fornaciari

Indirizzamento diretto:

esecuzione

La CPU genera indirizzo e subito analizza la cache

I bit del campo blocco puntano a blocco particolare

della cache

I bit più significativi, quelli dell’etichetta, sono

confrontati con l’etichetta associata al blocco cache

se sono uguali

OK, la parola è in quel blocco di cache

se sono diversi

debbo leggere e caricare blocco contenente la parola

desiderata dalla memoria centrale

Gerarchie di memoria

©2004 William Fornaciari

- 20 -

©2004 William Fornaciari

10

Organizzazione dei calcolatori

Gerarchie di memoria

Indirizzamento diretto: esempio

Mostrare la struttura degli indirizzi di memoria per

il seguente sistema

mem principale di 4 M parole

blocchi da 64 parole

mem cache di 1K parole

Risposta

ind memoria = 22 bit totali (222= 22 *220= 4 M)

campo parola= 6 bit (indirizzo le 26=64 parole del

blocco)

# blocchi: dim cache/dim blocchi = 1K/64= 16 blocchi

nella cache che posso identificare con 4 bit

Etichetta= 12 (22-4-6), infatti

64K blocchi in mem princip/16 blocchi cache = 212

Gerarchie di memoria

- 21 -

©2004 William Fornaciari

Indirizzamento associativo

Ogni blocco delle memoria

centrale è caricabile in un

blocco qualunque della

cache

Ho pochi conflitti di

allocazione ma costo

elevato

Riduco al minimo la

presenza di blocchi liberi

non sfruttati in cache

MEMORIA

CENTRALE

etichetta

IND. DI

BLOCCO

0 0 0

000

B0

IND. DI

BLOCCO

0 0 1

MEMORIA

CACHE

B1

C0

B2

C1

B3

C2

B4

C3

B5

0 1 0

00

0 1 1

01

1 0 0

10

1 0 1

11

1 1 0

B6

1 1 1

B7

Gerarchie di memoria

©2004 William Fornaciari

- 22 -

©2004 William Fornaciari

11

Organizzazione dei calcolatori

Gerarchie di memoria

Indirizz. associativo e

identificazione

In una memoria associativa

viene memorizzata

l’etichetta dell’indirizzo di

memoria centrale

L’indirizzo di memoria

centrale e suddiviso in due

sole sezioni

MEMORIA

CENTRALE

0 0 0

B0

IND. DI

BLOCCO

0 0 1

MEMORIA

CACHE

B1

C0 = B0

B2

C1= B3

B3

C2= B6

B4

C3= B5

B5

0 1 0

00

00

000

01

011

10

110

11

101

0 1 1

01

1 0 0

10

1 0 1

11

etichetta

quale blocco di mem

centrale è caricato in cache

Gerarchie di memoria

IND. DI

BLOCCO

parola

1 1 0

quale parola fra

quelle del blocco

B6

memoria associativa

contenente le etichette dei

blocchi allocati

- 23 -

1 1 1

B7

©2004 William Fornaciari

Indirizzamento associativo:

esecuzione

La CPU genera un indirizzo e subito viene analizzata

la cache

I bit di etichetta dell’indirizzo di memoria centrale

sono confrontati in modo associativo con tutti quelli

della cache per vedere se il blocco è presente in

cache

Etichette lunghe

mem associativa più grossa, costosa e lenta del

diretto

Uso lo spazio più efficientemente

un blocco esce dalla cache solo se è piena

riduco in numero di miss (penalità)

Gerarchie di memoria

©2004 William Fornaciari

- 24 -

©2004 William Fornaciari

12

Organizzazione dei calcolatori

Gerarchie di memoria

Indirizzamento associativo:

esempio

Mostrare la struttura degli indirizzi di memoria per

il seguente sistema

mem principale di 4 M parole

blocchi da 64 parole

mem cache di 1K parole

Risposta

ind memoria = 22 bit totali (222= 22 *220= 4 M)

campo parola= 6 bit (indirizzo le 26=64 parole del

blocco)

Etichetta= 16 (22-6), infatti

4M/64= 64K (216) blocchi in mem principale

Gerarchie di memoria

- 25 -

©2004 William Fornaciari

Indirizzamento set-associativo

I blocchi della cache sono

suddivisi in gruppi (set)

Ogni blocco della

memoria centrale è

caricabile in un dato set

Ho alcuni conflitti di

allocazione, costi e

velocità medi

È la soluzione intermedia

fra la soluzione diretta e

associativa

Gerarchie di memoria

©2004 William Fornaciari

etichetta

# gruppo

MEMORIA

CENTRALE

IND. DI

BLOCCO

0 0 0

0 0 0

B0

{

{

GRUPPI

- 26 -

IND. DI

BLOCCO

0 0 1

MEMORIA

CACHE

B1

C0

B2

C1

B3

C2

B4

C3

B5

0 1 0

00

G0

G1

0 1 1

01

1 0 0

10

1 0 1

11

1 1 0

B6

# DI GRUPPI

=2

DIM. GRUPPO = 2

1 1 1

B7

©2004 William Fornaciari

13

Organizzazione dei calcolatori

Gerarchie di memoria

Indirizz. set-associativo e

identificazione

Per identificare un blocco in

cache occorre memorizzare

in memoria associativa

l’etichetta dell’indirizzo di

memoria centrale relativi ai

blocchi effettivamente

allocati nel set

L’indirizzo di memoria

centrale è suddiviso in tre

sezioni etichetta blocco

parola

quale blocco di mem

centrale, fra i possibili per

un dato set, è realmente

caricato in cache

Gerarchie di memoria

set della memoria

cache nel quale è

caricato il blocco

MEMORIA

CENTRALE

IND. DI

BLOCCO

0 0 0

B0

{

{

IND. DI

GRUPPO

IND. DI

BLOCCO

0 0 1

MEMORIA

CACHE

B1

C0 = B0

B2

C1 = B6

B3

C2 = B5

B4

C3 = B3

B5

0 1 0

00

0

00

00

01

11

10

10

11

01

1

0 1 1

01

1 0 0

10

1 0 1

11

1 1 0

B6

memoria associativa

contenente le etichette

dei blocchi allocati

1 1 1

B7

quale parola fra

quelle del blocco

- 27 -

©2004 William Fornaciari

Indirizz. set-associativo:

esecuzione

I bit di etichetta dell’indirizzo di memoria centrale

sono confrontati in modo associativo con le

etichette dei blocchi dell’insieme da controllare,

per vedere se il blocco è presente in cache

Etichette di lunghezza intermedia

mem associativa più piccola del caso precedente, più

veloce e meno costosa (più grossa del diretto)

Conflitti

ho meno conflitti del diretto ma ho meno scelta nel

posizionare il blocco rispetto al caso associativo

Casi limite

1 blocco per set: indirizzamento diretto

1 solo insieme: indir. completamente associativo

Gerarchie di memoria

©2004 William Fornaciari

- 28 -

©2004 William Fornaciari

14

Organizzazione dei calcolatori

Gerarchie di memoria

Indirizz. set-associativo: esempio

Mostrare la struttura degli indirizzi di memoria per

il seguente sistema

mem principale di 4 M parole

blocchi da 64 parole

mem cache di 1K parole

2 blocchi per insieme

Risposta

ind memoria = 22 bit totali (222= 22 *220= 4 M)

campo parola= 6 bit (indirizzo le 26=64 parole del

blocco)

blocco: 3 bit; dim cache/dim set = 1K/64*2 = 23 set

Etichetta: 13 bit (22-6-3)

Gerarchie di memoria

- 29 -

©2004 William Fornaciari

Cache hit: metodi di scrittura

Problema della coerenza

il blocco è in cache, ma scrivendo la parola solo in

cache la memoria centrale non è più allineata

Politiche di scrittura della parola

Write-through (immediata)

il processore scrive la parola sia in memoria centrale,

sia nella cache e prosegue la sua attività

Write-back (differita)

il processore scrive solo in cache e prosegue attività

il blocco viene marcato come modificato e in seguito

(tipicamente all’atto della rimozione per fare spazio)

verrà ricopiato in cache

Gerarchie di memoria

©2004 William Fornaciari

- 30 -

©2004 William Fornaciari

15

Organizzazione dei calcolatori

Gerarchie di memoria

Cache hit: metodi di lettura

Nessun problema!

Il blocco è nella cache

la parola viene letta dalla copia residente in cache

Il processore continua subito la propria attività

Gerarchie di memoria

- 31 -

©2004 William Fornaciari

Cache miss: lettura

Il processore si sospende e il blocco deve essere

caricato da mem centrale in mem cache

Politiche di lettura della parola

Read-through (immediata)

il processore legge la parola non appena viene caricata

in cache e riprende subito l’attività

Read-back (differita)

il processore attende che l’intero blocco sia stato

caricato in cache, poi legge la parola e riprende attività

Gerarchie di memoria

©2004 William Fornaciari

- 32 -

©2004 William Fornaciari

16

Organizzazione dei calcolatori

Gerarchie di memoria

Cache miss: scrittura

L’operazione di scrittura è molto meno frequente

della lettura

in generale non è obbligatorio caricare il blocco dalla

mem centrale in cache

Politiche di scrittura della parola

Write-through (immediata)

il processore bypassa la cache, scrive la parola solo in

mem centrale e riprende attività

Write-back (differita)

il processore copia il blocco interessato nella cache

il processore scrive solo in cache e prosegue attività

il blocco viene marcato come modificato e in seguito

(come nel caso write-back hit) verrà ricopiato in cache

Gerarchie di memoria

- 33 -

©2004 William Fornaciari

Metodo di sostituzione

Problema

si deve caricare un blocco in cache ma non esistono

più blocchi liberi per accoglierlo

Soluzione

sostituzione: scegliere un blocco della mem cache e

liberarlo, per fare posto al nuovo

L’algoritmo di sostituzione individua il blocco della

cache da sostituire

per indirizzamento diretto il blocco è fissato

Least Recently Used (LRU): si sostituisce il blocco di

memoria usato meno recentemente

Random: scelta a caso, realizzazione semplice

FIFO: tratto il set come coda circolare, rimpiazzo

blocco in testa, realizzazione semplice

Gerarchie di memoria

©2004 William Fornaciari

- 34 -

©2004 William Fornaciari

17

Organizzazione dei calcolatori

Gerarchie di memoria

Algoritmo LRU

Ogni blocco di memoria cache è dotato di un

contatore di invecchiamento

registro di n bit, se la memoria cache ha 2n blocchi

Ad ogni cache hit il contatore del blocco di

memoria cache interessato viene azzerato, e inoltre

i contatori dei blocchi più “giovani” (<) vengono

incrementati

i contatori dei blocchi più “vecchi” (>) restano

invariati

Gerarchie di memoria

- 35 -

©2004 William Fornaciari

Algoritmo LRU

Ad ogni cache miss occorre caricare in cache un

nuovo blocco

se in cache c’è un blocco libero, lo si occupa

caricando il blocco e azzerandone il contatore

se in cache non c’è alcun blocco libero, si sostituisce

il blocco avente contatore di valore massimo,

azzerandolo

In entrambi i casi i contatori di invecchiamento

degli altri blocchi occupati vengono incrementati

Proprietà di LRU

scelta univoca: ad ogni istante esiste un solo blocco

nella cache con contatore di invecchiamento di valore

massimo

Gerarchie di memoria

©2004 William Fornaciari

- 36 -

©2004 William Fornaciari

18

Organizzazione dei calcolatori

Gerarchie di memoria

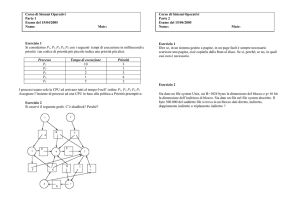

Limiti della cache

Non serve aumentare le dimensioni della cache oltre

una capacità limite, sopra cui le prestazioni del

sistema di memoria smettono di aumentare o

addirittura iniziano a diminuire

guadagno di

prestazioni

saturazione

guadagno di prestazioni =

velocità sistema con cache

velocità sistema senza cache

limite di

guadagno

3

zona di

decadimento

zona di

crescita

2

capacità limite

capacità cache

1

10K

Gerarchie di memoria

100K

1M

10M

100M

- 37 -

©2004 William Fornaciari

Limiti delle cache: motivazioni

Se le dimensioni della cache superano i limiti di validità dei

principi di località dei programmi, nella cache, oltre ai blocchi

usati in modo intenso, vengono inevitabilmente a trovarsi

blocchi spesso liberi (e dunque sprecati)

blocchi invecchiati, che dopo un periodo di uso intenso

vengono ormai acceduti poco di frequente (e che dunque si

potrebbero lasciare senza danno in memoria centrale)

Questo impedisce la crescita indefinita del guadagni di

prestazioni, all’aumentare della capacità della cache

(fenomeno di saturazione)

Inoltre, all’aumentare delle dimensioni della cache il tempo di

accesso alla cache aumenta (per motivi tecnologici), e dunque

superando la capacità limite della cache le prestazioni del

sistema di memoria dotato di cache iniziano a dacadere

Gerarchie di memoria

©2004 William Fornaciari

- 38 -

©2004 William Fornaciari

19

Organizzazione dei calcolatori

Gerarchie di memoria

Prestazioni delle cache

h

C

M

hit rate, tipicamente > 90%

tempo per accedere alle informazioni in cache

penalità di fallimento

tempo addizionale per portare le info nella cache in

caso di miss, la cpu è in stallo

tavg tempo medio di accesso sperimentato dalla CPU

tavg = h C + (1-h) M

Guadagno di prestazioni

tavg con cache/ t senza cache

Gerarchie di memoria

- 39 -

©2004 William Fornaciari

Prestazioni delle cache:

miglioramento h

Aumento dimensione

anche $$$ sale

Aumento dim blocchi a parità dim cache per meglio

sfruttare la località spaziale

ho penalità maggiore in caso di miss

con blocchi grossi molti elementi possono rimanere

inutilizzati

Il progetto deve essere guidato da fattori

costo/prestazione e possibilmente orientato

all’applicazione

Gerarchie di memoria

©2004 William Fornaciari

- 40 -

©2004 William Fornaciari

20

Organizzazione dei calcolatori

Gerarchie di memoria

Tecniche avanzate (cenni)

Portare la cache sullo stesso chip della CPU

costoso, non praticabile se le dim sono grandi

Aggiungo un livello intermedio

L1 typ on-chip, ck elevato (typ dim. decine di Kbyte)

L2 typ off-chip, dim L2> dimL1 (anche Mbyte)

tavg= h1C1 + (1-h1)h2C2 + (1-h1)(1-h2)M

se h1~ h2 ~ 90%: (1-h1)(1-h2) ~ 1%, M poco influente

Cache dati e istruzioni separate

aumento il parallelismo

tuning mirato dei parametri

elevata complessità

Gerarchie di memoria

- 41 -

©2004 William Fornaciari

Dimensione, costo e velocità:

valori tipici ai vari livelli della

gerarchia

cache

CPU

Reg.

dimesione: 200 B

velocità:

3 ns

$/Mbyte:

dim. blocco: 4 B

Gerarchie di memoria

©2004 William Fornaciari

4B

C

a

c

h

e

8B

32 KB / 4MB

6 ns

$256/MB

8B

- 42 -

Memoria virtuale

Memoria

128 MB

100 ns

$2/MB

4 KB

4 KB

disco

20 GB

10 ms

$0.8/MB

©2004 William Fornaciari

21

Organizzazione dei calcolatori

Gerarchie di memoria

Evoluzione della tecnologia

Le previsioni riportate, risalenti al 1992, sono state

già abbondantemente superate

Anno

1992

1995

1998

2001

2004

2007

Feature size 0.5

0.35

0.25

0.18

0.12

0.10

DRAM cap

16M

64M

256M

1G

4G

16G

Gates/chip

300K

800K

2M

5M

10M

20M

2.5

4.0

6.0

8.0

10.0

12.5

off chip MHz 60

100

175

250

350

500

on chip MHz 120

200

350

500

700

1000

Chip

cm2

Gerarchie di memoria

- 43 -

©2004 William Fornaciari

Il gap fra processore e memoria

■

1000

▲

●

Access time (ns)

▲

■

●

▲

100

▲

■

●

●

10

■

1

1980

1985

1990

1995

Year

■

microprocessor clock periods

Gerarchie di memoria

©2004 William Fornaciari

●

SRAM access time

- 44 -

▲

DRAM access time

©2004 William Fornaciari

22

Organizzazione dei calcolatori

Gerarchie di memoria

Evoluzione del Prezzo/Mbyte

100000

■

●

10000

■

1000

$/Mbyte

▲

SRAM

●

DRAM

▲

disk

●

■

■

●

▲

100

■

●

10

▲

1

▲

0.1

1980

1985

1990

1995

Year

Gerarchie di memoria

- 45 -

©2004 William Fornaciari

Esempi di cache in sistemi

commerciali

Esempio di cache

integrata nello

stesso package

del processore

Caratteristica

Organizzazione della cache

Intel Pentium Pro

PowerPC 604

Cache dati e istruzioni separate Cache dati e istruzioni separate

Dimensione della cache

8 KB ciascuna (istr./dati)

Associatività

set associativa a 4 vie

set associativa 4 vie

Politica rimpiazzamento

Dimensione blocco

LRU (approssimato)

32 byte

LRU

32 byte

Politica scrittura

Write-back

Write-back o write-through

Gerarchie di memoria

©2004 William Fornaciari

- 46 -

16 KB ciascuna (istr./dati)

©2004 William Fornaciari

23

Organizzazione dei calcolatori

Gerarchie di memoria

Alpha 21164 Chip

Cache

L1 dati

L1 istruzioni

L2 unificata

TLB

Branch

history

Gerarchie di memoria

- 47 -

©2004 William Fornaciari

Alpha 21164 Chip: cache

L2

Control

Right Half

L2

L1

Data

L1

I

n

s

t

r.

Right Half

L2

Gerarchie di memoria

©2004 William Fornaciari

Cache

L1 dati

L1 istruzioni

L2 unificata

TLB

Branch

history

L2

Tags

- 48 -

©2004 William Fornaciari

24

Organizzazione dei calcolatori

Gerarchie di memoria

Alpha 21164: gerarchia

Obiettivo di progetto primario

migliorare prestazioni della memoria, le prime

versioni di Alpha erano soggette a molti stalli

Regs.

L1 Data

1 cycle latency

8KB, direct

Write-through

Dual Ported

32B lines

L1 Instruction

8KB, direct

32B lines

L2 Unified

8 cycle latency

96KB

3-way assoc.

Write-back

32B/64B lines

L3 Unified

1M-64M

direct

Write-back

Main

Memory

Up to 1TB

32B or 64B

lines

Processor Chip

Gerarchie di memoria

©2004 William Fornaciari

- 49 -

©2004 William Fornaciari

25