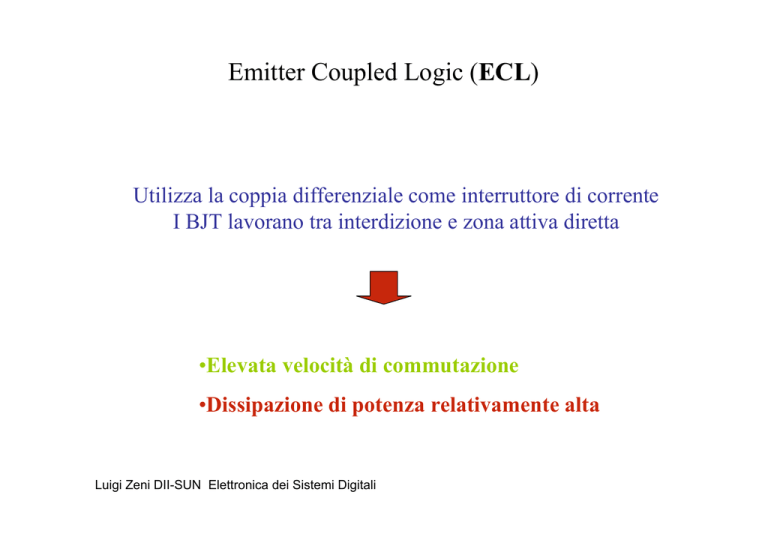

Emitter Coupled Logic (ECL)

Utilizza la coppia differenziale come interruttore di corrente

I BJT lavorano tra interdizione e zona attiva diretta

•Elevata velocità di commutazione

•Dissipazione di potenza relativamente alta

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

Coppia differenziale

1.5

RC

RC

v

v C2

C1

i

C2

Q2

Q1

V REF

α F I EE

i

0.5

i C1 - i C2

C1

vI

1.0

0.0

-0.5

-1.0

-1.5

I EE

-V EE

-12

-10

-8

-6

-4

-2

0

2

vBE1 - vBE2

2 VT

VT = 25mV a temperatura ambiente (300K)

Sono sufficienti 0.3V per la commutazione

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

4

6

8

10

12

Equazioni della corrente

⎛ v BE1 ⎞

⎟⎟

i C1 = IS exp⎜⎜

⎝ VT ⎠

⎛ v BE 2 ⎞

⎟⎟

i C 2 = IS exp⎜⎜

⎝ VT ⎠

i C1 − i C 2

⎛ v BE1 − v BE 2 ⎞

⎟⎟

= α F I EE tanh⎜⎜

2VT

⎠

⎝

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

Coppia differenziale come interruttore di corrente

RC

RC

v C2

v C1

v I > VREF

RC

RC

v

v C2

C1

v I < V REF

I EE

-VEE

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

I EE

-VEE

Valori di tensione

RC

2 kΩ

v

vC2

i

v = - 0.7 V

I

i

C1

+

VREF = - 1 V

Q2

+

0.4V

i

E1

O2

i C1

-1.4V

-

v

O1

C2

Q1

i

RC

2 kΩ

2 kΩ

vC1

0.7V

RC

RC

2 kΩ

-

E2

v = -1.3V

I

Q

1

+

0.4V

i C2

V

REF

Q

2

+

-1.7V

-

I EE = 0.3 mA

i E1

I

EE

= -1 V

i E2

-

0.7V

0.3 mA

-VEE

-VEE

Le tensioni sui collettori sono 0V e 0.6V e non coincidono con quelle di ingresso

NON è una porta logica

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

Invertitore ECL

RC

i B3

Q

2 kΩ

v

v

C1

-0.6 V

3

+

-

BE3

v O1

i

0.1 mA

i

C2

B4

Q

v

BE4

Q

1

2

-1.4 V

0.3 mA

EE

-

V REF = -1.0 V

-0.7 V

v

i E2

I

4

+

C2

Q

i E1

A

I3

A iIN

vI = -0.7 V

-1.3 V

0V

i C1

v

RC

2 kΩ

A

0.1 mA

O2

I4

-V EE

Gli inseguitori di emettitore traslano le tensioni di collettore rendendole uguali a

quelle di ingresso

E’ una porta logica

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

Caratteristica di trasferimento e margini di rumore

-0.5V

V

O1

Pendenza = -1

VOH = -0.7V; VOL = -1.3V

∆V = VOH - VOL = IEERC = 0.6V

-1.0V

ridotta escursione logica

V

O2

VIL

-1.5V

-1.3V

-1.2V

⎛ ∆V ⎞

− 1⎟⎟

VIL = VREF − VT ln⎜⎜

⎝ VT

⎠

Pendenza = -1

-1.1V

V

REF

-1.0V

⎛ ∆V ⎞

− 1⎟⎟

VIH = VREF + VT ln⎜⎜

V

⎝ T

⎠

VIH

-0.9V

-0.8V

-0.7V

vIN

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

⎡ ∆V

⎛ ∆V ⎞ ⎤

− ln⎜⎜

− 1⎟⎟⎥ = 0.22V

NM L = NM H = VT ⎢

2

V

V

⎝ T

⎠⎦

⎣ T

Realizzazione con resistori

RC

2 kΩ

RC

2 kΩ

Q3

Q

4

I

A

Q

v I = -1.3 V

v O1

A

Q

1

2

-1.7 V

i

E1

R EE

i

V REF = -1.0 V

v

E2

O2

A

11.7 kΩ

42 kΩ

42 kΩ

-V

EE

= - 5.2 V

REE = [-1.7V-(-5.2V)]/(0.3mA) = 11.7kΩ

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

Realizzazione con resistori

RC2

RC1

1.85 kΩ

2 kΩ

Q3

Q

4

I

A

V I = -0.7 V

vO1

A

Q

1

Q

2

-1.4 V

i E1

i

REE

V REF = -1.0 V

v

E2

11.7 kΩ

42 kΩ

A

O2

42 kΩ

- VEE = - 5.2 V

iE1 = [-1.4V-(-5.2V)]/(11. 7kΩ ) = 0.325mA

RC1 = 0.6V/(0.325mA) = 1.85V

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

Porta OR-NOR

RC1

2 kΩ

R C2

2 kΩ

v

C1

Q3

A

B

Q

Q

2

C

Y1 = A + B + C

VREF

(-1 V)

Y2 = A + B + C

0.3 mA

I

EE

42 kΩ

42 kΩ

-V EE

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

4

Dipendenza dei parametri dalla temperatura

•I valori logici dipendono dalle tensioni base-emettitore dei BJT

•Le tensioni VBE dipendono dalla temperatura

•Il coefficiente di temperatura della VBE è di circa -1.8mV/K

•La tensione di riferimento (VREF = -1V) non è più (VOH+VOL)/2

•I margini di rumore non sono più simmetrici

Problemi nel funzionamento della porta vista la ridotta escursione logica

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

Generatore di tensione di riferimento

1 kΩ

Q5

- 0.3 V

D5

V

REF

0.3 mA

D1

3.3 kΩ

0.3 mA

11.7 kΩ

- 5.2 V

Il circuito fornisce una tensione di riferimento che varia con la

temperatura verificando sempre la condizione VREF = (VOH+VOL)/2

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

Capacità nell’invertitore ECL

CCB3

RC

2 kΩ

2 kΩ

CCS1

C

Q

3

vC2

CS2

Q

CCB1

CCB2

Q

vI

CCB4

RC

Q

1

2

V REF

vO

I3

4

vO

I EE

0.3 mA

0.1 mA

0.1 mA

I4

-V EE = -5.2 V

Il ritardo di propagazione della porta dipende dalle capacità in figura

e da quella del carico

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

Modello semplificato

v

⎡

⎛

t ⎞⎤

⎟⎟⎥

v C 2 ( t ) = − I EE R C ⎢1 − exp⎜⎜ −

⎝ R C C L ⎠⎦

⎣

τ PHL = 0.69R C C L

C2

2 kΩ

I

EE

R

C

C=C

L

CS2

+C

CB2

+C

CB4

⎛

t ⎞

⎟⎟

v C 2 ( t ) = − I EE R C exp⎜⎜ −

⎝ R CCL ⎠

τ PLH = 0.69R C C L

La effettiva tensione di uscita è traslata di

VBE = 0.7V ma la dinamica è ovviamente

la stessa

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

τP =

τ PHL + τ PLH

= 0.69R C C L

2

Commutazione dell’invertitore ECL

V

-0.5V

vI

L’uscita è normalmente simmetrica, tuttavia

una elevata (10pF) capacità di carico può

portare ad una asimmetria della forma

d’onda di uscita, in particolare ad un

rallentamento della transizione H-L

v

O

-1.0V

τ PHL

vO

τ PLH

-1.5V

0s

5ns

10ns

15ns

20ns

25ns

30ns

t

Gli impulsi (spikes) sull’uscita negata sono dovuti ad un effetto derivativo

della capacità CCB1 che collega direttamente l’uscita invertente con l’ingresso

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

Potenza dissipata dall’invertitore ECL

Nelle porte ECL circola praticamente la stessa corrente, salvo piccole differenze,

sia per uscita alta sia per uscita bassa e dipende dai valori delle resistenze. Nel

caso delle porte analizzate precedentemente la dissipazione di potenza è di circa

2.7mW.

Il prodotto ritardo-potenza è dell’ordine della decina di pJ e ciò non rende adatte

le famiglie ECL alla realizzazione di circuiti VLSI.

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

FAN-OUT dell’invertitore ECL

Il FAN-OUT per uscita bassa non è un problema in quanto le porte in uscita

non assorbono corrente significativa (il BJT di ingresso è interdetto).

Il FAN-OUT per uscita alta dipende dal massimo incremento della corrente,

che attraversa il resistore RC, tollerabile senza che VOH si abbassi troppo. E’

comunque un valore piuttosto alto (N > 150) perché l’incremento di corrente

che attraversa RC è pari alla corrente di uscita divisa per βF + 1.

La vera limitazione al numero di porte in uscita dipende, come per le porte CMOS,

da considerazioni di tipo dinamico.

In particolare, il FAN-OUT è limitato dal rallentamento della transizione H-L per

elevati carichi capacitivi.

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

Prodotto ritardo-potenza di famiglie logiche

commerciali ECL e TTL

100

50 pJ

Low Power TTL

(54L, 74L)

10

TTL (54, 74)

Low Power

Schottky TTL

(54LS, 74LS)

τ p (ns)

ECL II

Schottky TTL

1 pJ

ECL 10K

ECL III

1

ECL 100K

On-Chip VLSI Circuit

Requirements

100 fJ

.1

.1

1

10

Potenza dissipata (mW)

Luigi Zeni DII-SUN Elettronica dei Sistemi Digitali

100