PROGRAMMA MINIMO SVOLTO

Classe

Docente

SALVATORE G. DI VINCENZO - VINCENZO MANCINI 3°B-AUTOMAZ

2015-2016

Ore di lezione svolte

Disciplina

ELETTROTECNICA ED ELETTRONICA

TESTI ADOTTATI

ELETTROTECNICA ED ELETTRONICA vol.1A e vol. 1B

AUTORI: BOBBIO, SAMMARCO

EDITRICE: PETRINI

PROGRAMMA MINIMO SVOLTO

MODULO 1: RETI IN CORRENTE CONTINUA

Obiettivo: utilizzo corretto delle leggi per analisi reti in cc

Anno scolastico

Grandezze elettriche, segnali e relativi parametri

Generatore di tensione e di corrente

Concetti di V.I.R. (legge di Ohm)

Potenza elettrica

Resistenze in serie e parallelo

Principi di Kirchhoff, sovrapposizione degli effetti, Thevenin,

Partitore di tensione e di corrente

Periodo: Settembre-Ottobre

MODULO 2: TRANSITORI CAPACITIVI

Obiettivo: comprendere il funzionamento in regime transitorio di reti RC

Capacità

Condensatore

Dielettrico

Rigidità dielettrica

Collegamenti fra condensatori (serie – parallele)

legge di carica e scarica del condensatore attraverso una resistenza

Periodo: novembre

MOD 3.6.19./1 Programma svolto

PROGRAMMA MINIMO SVOLTO

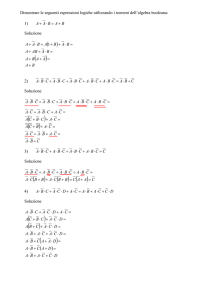

MODULO 3: RETI COMBINATORIE

Obiettivo : conoscere la componentistica di base relativa all'elettronica digitale SSI e MSI, saper utilizzare

l'algebra di boole per la minimizzazione delle funzioni logiche, saper leggere ed interpretare manuali tecnici

relativi

Analisi e sintesi di reti logiche combinatorie

Algebra di commutazione e operazioni binarie NOT, AND, OR

Tabelle della verità

1^ forma canonica per la sintesi di reti a partire dalle tabelle

Teoremi dell’algebra di Boole per la semplificazione di espressioni logiche

Teorema di De Morgan

Porte logiche NAND, NOR, XOR,X-NOR

Reti MSI

Multiplexer/demultiplexer logici

Encoder, decoder binario ottale,decoder BCD/7 segmenti

Sommatori (Half Adder e Full Adder)

Periodo: dicembre-marzo

MODULO 4: RETI SEQUENZIALI

Obiettivo : conoscere la componentistica di base, comprendere diagrammi temporali di segnali digitali,

analizzare e progettare contatori asincroni con FF e dispositivi integrati

Reti logiche sequenziali

I latch

I Flip-flop e le loro proprietà

Ingressi di Enable preset, Clear

FF JK, edge triggered e temporizzazioni

Flip-Flop di tipo D

Registri e Contatori integrati

analisi e progetto di contatori/divisori asincroni

analisi e progetto contatori sincroni

Periodo: aprile-maggio

LABORATORIO:

Tecnologia delle resistenze: tipi e valori commerciali, codice colori, tolleranza, potenziometri

Uso del multimetro come ohmmetro, voltmetro, amperometro

Partitore di tensione

Ponte di Wheastone

Termistori (NTC – PTC)

Risposta al gradino di un circuito RC

MOD 3.6.19./1 Programma svolto

PROGRAMMA MINIMO SVOLTO

Prove con porte logiche

Interruttore crepuscolare

Flip – Flop tipo SR

Trigger di SCHMITT

4051 – 400106

4051 – Immunità al rumore (in una porta CMOS)

Oscillatore porte NOT

Oscillatore con 555

Contatori

Decodificatori

Comparatore di maggioranza 40085//7485

4040//4020//4060

Tecniche di saldatura

Prove di saldatura

Contatore 4017

I rappresentanti di classe

I docenti

Prof. Salvatore Giuseppe Di Vincenzo

Prof. Vincenzo Mancini

Data: 08/06/2016

MOD 3.6.19./1 Programma svolto