ElapBe1

21/09/2015

ElapBe1

21/09/2015

Ingegneria dell’Informazione

Esercitazione Be1: parte B - 1

• Esercizi sugli argomenti svolti nelle lezioni B1-B4

ELETTRONICA APPLICATA

E MISURE

• Raccomandazione di risolvere come homework

prima della lezione

Dante DEL CORSO

• Soluzione e chiarimenti (a richiesta) in aula

Be1 – Esercizi parte B (1)

»

»

»

»

• Argomenti esercizi parte B - 1:

Interfacciamento statico

Ritardi

Diagrammi temporali

Massima cadenza clock

–

–

–

–

Circuiti con Flip-Flop

Diagrammi temporali senza ritardi

Calcolo dei ritardi, diagrammi con ritardi

Valutazione della massima cadenza di clock

AA 2015-16

21/09/2015 - 1

ElapBe1 - 2014 DDC

21/09/2015 - 2

ElapBe1 - 2014 DDC

Per le esercitazioni sono disponibili stampe con spazio per annotare la

soluzione a ciascuna domanda.

© 2014 DDC

1

© 2014 DDC

2

ElapBe1

21/09/2015

ElapBe1

21/09/2015

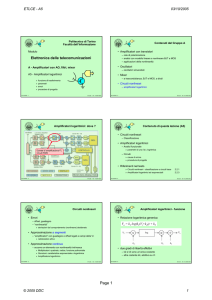

Esercitazione Be1: Elenco esercizi

Macchina a Stati Finiti (FSM)

• Obbiettivi di questi esercizi

• Le uscite di un contatore evolvono secondo la

successione dei numeri interi:

– Analisi di circuiti con porte e flip-flop

– Valutazione di specifiche temporali

– (Richiami su interfacciamento statico)

– 1, 2, 3, 4, 5, …

– La commutazione avviene in corrispondenza del clock

• E’ possibile realizzare circuiti sequenziali in cui

• Be.1: Analisi di Flip-Flop JK

– La sequenza di stati è arbitraria (ad esempio 4, 2, 1, 3, 5, …)

– La commutazione avviene sempre in corrispondenza del

clock

– Il passaggio da uno stato all’altro è condizionato da segnali

esterni

• Be.2: Analisi di circuito sequenziale

– Comportamento ideale (no ritardi)

– Analisi con ritardi, frequenza max di clock

– (resistenza di pull-up, carico capacitivo, decodifica stati)

• Macchine a Stati Finiti (FSM)

• Be.3: Circuiti antirimbalzo

21/09/2015 - 3

© 2014 DDC

ElapBe1 - 2014 DDC

3

21/09/2015 - 4

© 2014 DDC

ElapBe1 - 2014 DDC

4

ElapBe1

21/09/2015

ElapBe1

21/09/2015

Macchine a Stati Finiti (FSM)

Esercizio Be1.1: JK FF come FSM

• Una FSM comprende elementi di memoria (Flip-Flop)

• Progettare un circuito (Finite State Machine: FSM) che

usa un FF-D, e si comporta come un FF-JK:

• Lo stato degli elementi di memoria identifica lo stato

del sistema (N FF 2N stati)

• I passaggi da stato a stato

sono rappresentati con archi,

condizionati da variabili

interne e di ingresso

• Ad ogni stato corrisponde una

combinazione delle uscite

A

D

– Due ingressi: J, K

Una uscita: Q

– Comando RESET;

(forza Q = 0)

B

– Due soli stati:

Q=HeQ=L

C

– Comando diretto

RESET:

porta Q a 0

• Questa rappresentazione è un diagramma degli stati

21/09/2015 - 5

© 2014 DDC

ElapBe1 - 2014 DDC

5

21/09/2015 - 6

© 2014 DDC

RETE DI

USCITA

J

K

Q

RETE DI

STATO FUTURO

Q

D

CK

R

RESET

ElapBe1 - 2014 DDC

6

ElapBe1

21/09/2015

ElapBe1

21/09/2015

Esercizio Be1.1-a: diagramma stati

Esercizio Be1.1-b: FSM completa

Variabile D ottenuta

da J, K, Q con rete

combinatoria che

realizza l’equazione di

stato futuro:

Comportamento del JK-FF

J

K

STATO

ATTUALE (Q)

STATO

FUTURO (D)

0

0

0

0

0

0

1

1

0

1

0

0

0

1

1

0

1

0

0

1

1

1

0

1

1

1

0

1

1

1

1

0

Equazione di

stato futuro:

RETE DI

USCITA

J

A

K

D = Qn+1 = Q* J + Q K*

D = Q* J + Q K*

Q

B

RETE DI

STATO FUTURO

L’uscita è direttamente

la Q del FF

Q

D

CK

R

RESET*

21/09/2015 - 7

© 2014 DDC

ElapBe1 - 2014 DDC

7

21/09/2015 - 8

© 2014 DDC

ElapBe1 - 2014 DDC

8

ElapBe1

21/09/2015

ElapBe1

21/09/2015

Esercizi su circuiti sequenziali

•

Esercizio completo su circuito sequenziale (2-3 FF)

•

Esempi di quesiti:

a.

b.

c.

d.

e.

f.

Esercizio Be1.2: circuito sequenziale

•

Analisi temporale “ideale” (senza ritardi)

Analisi temporale con ritardi

Calcolo resistenza di pull-up

Decodifica di stati

Calcolo dell’effetto di un carico capacitivo

Calcolo della frequenza massima del clock

Nello schema in figura i tre FF hanno le uscite Q

inizializzate a 0. Il clock ha duty cycle di 0.5.

B1 è un buffer OC, con RON = 40 Ω, IOH = 200 μA,

I1 un inverter con ingresso a trigger. (SE1109)

Val

F

CK

–

21/09/2015 - 9

© 2014 DDC

Numerosi esercizi svolti di questo tipo si trovano nel sito di

“Sistemi Elettronici”:

da areeweb …. (in fondo) 01EKL scritti di esame risolti

A

Rpu

Q2

D Q

FF1

Q1

D Q

Q

FF2

Q3

D Q

B1

B1

FF3

Out

C

I1

a. Tracciare le forme d’onda ai nodi A, Q1, Q2, Q3, Out

nell’ipotesi che tutti i componenti abbiano ritardo nullo per i

primi 3 periodi del clock CK (capacità C = 0).

ElapBe1 - 2014 DDC

9

21/09/2015 - 10

© 2014 DDC

ElapBe1 - 2014 DDC

10

ElapBe1

21/09/2015

ElapBe1

21/09/2015

Esercizio Be1.2a1: segnali

Esercizio Be1.2.a2: sequenza di stati

• Sequenza di segnali (senza ritardi)

CK

___

___

___

___

___

__/

\___/

\___/

\___/

\___/

Q1

__

Il clock è attivo su entrambi i fronti (LH FF1, HL FF2).

FF 3 è collegato come divisore modulo 2, e commuta sui fronti di

discesa di Q2* (salita di Q2).

C = 0; tra Q3 e OUT solo inversione di stato logico

CK

Q2

A

__

__

Q1

Q2

A

Q3

OUT

21/09/2015 - 11

© 2014 DDC

ElapBe1 - 2014 DDC

11

21/09/2015 - 12

© 2014 DDC

1a

1b

2a

2b

3a

3b

4°

_________

_________

_________

____/

\_________/

\_________/

\_________/

_______________

_____________________________

_

\_________/

\_________/

___________________

___________________

_____/

\___________________/

\_

___________________

___________

_______________/

\___________________/

_______________________________________

_______________/

\___________

_______________

___________

Transizioni con ritardo

\_______________________________________/

rispetto al clock (unico

valore convenzionale)

ElapBe1 - 2014 DDC

12

ElapBe1

21/09/2015

ElapBe1

21/09/2015

Esercizio Be1.2b1: valutazione ritardi

Esercizio Be1.2-b2: ritardi

• Sequenza di segnali (con ritardi)

Val

F

CK

A

D Q

FF1

Q1

Q2

D Q

Q

FF2

Q3

D Q

FF3

B1

B1

Out

C

Tsu = 3 ns, Th = 2 ns (tutti i FF) ;

Tckq = 5 ns (tutti i FF, sia LH che HL)

porta NAND e trigger di uscita I1: TLH = 3ns , THL = 4 ns,

buffer B1: Tp = 6 ns (per entrambe le transizioni)

© 2014 DDC

_____

_____

___

_____/

\______/

\______/

Q1

__

Q2

__

__

I1

b. Tracciare con asse dei tempi tarata le forme d’onda

per due periodi di clock ai nodi A, Q1, Q2, Q3, Out

con i parametri dinamici indicati (sempre per C = 0).

21/09/2015 - 13

CK

Rpu

A

ElapBe1 - 2014 DDC

13

21/09/2015 - 14

© 2014 DDC

ElapBe1 - 2014 DDC

14

ElapBe1

21/09/2015

ElapBe1

21/09/2015

Eserc. Be1.2c: diagramma temporale

–

–

–

–

•

•CK

•A

•Q1

•Q2

•Q3

•OUT

Esercizio Be1.2d: calcolo R pullup

c. L’inverter con ingresso a trigger ha soglie Vs1 = 3V e

Vs2 = 2V, Iih = 0,3 mA, Iil = - 0,3 mA.

Determinare i valori min/max della Rpu che

garantiscono la commutazione di Out (Val = 5V)

Tsu = 3 ns, Th = 2 ns (tutti i FF) ;

Tck->Q = 5 ns (tutti i FF, per L-> H e H->L)

porta NAND e trigger di uscita I1: TLH = 3ns , THL = 4 ns,

buffer B1: Tp = 6 ns (per entrambe le transizioni)

– La tensione nello stato H deve superare la soglia Vs1;

questa condizione fissa un massimo al valore della Rpu.

1a

1b

2a

2b

3a

_______________

_______________

_

____/

\_______________/

\_____________/

– Nello stato H, nella Rpu scorre una corrente

Irph = Ioh + Iih = 0,2 + 0,3 = 0,5 mA.

Tensione all’uscita OC: Val – Irph x Rpu ,

che deve essere (almeno) uguale a Vs1 (3 V).

_______________________|-4-|

|-3-|_______________________

|

\___________|___/

|

|

-5-|_______________|___________ -5-|

_______/

|

\___________________________

|

-5-|___________________________ -5-|

_______________________/

\___________

|-5-|_______________________________________

___________________________/

___________________________|-6+4-|

Ritardi effettivi (in ns),

\_________________________________

– (Val – Vs1)/Rpumax = Irph;

Rpumax = (5–3)V/0,5mA = 4 kΩ

– Una resistenza Rpu più alta farebbe scendere la tensione

stato H sotto la soglia Vs1, bloccando Out nello stato H.

valutati caso per caso

21/09/2015 - 15

© 2014 DDC

ElapBe1 - 2014 DDC

15

21/09/2015 - 16

© 2014 DDC

ElapBe1 - 2014 DDC

16

ElapBe1

21/09/2015

ElapBe1

21/09/2015

Esercizio Be1.2e: calcolo R pullup

Eserc. Be1.2f: andamento Vc e Vout

d. Analizzare il comportamento

dinamico dell’anello

B1-C-I1-FF3. Tracciare

l’andamento qualitativo di

Q3, della tensione ai capi

di C e della Vout.

c. ….. Determinare i valori minimo e massimo della

Rpu che garantiscono la commutazione di Out

(Val = 5V)

– Perché il trigger riconosca lo stato L la tensione di ingresso

deve scendere sotto Vs2. Per V = Vs2 = 2V nell’uscita OC

circola una corrente IL pari a 2V/40Ω = 50mA. Questa

corrente proviene dalla resistenza Rpu e (per soli 0,3 mA)

dall’ingresso del trigger. Trascurando quest’ultima si ha:

Rpumin = 3V/50mA = 60 Ω

© 2014 DDC

CK1

D Q

Rpu

FF3

B1

B1

Out

C

I1

– Tra Q3 e Out buffer OC caricato da C; Vc ha andamento

esponenziale, con tau = C Rpu in salita e tau = C

(Rpu//Ron) in discesa. Le variazioni di stato sono rilevate da

I1 con ritardi diversi (> per LH). Out riportata a D del FF3

forma un divisore modulo due. La max frequenza operativa

è limitata dal ritardo della catena B1-C-I1 e ritardi del FF.

– Per la transizione LH (caso peggiore), si ha (CK di FF3):

Tckmin(FF3) = Tckq(FF3) + Tp(B1) +

Thlc(ritardo dovuto a C e Rpu) + Thl(I1) + Tsu(FF3).

– Resistenze di valore più basso determinano una tensione allo

stato L maggiore della Vs2, e il trigger di uscita rimane

bloccato nello stato L. Il valore limite molto basso per Rpu

deriva dalla soglia relativamente alta del trigger (2 V).

21/09/2015 - 17

Val

Q3

ElapBe1 - 2014 DDC

17

21/09/2015 - 18

© 2014 DDC

ElapBe1 - 2014 DDC

18

ElapBe1

21/09/2015

ElapBe1

21/09/2015

Esercizio Be1.2g: frequenza max

Esercizio Be1.2h: frequenza max

Valutazione quantitativa di Thlc

e. Determinare la massima frequenza del clock CK che

permette il funzionamento di questa parte del circuito con

Rpu = 1kΩ, C= 25pF, Val = 5V.

– Tensione iniziale (stato L):

VL = 204 mV (accettabile 0 V in prima approssimazione)

Per determinare il tempo T1 richiesto per raggiungere Vs1 occorre

risolvere la relazione

Vc(T1) = Vs1 = A + B e^-T1/tau

3 V = 4,5 – 4,3 e^-T1/tau;

e^-T1/tau = 1,5/4,3 = 0,349

T1 = 1,053 tau = 1,053 x 25 ns = 26,3 ns

Tckmin(FF3) = 5 + 6 + 26,3 + 4 + 3 = 44,3 ns

Questo periodo corrisponde a tre cicli del clock CK (punto a), quindi

Fmax(CK) = 22,5 MHz

– L’asintoto è VH = Val – Rpu x Irph = 5 – 0,5 = 4,5V

– Vc(t) può essere espresso nel modo standard (sistemi del I

ordine):

Vc(t) = A + B e^-t/tau;

– B = V(∞) = 4,5 V;

A = V(0) – B = - 4,3 V

– Tau = R x C = 1 k x 25 pf = 25 ns

21/09/2015 - 19

© 2014 DDC

ElapBe1 - 2014 DDC

19

21/09/2015 - 20

© 2014 DDC

ElapBe1 - 2014 DDC

20

ElapBe1

21/09/2015

ElapBe1

21/09/2015

Esercizio Be1.3: circuiti anti-rimbalzo

Es. Be1.3-a: anti-rimbalzo con FF SR

Occorre dare un comando “manuale” (azionamento

di un deviatore) a un sistema elettronico.

Quando il deviatore commuta,

il contatto rimbalza più volte

causando transizioni multiple

1. Inserire un circuito per eliminare i comandi spuri

dovuti ai rimbalzi meccanici

A

2. Come realizzare la stessa funzione per un

interruttore (chiude verso massa, con R di pull-up)?

3. Come realizzare le stesse funzioni a SW, utilizzando

come ingresso un interruttore senza antirimbalzo?

© 2014 DDC

B

VAL

OUT

RPU1

Il segnale OUT ha una

singola commutazione

4. Per tutti questi casi, indicare come determinare il

valore degli eventuali componenti passivi.

21/09/2015 - 21

Resistenze di pull-up.

Portano allo stato 1 il

morsetto non

collegato a massa

ElapBe1 - 2014 DDC

21

21/09/2015 - 22

© 2014 DDC

RPU2

A

B

S

Q*

R

Q

OUT

ElapBe1 - 2014 DDC

22

ElapBe1

21/09/2015

ElapBe1

21/09/2015

Es. Be1.3-b: Segnali nell’antirimbalzo

Es. Be1.3-c: varianti anti-rimbalzo 1

• Ingressi SET e RES attivi bassi (comanda lo ”0”)

• Quale circuito usare se il deviatore commuta i due

punti verso l’alimentazione (anziché verso massa)?

– SET* comanda direttamente Q; da Q comando a Q*

– RES* comanda direttamente Q*; da Q* comando a Q

POSIZ. SW

A = SET*

B = RES*

Q

Q*

21/09/2015 - 23

© 2014 DDC

B

____A________

B

___A___

_____/

\_________/

______

__________

\/\/\_____/\/

\/\/\___

_______________

______

__/\/

\/\___/\/

______________

___

_______/

\_______/

________

_________

\____________/

\___

21/09/2015 - 24

ElapBe1 - 2014 DDC

23

© 2014 DDC

ElapBe1 - 2014 DDC

24

ElapBe1

21/09/2015

ElapBe1

21/09/2015

Es. Be1.3-d: varianti anti-rimbalzo 2

Es. Be1.3-e: varianti anti-rimbalzo 3

• Come realizzare la stessa funzione se l’organo di

comando è un interruttore (anziché un deviatore)?

• Come realizzare le stesse funzioni a SW, utilizzando

come ingresso un interruttore senza antirimbalzo?

– Si può usare una rete RC passa-basso che “filtra” i rimbalzi,

seguita da un trigger che trasforma la transizione lenta

(dovuta alla rete RC) in gradino.

– Il SW deve leggere lo stato dell’interruttore periodicamente, e

accettare la variazione solo quando lo stato viene mantenuto

per più campionamenti consecutivi.

– L’intervallo su cui viene valutata questa “permanenza” deve

essere maggiore della durata massima dei rimbalzi

• Come determinare il valore degli eventuali

componenti passivi?

– Le resistenze di pull-up o pull-down devono essere calcolate

tenendo conto di VIH, VIL e delle correnti di ingresso.

– Le resistenze in serie agli ingressi devono garantire livelli

logici corretti agli ingressi, tenendo conto della corrente

circolante negli stessi (minima nei circuiti MOS).

– Nota R, il condensatore va calcolato per il ritardo voluto.

21/09/2015 - 25

© 2014 DDC

ElapBe1 - 2014 DDC

25

21/09/2015 - 26

© 2014 DDC

ElapBe1 - 2014 DDC

26

ElapBe1

21/09/2015

Altri esercizi

• Esempi di esercizi risolti su circuiti sequenziali sono

nell’archivio scritti di Sistemi Elettronici

– Seguire: Materiale didattico > Scritti … Sistemi Elettronici

Ogni scritto ha un esercizio di analogica, uno di digitale

(circuiti con FF e porte), e domande a risposte chiuse

• Le domande su reti sequenziali riguardano:

–

–

–

–

Diagrammi temporali senza ritardi

Diagrammi temporali con valutazione dei ritardi

Valutazione della massima frequenza operativa

Domande su argomenti trattati a “Sistemi e Tecn. Elettron.”:

» Calcolo di resistenze di pull-up, verifiche di interfacciamento

» Valutazione dei ritardi causati da carichi capacitivi

21/09/2015 - 27

© 2014 DDC

ElapBe1 - 2014 DDC

27