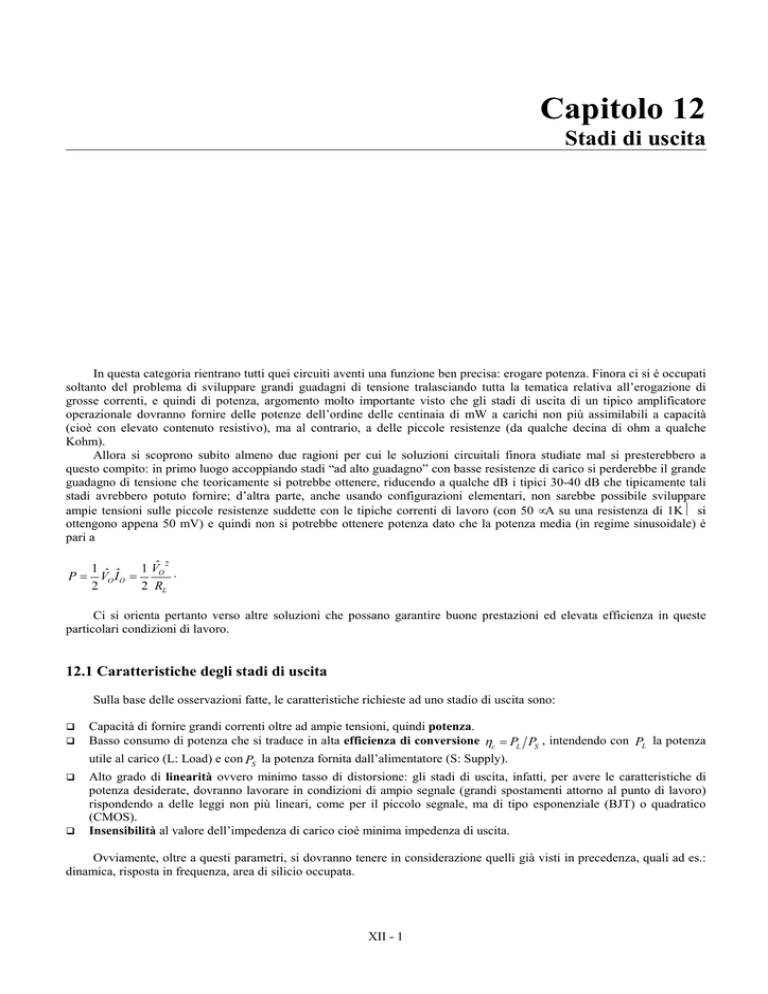

Capitolo 12

Stadi di uscita

In questa categoria rientrano tutti quei circuiti aventi una funzione ben precisa: erogare potenza. Finora ci si è occupati

soltanto del problema di sviluppare grandi guadagni di tensione tralasciando tutta la tematica relativa all’erogazione di

grosse correnti, e quindi di potenza, argomento molto importante visto che gli stadi di uscita di un tipico amplificatore

operazionale dovranno fornire delle potenze dell’ordine delle centinaia di mW a carichi non più assimilabili a capacità

(cioè con elevato contenuto resistivo), ma al contrario, a delle piccole resistenze (da qualche decina di ohm a qualche

Kohm).

Allora si scoprono subito almeno due ragioni per cui le soluzioni circuitali finora studiate mal si presterebbero a

questo compito: in primo luogo accoppiando stadi “ad alto guadagno” con basse resistenze di carico si perderebbe il grande

guadagno di tensione che teoricamente si potrebbe ottenere, riducendo a qualche dB i tipici 30-40 dB che tipicamente tali

stadi avrebbero potuto fornire; d’altra parte, anche usando configurazioni elementari, non sarebbe possibile sviluppare

ampie tensioni sulle piccole resistenze suddette con le tipiche correnti di lavoro (con 50 µA su una resistenza di 1KΩ si

ottengono appena 50 mV) e quindi non si potrebbe ottenere potenza dato che la potenza media (in regime sinusoidale) è

pari a

2

1

1 VˆO .

P = VˆO IˆO =

2

2 RL

Ci si orienta pertanto verso altre soluzioni che possano garantire buone prestazioni ed elevata efficienza in queste

particolari condizioni di lavoro.

12.1 Caratteristiche degli stadi di uscita

Sulla base delle osservazioni fatte, le caratteristiche richieste ad uno stadio di uscita sono:

Capacità di fornire grandi correnti oltre ad ampie tensioni, quindi potenza.

Basso consumo di potenza che si traduce in alta efficienza di conversione ηc = PL PS , intendendo con PL la potenza

utile al carico (L: Load) e con PS la potenza fornita dall’alimentatore (S: Supply).

Alto grado di linearità ovvero minimo tasso di distorsione: gli stadi di uscita, infatti, per avere le caratteristiche di

potenza desiderate, dovranno lavorare in condizioni di ampio segnale (grandi spostamenti attorno al punto di lavoro)

rispondendo a delle leggi non più lineari, come per il piccolo segnale, ma di tipo esponenziale (BJT) o quadratico

(CMOS).

Insensibilità al valore dell’impedenza di carico cioè minima impedenza di uscita.

Ovviamente, oltre a questi parametri, si dovranno tenere in considerazione quelli già visti in precedenza, quali ad es.:

dinamica, risposta in frequenza, area di silicio occupata.

XII - 1

Stadi di uscita

12.1 Classificazione

E’ possibile classificare gli stadi di uscita in base al modo in cui lavorano gli stessi transistori che li compongono. Si

hanno principalmente quattro categorie, ma da queste, per combinazione, se ne possono ottenere altre.

CLASSE A

I transistori si trovano sempre in regione attiva. Come si può

vedere dalla fig. 12.1, l’angolo di conduzione del transistore è

pari a 2π, ovvero l’intervallo di conduzione è uguale a T: si ha

sempre conduzione, e questo perché l’ampiezza del segnale si

mantiene sempre minore del valore della corrente di

polarizzazione: I C > IˆC

Fig. 12.1

Angolo di conduzione dello stadio in classe A

Fig. 12.2

Angolo di conduzione dello stadio in classe B

CLASSE B

I transistori stanno per metà del tempo in regione attiva e per

metà in interdizione. Dalla fig. 12.2 si vede che l’angolo di

conduzione è pari a π, cioè, l’intervallo di conduzione è pari ad

un semiperiodo.

CLASSE AB

E’ una via di mezzo tra la classe A e la classe B: l’intervallo

di conduzione è leggermente superiore a quello della classe B,

ma comunque inferiore a quello della classe A (fig. 12.3).

Fig. 12.3

Angolo di conduzione dello stadio in classe AB

CLASSE C

E’ caratterizzato da un intervallo di conduzione minore di un

semiperiodo (fig. 12.4).

Fig. 12.4

XII - 2

Angolo di conduzione dello stadio in classe C

Stadi di uscita

12.2 Stadio di uscita in classe A

12.2.1 Realizzazione in tecnologia bipolare

Uno stadio d’uscita in classe A, in tecnologia bipolare, si può realizzare con una configurazione a collettore comune

(fig. 12.5):

VCC

IB

vI

Q1

vO

Q3

Q2

RL

VEE

Fig. 12.5

Circuito di un inseguitore in classe A

nella quale si può considerare, per un’alimentazione simmetrica:

V EE = −VCC

(12.1)

Nell’analisi del circuito di fig. 12.5 si deve tenere conto del fatto che, essendo uno stadio d’uscita, esso deve poter

trattare segnali con grandi escursioni in ampiezza, pertanto l’analisi per piccolo segnale non può essere usata; si passa

quindi ad un’analisi di ampio segnale.

Dall’osservazione del circuito, nell’ipotesi che Q1 stia in regione attiva, si ricava la caratteristica di trasferimento:

vI = vBE1 + vO

(12.2)

La vBE1 adesso non può più essere considerata costante e circa uguale a 0.7V ma deve essere espressa in funzione

della corrente in Q1:

v I = VT ln

i E1

+ vO

I ES 1

(12.3)

Trascurando la corrente nella base di Q1, iE1 sarà:

i E1 = I C 2 +

vO

RL

(12.4)

La I C 2 è fissata dallo specchio formato da Q2 e Q3 e quindi dal loro rapporto di aree, si pone perciò:

I C1 = I C 2 = I Q

(12.5)

Sostituendo le (12.4) e (12.5) nella (12.3) si arriva all’espressione della transcaratteristica d’uscita di Q1 che è quella

data dalla (12.6) e rappresentata nella fig. 12.6.

XII - 3

Stadi di uscita

vO

VCC-|vCE SAT|-vBE1 MAX

vBE1

(1)

VCC-|vCE SAT|

vI

-RLIQ

v

IQ + O

RL

v I = VT ln

I

ES 1

+v

O

(12.6)

(2)

-VCC+vCE2 SAT

Fig. 12.6

Transcaratteristica dell’inseguitore in classe A (versione bipolare)

Quando vI ≅ 0.7V si può immaginare vO ≅ 0 , all’aumentare di vI , che può arrivare fino a VCC − v CEsat dovendo

garantire nella migliore delle ipotesi almeno una vCEsat per lo stadio pilota, vO cresce fino a raggiungere il massimo valore

consentito che, come si vede dal circuito di fig. 12.5, è pari a VCC − v CEsat − v BE1 max .

Per quanto riguarda la linearità, dalla (12.6) si scopre che essa sarà tanto maggiore quanto più il termine vO RL sarà

piccolo rispetto ad I Q , ne segue quindi che, per R L piccole, si ha una piegatura maggiore ossia un effetto sensibile di non

linearità. In ogni caso, per piccoli valori di vI ci sarà un inseguimento pressoché lineare.

Con le vI negative, per abbassare la vO si dovrà “tirare” corrente dalla R L . La I Q però è fissata dallo specchio, parte

di essa viene dalla R L , parte da Q1; man mano che vO diventa più negativa, sempre più corrente scorrerà su R L . Per piccoli

valori di R L , il minimo valore teorico di vO si ottiene quando tutta la corrente I Q scorrerà sul carico (con conseguente

spegnimento di Q1) , si avrà quindi vO = I Q RL ; l’uscita si è saturata prima della saturazione di Q2. Per grandi valori di R L ,

può accadere che prima che la corrente I Q finisca per scorrere tutta sul carico, il transistore Q2 sia uscito dalla regione

attiva andando in saturazione; il minimo valore per vO diventa vO = VEE + vCEsat .

Un vantaggio di questa configurazione sta nell’alta linearità ottenibile: se la corrente di polarizzazione è molto

grande, maggiore della massima corrente di segnale, il termine logaritmico nella (12.6) tende ad essere costante ed

indipendente da vO . Questo beneficio si paga però in termini di consumo di corrente e quindi di dissipazione, a spese,

come si vedrà, dell’efficienza di conversione. Un’altra peculiarità di questo stadio è la buona risposta in frequenza e

quindi la velocità, tipiche dello stadio a collettore comune. Per quanto riguarda però la dinamica, si è svantaggiati in

quanto ci si ritrova una massima tensione sviluppabile legata alla I Q ; difatti, per le componenti negative del segnale, la

corrente al carico essendo fornita da Q2 sarà limitata da quella specchiata ovvero da I Q . Per le componenti positive invece

non vi sono limiti, dato che Q1 farà scorrere la corrente che serve, indipendentemente da I Q .

12.2.2 Efficienza di conversione

L’efficienza di conversione è definita come ηc = PL PS , si deve quindi calcolare la potenza utile ceduta al carico, PL

e quella fornita dall’alimentazione, PS . La massima ampiezza di corrente in uscita è pari ad I Q :

iˆO = I Q

(12.7)

d’altra parte si ha:

vˆO = iˆO RL

(12.8)

XII - 4

Stadi di uscita

allora, la potenza media vale:

2

PL =

1 2

1 vˆO

I Q RL =

2

2 RL

(12.9)

La potenza erogata dall’alimentatore è data dalla somma di quella relativa all’alimentazione negativa e di quella

relativa all’alimentazione positiva. La prima è:

PEE = I Q VEE = I QVCC

(12.10)

poiché I Q è fissata ed è la massima corrente che l’alimentazione negativa può fornire.

La seconda, cioè la corrente ceduta da VCC , varia con un’ampiezza massima pari a I Q attorno ad I Q stessa: diventa

2 I Q in corrispondenza del massimo positivo di v I , e 0 quando tutta la corrente di Q2 va in RL cioè nel massimo negativo di

v I . La potenza media allora è data dalla (12.11):

PCC = VCC I Q

(12.11)

In definitiva la potenza totale fornita dall’alimentazione è:

PS = PCC + PEE = 2 I QVCC

(12.12)

L’efficienza di conversione è data dal rapporto tra la PL della (12.9) e la PS della (12.12):

1 2

I Q RL

1 I Q RL 1 vˆO

ηc = 2

=

=

2 I QVcc 4 Vcc

4 Vcc

(12.13)

La v̂O si può ricavare come media tra il valore massimo di vO :

v O max = VCC − v CEsat − v BE1 max

(12.14)

e quello minimo:

v O min = V EE + v CEsat

(12.15)

Si ottiene:

vˆ O =

VCC − vCEsat − v BE1 max − V EE − v CEsat 2VCC − 2v CEsat − 0.8

≅

2

2

(12.16)

Idealizzando lo stadio in classe A, si può assumere:

vˆ O = VCC

(12.17)

Sostituendo la (12.17) nella (12.13) si ha, infine:

η c = 0.25 = 25%

(12.18)

che rappresenta il rendimento massimo, teorico, di uno stadio in classe A.

XII - 5

Stadi di uscita

In realtà però si deve considerare il contributo delle vCEsat e della v BE max , come indicato nella (12.16), ottenendo in

prima approssimazione:

vˆ O = VCC − 0.6

(12.19)

Si capisce quindi che, dal momento in cui si ha a che fare con tensioni non più dell’ordine delle decine di Volt (come

accadeva fino a qualche tempo fa), ma di qualche Volt (com’è richiesto da quasi tutte le odierne applicazioni), il

rendimento reale diventa sensibilmente più basso di quello ideale.

12.2.3 Realizzazione in tecnologia CMOS

Un circuito analogo al precedente, in tecnologia CMOS, si può ottenere con un drain comune, come mostrato nella

fig. 12.7, dove si è posto:

VSS = −VDD

(12.20)

VDD

IB

vI

M1

vO

M3

M2

RL

VSS

Fig. 12.7

Circuito di un inseguitore in classe A

La relazione ingresso - uscita si ricava allo stesso modo del caso precedente ed è data dalla (12.21), nella quale si nota

che stavolta non c’è una dipendenza di tipo “logaritmo” con la v O , bensì una dipendenza del tipo “radice quadrata”.

Per la linearità valgono le stesse considerazioni fatte precedentemente, ma la v GS adesso, contrariamente alla v BE ,

può variare di parecchio per cui si può avere anche vGS max >> vGSpol (ad esempio 2.5V con 1V), mentre la v BE max poteva

oscillare soltanto di centinaio di mV. La transcaratteristica è rappresentata in fig. 12.8.

vO

VDD-|vDS SAT|-vGS1 MAX

vO

RL

v I = v GS 1 + vO = VT +

+ vO

W

Kn

L 1

IQ +

vGS1 VDD-|vDS SAT|

(1)

(2)

Fig. 12.8

vI

-RLIQ

-VSS+vDS2 SAT

Transcaratteristica dell’inseguitore in classe A (versione CMOS)

XII - 6

(12.21)

Stadi di uscita

12.2.4 Conclusioni

Si è visto che il vantaggio essenziale dello stadio in classe A, sia per il bipolare che per il MOS, consiste nell’alta

linearità ottenibile. A questo si oppone però l’elevata dissipazione necessaria per poter avere delle caratteristiche di uscita

accettabili, e questo si è tradotto in un basso rendimento di conversione.

Per ottenere prestazioni migliori, a scapito però, come si vedrà, della linearità, si va verso lo stadio in classe B.

12.3 Stadio in classe B (PUSH-PULL)

12.3.1 Realizzazione in tecnologia bipolare

Nella fig. 12.9 è mostrato uno stadio d’uscita in classe B, realizzato tramite due inseguitori.

VCC

Q2

vI

vO

Q1

RL

VEE

Fig. 12.9

Circuito per un finale in classe B

Si pone:

V EE = −VCC

(12.22)

Si può scrivere l’equazione alla maglia comprendente le due basi e i due emettitori:

v BE 2 + v EB1 = 0

(12.23)

La (12.23) porta ad un'importante conclusione: le due v BE non possono essere contemporaneamente positive, vale a

dire che i due transistori non possono essere simultaneamente accesi; allora, in assenza di segnale, poiché iO = 0 , entrambi i

transistori devono essere spenti perché, se così non fosse, l’eventuale corrente dovrebbe fluire in Q1 e Q2 e ciò è impossibile

per quanto visto prima. Di conseguenza non vi sarà corrente in assenza di segnale cioè:

IQ = 0

(12.24)

e quindi, in assenza di segnale, non sarà dissipata potenza.

Dall’analisi delle due maglie ingresso-uscita, comprendenti una Q1 ed una Q2, si ottengono le (12.25) e (12.26) :

v I = −v EB1 + v O

v I = v BE 2 + vO

(12.25)

(12.26)

Dalla (12.26), sostituendo l’espressione di v BE 2 e trascurando la corrente di base si ottiene la (12.27). Analogamente,

per le componenti negative del segnale si ottiene la (12.28); queste due ultime espressioni danno luogo alla

transcaratteristica illustrata in fig. 12.10.

XII - 7

Stadi di uscita

vO

v I = VT ln

VCC-|vCE SAT|-vBE2

vO RL

+ vO

I ES 2

vO > 0

(12.27)

VEE+vCE SAT -0.7

0.7

vI

VCC-|vCE SAT|

vO RL

v I = −VT ln

+ v O

I ES1

VEE+vCE SAT+vEB1

Fig. 12.10

vO < 0

(12.28)

Transcaratteristica del PUSH-PULL (versione bipolare)

Dalle (12.27) e (12.28) si vede che bastano piccole tensioni per avere grandi correnti in uscita e questo perché

v O R L è l’argomento del logaritmo; allora si capisce che questo stadio può essere adatto a pilotare anche resistenze molto

piccole.

Finora sono stati elencati alcuni pregi del "classe B", ma si vede, dalla fig. 12.10, che tali pregi si pagano in termini di

forte non linearità: oltre al tratto non lineare, dovuto alla legge di tipo logaritmico, c’è la cosiddetta “zona morta” che si

estende all’incirca per − 0.7V < v I < 0.7V , in cui si ha v O ≅ 0 , e che dà luogo alla distorsione di cross-over

(attraversamento). E’ quindi evidente la differenza col "classe A" che invece, per piccole v I , attraversava la propria zona

più lineare. Può sembrare che un tale stadio sia inutilizzabile, bisogna però considerare che esso costituirà, in genere,

l’uscita di un amplificatore retroazionato: di conseguenza la distorsione subirà un’attenuazione pari al guadagno d’anello

che, se sufficientemente elevato, può far sì che essa rientri in valori accettabili.

12.3.2 Efficienza di conversione

Se si indica con iC1 e iC 2 il valore medio delle correnti rispettivamente su Q1 e Q2, le potenze fornite dalle

alimentazioni saranno date dalle (12.29) e (12.30):

PCC = VCC iC 2

(12.29)

PEE = V EE iC1

(12.30)

Essendo poi VCC = V EE e iC1 = iC 2 , la potenza totale fornita dalle alimentazioni sarà:

PS = 2 VCC i C 2

(12.31)

Rimane da calcolare il valore medio della corrente su Q2. Si sa però che la conduzione avviene ogni semiperiodo (fig.

12.11), allora iC 2 sarà data dalla (12.32).

iC1

ωτ

− iˆO

iC2

iˆO

π/2

Fig. 12.11

π

3π/2

Angoli di conduzione di Q1 e Q2.

XII - 8

2π

ωτ

Stadi di uscita

T

iC 2 =

1

1

iC 2 (t )dt =

T ∫0

T

T 2

∫ iˆ

O

sen(ωt )dt

(12.32)

0

Risolvendo l’integrale si ottiene, infine:

iC 2 =

1ˆ

iO

π

(12.33)

Sostituendo la (12.33) nella (12.31), si arriva all’espressione:

PS =

2

VCC iˆO

π

(12.34)

La potenza ceduta al carico è data da:

PL =

(12.35)

1 ˆ

vˆ O iO

2

L’efficienza dello stadio in classe B si ottiene dividendo la (12.35) per la (12.34):

ηc =

π v̂ O

4 VCC

(12.36)

Nel caso ideale, in cui l’ampiezza della tensione d’uscita eguagli la VCC , si ha un’efficienza pari a:

ηc =

π

≅ 0,78 = 78%

4

(12.37)

A rigore però:

ηc =

π VCC − v BE max − vCEsat π VCC − 1

≅

4

VCC

4 VCC

(12.38)

che è inferiore a quello dato dalla (12.37), valgono comunque le considerazioni fatte in precedenza per gli stadi in classe A.

12.3.3 Pilotaggio

Una volta definito lo stadio d’uscita è molto importante scegliere l’opportuno circuito di pilotaggio: da esso, infatti,

dipenderanno le prestazioni generali dell’intero stadio finale.

Per lo stadio in classe B, si possono considerare fondamentalmente due topologie per la realizzazione di un circuito di

pilotaggio e sono mostrate in fig. 12.12 (ad emettitore comune) e in fig.12.13 (a collettore comune).

Nonostante nei due casi vi sia lo stesso stadio finale, le prestazioni dei due circuiti sono molto diverse tra loro. Una

prima differenza sta nel fatto che nel primo circuito c’è un guadagno, mentre nel secondo no perché in ingresso c’è un

inseguitore; in fase di progettazione quindi si tiene conto di questo guadagno addizionale andando a richiedere allo stadio

precedente un guadagno minore. Col secondo circuito si hanno però vantaggi in termini di risposta in frequenza essendo il

collettore comune più “veloce” dell’emettitore comune. La differenza sostanziale tra i due circuiti sta però nella massima

tensione sviluppabile.

Per il circuito ad emettitore comune (fig. 12.12) si ha:

v O max = VCC − v BE max − v CEsat

(12.39)

dovendo garantire una v BE max per Q2 e una v CEsat per Q4.

XII - 9

Stadi di uscita

Per quello a collettore comune (fig. 12.13):

v O max = VCC − 2v BE max − v CEsat

(12.40)

perché si deve lasciare una v BE max per Q4 e una v CEsat (nella migliore delle ipotesi) per uno stadio precedente a questo.

VCC

VB

Q4

VCC

vI

Q2

Q4

Q2

vO

Q3

vI

Q1

vO

VB

RL

VEE

Fig. 12.12

Circuito di pilotaggio ad emettitore comune

Q3

Q1

RL

VEE

Fig. 12.13

Circuito di pilotaggio a collettore comune

La prima soluzione ha quindi il netto vantaggio di avere una dinamica maggiore verso l’alto; verso il basso, infatti, i

due circuiti limitano allo stesso modo:

v Omn = V EE + v EB max + v CEsat

(12.41)

Essendo i segnali simmetrici è preferibile, ai fini della dinamica, soltanto la seconda soluzione, considerando anche il

fatto che, con tensioni basse, perdere una v BE potrebbe significare perdere anche il 25% della dinamica disponibile.

Un altro parametro da valutare è la massima corrente che può essere ceduta al carico. Si sottolinea che non è sempre

vero che la massima corrente può essere ceduta dallo stadio che può raggiungere la massima tensione; non si ha che fare

con generatori ideali quindi bisogna valutare volta per volta quali possano essere i fattori limitanti la corrente,

indipendentemente dalle tensioni in gioco. In questi casi, infatti, ci si riferisce alla corrente di cortocircuito ottenuta

ponendo R L = 0 . La corrente sull’emettitore dipende da quella sulla base.

Per il circuito di fig. 12.12, una limitazione

per il massimo positivo è data dalla corrente su Q4 che è fissata dallo specchio: al limite quando tutta la corrente fornita da

Q4 va nella base di Q2, Q3 si spegne e si raggiunge il massimo valore (positivo) per iO . Ciò è indicato nella (12.42).

iO max + = β F 2 I C 3, 4

(12.42)

Per quanto riguarda il massimo valore negativo, invece, non c’è un limite, o meglio, si può dire che vi è solo un limite

di natura fisica del transistore Q3: sarà esso infatti a dover fornire la corrente richiesta in uscita.

Si può considerare

quindi:

iO max − = β F 2 β F 3 I B 3 max

(12.43)

Per il circuito di fig. 12.13 si ha una situazione analoga ma invertita; il limite superiore è:

iO max + = β F 2 β F 4 I B 4 max

(12.44)

mentre quello inferiore:

(12.42)

iO max − = β F 2 I C 3, 4

Può essere fatta ancora una considerazione: si è visto che nel circuito di fig. 12.12 il limite di corrente riguarda il

valore positivo. Il progetto però è fatto cercando di mantenere un equilibrio: Q2, infatti, è un NPN e come tale ha un β F

maggiore di quello di Q3 che, pur avendo a disposizione una corrente negativa assai meno limitata, ha un β F minore.

XII - 10

Stadi di uscita

Analogo discorso si fa per il circuito di fig. 12.13 che, per quanto detto, deve essere migliorato in quanto così com’è

comporta una limitazione in corrente proprio al PNP: basta sostituire allo stadio pilota NPN uno stadio equivalente PNP,

come mostrato in fig. 12.14.

VCC

VB

Q4

Q2

vO

vI

Q3

Q1

RL

VEE

Fig. 12.14

Circuito di pilotaggio PNP a collettore comune per un finale in classe B

Si vuole infine far notare che, in fase di progetto, si deve tener conto del fatto che il valore di β F non è costante con

la densità di corrente, e che esiste un range ottimale di valori di essa per i quali β F si mantiene pressoché costante e pari al

proprio massimo valore. Sarà quindi compito del progettista far sì che il transistore lavori in tali regioni di funzionamento,

scalando opportunamente le aree d’emettitore secondo il valore delle correnti in gioco.

12.3.4 Realizzazione in tecnologia CMOS

Uno stadio analogo a quello di fig. 12.9 si può realizzare con transistori MOS, come mostrato nella fig. 12.15, per il

quale si possono rifare le stesse considerazioni già fatte per il bipolare. Essendo:

v GS 2 + v GS 2 = 0

(12.43)

se iO = 0 allora i D1 = i D 2 = 0 ; anche adesso c’è il grosso vantaggio di una corrente di polarizzazione nulla.

VDD

M1

vI

vO

M2

RL

VSS

Fig. 12.15

Circuito per un finale in classe B

La transcaratteristica si può ottenere, al solito, analizzando i due percorsi ingresso-uscita e sostituendo le espressioni

delle v GS 2 e v SG1 nelle (12.44) e (12.45).

(12.44)

v I = v GS 2 + v O

v I = v SG1 + v O

(12.45)

XII - 11

Stadi di uscita

vO

v I = VT +

VDD-|vDS SAT|-vGS2 MAX

VSS+vDS SAT

vO > 0

(12.46)

VTp

VTn

vI

VDD-|vDS SAT|

VSS+vDS SAT+|vGS1 MAX|

Fig. 12.16

vO R L

+ vO

W

Kn

L 2

v I = −VT +

vO R L

+ vO

W

Kp

L 1

vO < 0

(12.47)

Transcaratteristica del PUSH-PULL (versione CMOS)

Anche ora si ha una caratteristica non lineare; le considerazioni che si possono fare riguardano essenzialmente il

legame di tipo “radice quadrata” nelle (12.46) e (12.47) della v I con la vO , e il fatto che l’escursione del segnale è limitata

da una vGS max che può essere anche molto differente rispetto alla vGS .

La iO max però non è più legata alla corrente in

ingresso, visto che il MOS non assorbe corrente, bensì alla tensione presente sul gate: più alta sarà la v I , maggiore corrente

si avrà in uscita. Come conseguenza si preferisce pilotare questo stadio con un source-comune, che garantirà un’adeguata

escursione di segnale all’ingresso. Ci si preoccuperà quindi soltanto di dimensionare questo stadio per ottenere la dinamica

più alta possibile. Si vuole ora vedere su cosa agire per ottenere in uscita la corrente desiderata. A tal proposito basta

osservare la fig. 12.15 e, ad esempio, il transistore M2. Si supponga di fissare il valore desiderato di iO max ; esso si otterrà

quando tutta la corrente su M2 andrà al carico:

i D 2 = k n (W L )2 (vGS 2 max − VTn ) = iO max

2

(12.46)

La vGS max 2 è nota:

vGS 2 max = V DD − v DSsat − vO max = V DD − v DSsat − R L iO max

(12.47)

Sostituendo la (12.47) nella (12.46), si ricava il valore adeguato di (W L )2 :

iO max

W

=

2

L 2 k n (V DD − v DSsat − R L iO max − VTn )

(12.48)

Si può rifare lo stesso procedimento per il transistore M1, si trova infine la relazione:

k n (W L )2 = k p (W L )1

(12.49)

La differenza sostanziale col BJT è che adesso si gioca sui valori del rapporto (W L ) per ottenere la corrente

desiderata, e non più sul valore della corrente di base.

12.4 Stadio in classe AB

12.4.1 Realizzazione in tecnologia bipolare

Uno stadio in classe AB, in tecnologia bipolare, è rappresentato in fig. 12.17. Questo stadio offre un compromesso tra

le prestazioni del “classe A” e quelle del “classe B”, conciliando l’alta linearità del primo con l’elevata efficienza del

secondo. Si riesce difatti ad ottenere una linearità anche maggiore di quella dello stadio in classe A (a parità di correnti),

che si paga però con una certa dissipazione in continua e quindi con una minore efficienza rispetto al “classe B”.

Da una prima analisi del circuito si può notare che, rispetto al semplice stadio in classe B, sono stati interposti i due

transistori Q3 e Q4; sostanzialmente si tratta di una topologia di tipo “inseguitore”, con Q3 e Q4 connessi a diodo.

XII - 12

Stadi di uscita

Se si trascurano le correnti sulle basi di Q1 e Q2 (a rigore ciò è possibile solo con piccole correnti sul carico), si ha che

quelle in Q3 e in Q4 saranno uguali, costanti e pari ad I B .

VCC

IB

Q4

Q2

vI

vO

Q3

Q1

RL

IB

VEE

Fig. 12.17

Circuito per un finale in classe AB

L’equazione alla maglia interna fornisce:

v EB1 + v BE 2 = v EB 3 + v BE 4

(12.50)

con i termini a secondo membro pressoché costanti, per quanto detto sopra.

Un problema che ci si potrebbe porre è quello del controllo della corrente di polarizzazione nel ramo d’uscita, la I Q ,

dato che essa definisce gran parte delle caratteristiche del circuito. Non ci si preoccupava di ciò nella classe A, visto che era

fissata semplicemente, e neppure nella classe B, dove invece risultava nulla; adesso, non essendone immediata la

determinazione, si tratta di vedere in che modo la si possa legare ai parametri di progetto del circuito stesso.

Dalla (12.50), spostando al primo membro i termini relativi ai transistori PNP e al secondo quelli relativi agli NPN:

v EB1 − v EB 3 = v BE 4 − v BE 2

(12.51)

Sostituendo le espressioni delle v BE :

VT ln

iC1 AE 3

i A

= VT ln C 4 E 2

iC 3 AE1

iC 2 AE 4

(12.52)

Eguagliando gli argomenti e sostituendo I B ad iC 3 e ad iC 4 , si ottiene:

iC1 AE 3 I B AE 2

=

I B AE1 iC 2 AE 4

(12.53)

da cui:

i C1i C 2 =

AE1 AE 2 2

IB

AE 3 AE 4

(12.54)

Se si fissano le aree d’emettitore in maniera tale che:

AE1 AE 2

=

=n

AE 3 AE 4

(12.55)

XII - 13

Stadi di uscita

si ha:

iC1iC 2 = (nI B )

2

(12.56)

La (12.56) mostra che il prodotto delle due correnti su Q1 e Q2 sarà costante e pari a (nI B )2 . In condizioni di

polarizzazione, quando cioè si può supporre iC1 = iC 2 = I Q , la (12.56) diventa:

I Q = nI B

(12.57)

Mentre la (12.56) dà informazioni sulle iC , la (12.57) mostra la dipendenza della I Q dalla I B e fa vedere che tale

corrente, sotto le condizioni dettate dalla (12.55), è controllata mediante il rapporto d’aree dello pseudo-specchio

costituito da Q3 e Q4. Fintanto che i segnali applicati hanno piccole escursioni, è possibile fare un’analisi di piccolo segnale

secondo il modello semplificato di fig. 12.18.

1/gm4

Q2

vo

vi

1/gm3

ri

Q1

ro

RL

Modello equivalente per piccolo segnale del circuito di fig. 12.17

Fig. 12.18

Dall’analisi del circuito si scopre che, per piccoli segnali, l’amplificatore in classe AB si comporta da inseguitore, con

resistenze d’ingresso e d’uscita approssimativamente pari a:

ri =

rπ 1, 2

+

2

1

ro =

g m1, 2

β1 + β 2

RL

2

(12.58)

(12.59)

Al crescere del segnale, e quindi delle correnti, dovendo valere la (12.56), uno dei due transistori andrà a spegnersi;

se, ad esempio, accade che iC 2 >> iC1 , vorrà dire che iC1 → 0 e che, quindi, Q1 si spegnerà.

Nel momento in cui lavorerà un solo transistore, si ritornerà al funzionamento tipico del “classe B”, con una

caratteristica ingresso-uscita di tipo logaritmico:

v I = v O + v BE 2 − v BE 4

(12.60)

che, sostituendo l’espressione di v BE 2 diventa:

v I = v O + VT ln

vO R L

− v BE 4 pol

I ES 2

(12.61)

dove a v BE 4 è stato sostituito v BE 4 pol per il fatto che la corrente su Q4 si può, con buona approssimazione, ritenere costante

e pari al valore di polarizzazione. Le considerazioni fatte sono espresse graficamente nella fig. 12.19.

XII - 14

Stadi di uscita

vO

~VCC-|vCE SAT|-vBE2

ßF2IB2RL

VEE+vCE SAT+vEB3

VCC-|vCE SAT|-vBE4

vI

ßF1IB1RL

VEE+vCE SAT+vEB1

Fig. 12.19

Transcaratteristica del finale in classe AB (versione bipolare)

Dalla fig. 12.19 si nota essenzialmente la differenza con lo stadio in classe B, nel quale per piccoli segnali si andava

incontro alla distorsione di cross-over dovuta alla presenza della zona morta: adesso, al contrario, per piccoli segnali il

finale lavorerà con la massima linearità, grazie al fatto che entrambi i transistori sono attivi.

Questo miglioramento rispetto alla classe B si paga in termini di maggiore complessità (ma in fondo non è un grosso

problema), e soprattutto di riduzione dell’efficienza (si passa dal massimo teorico del 78% dello stadio in classe B al 50%

per il classe AB) a causa di una dissipazione in continua.

Anche adesso la massima corrente erogabile in uscita dipenderà, per come sono fatte le cose, dalla I B , come si può

vedere da una rapida analisi del circuito. Si capisce quindi che la massima tensione in uscita sarà limitata dal valore di tale

corrente nel caso in cui la R L sia sufficientemente bassa (fig. 12.19).Per migliorare questo stadio si può sostituire un

generatore di corrente costante con un emettitore comune (fig. 12.20).

VCC

VCC

IB1

IB1

Q4

Q4

Q1

Q1

vO

Q3

Q2

vO

Q3

RL

vI

RL

vI

Q5

Q5

VEE

Fig. 12.20

Q2

VEE

Classe AB migliorato con emettitore comune NPN

Fig. 12.21

Classe AB migliorato con collettore comune PNP

Verso il basso provvede Q5 a fornire corrente, in questo modo Q2, che è un PNP, non ha limiti di corrente, mentre Q1

rimane limitato dalla polarizzazione. Si poteva mettere un emettitore comune PNP verso l’alto ma sarebbe stato

avvantaggiato Q1 piuttosto che Q2. Una soluzione analoga a questa si può ottenere con un collettore comune (fig. 12.21), si

ripetono le considerazioni fatte.

XII - 15

Stadi di uscita

12.4.2 Realizzazione in tecnologia CMOS

Lo stadio AB si può realizzare secondo il circuito di fig. 12.22. Dall’analisi per piccolo segnale si scopre che, anche

ora, l’uscita insegue l’ingresso; per segnale più ampio vi è una dipendenza di tipo “radice quadrata”. La transcaratteristica

è tracciata nella fig. 12.23.

VDD

vO

IB1

VDD-|vDS SAT|-vGS2 MAX

M4

M1

vI

vO

M3

M2

VSS+vDS

VDD-|vDS SAT|-vGS4

vI

RL

VSS+vDS SAT+vGS1

IB2

VSS

Fig. 12.22

Circuito per un finale in classe AB

Fig. 12.23

Transcaratteristica del finale in classe AB

Stavolta le correnti su M3 ed M4 sono rigorosamente costanti dato che non vi è corrente sui gate di M1 e M2; ciò

comporta per piccolo e grande segnale:

v SG1 + v GS 2 = costante

(12.62)

La corrente massima non è più legata alla corrente di polarizzazione, ma alla massima v GS che si riesce a sviluppare,

quindi come nel “classe B”. Ripercorrendo gli stessi passi segnati dalle (12.46), (12.47) e (12.48) ci si calcola il rapporto

(W L ) sulla base della massima corrente desiderata in uscita. Si può dimostrare che

I Q = nI B

(12.63)

dove:

W

n=

L 2

W W

=

L 4 L 1

W

L 3

(12.57)

In realtà gli stadi in classe AB non vengono realizzati in questo modo perché, da uno studio della dinamica si scopre

che essi, così come sono implementati, sono inutilizzabili a basse tensioni. Valendo infatti la (12.47), si vede subito che, ad

esempio, con una tensione di alimentazione pari a ± 1.5V , se si vogliono sviluppare almeno ± 0.5V sull’uscita, bisogna

lavorare con una v GS 2 max = 0.3V che è addirittura minore della tensione soglia!

Si va allora verso altre soluzioni ancora in fase di studio, che permettono di avere le caratteristiche suddette di

dinamica con le tensioni considerate. La difficoltà di progettazione di questi stadi a bassa tensione sta nel controllo della

corrente di uscita.

12.5 Protezione dai cortocircuiti

Negli stadi di uscita, soprattutto in quelli degli amplificatori operazionali di uso generale, si trovano i circuiti di

protezione dai cortocircuiti. Il problema dei cortocircuiti si pone quando la corrente può essere non limitata (ad es. a quella

di polarizzazione) per motivi di progetto.

XII - 16

Stadi di uscita

In tal caso è necessaria una circuiteria di contorno all’amplificatore finale vero e proprio al fine di evitare che, in caso

di cortocircuito accidentale, i transistori stessi possano finire coll’erogare troppa corrente, rovinandosi in maniera

irreversibile. Un tipico circuito di protezione è mostrato nella figura seguente:

VCC

Q6

VB

Q4

Q2

Q8

vI

RX2

RX1

RX2

RX1

vO

RL

Q7

VA

Q3

Q1

Q5

VEE

Fig. 12.18

Circuito di protezione dai cortocircuiti

Quello nella fig. 12.18 è uno stadio in classe AB senza limitazioni in corrente. Le resistenze R X sono piccole in modo

da non disturbare il funzionamento del circuito (ad es. 25Ω ), e stanno tra loro nel rapporto R X 2 = (I Q I B ) ⋅ R X 1 per far sì

che analizzando la maglia le cadute si semplifichino. Sotto queste ipotesi, se Q7 è spento vale la (12.56).

Se la corrente supera un certo limite fissato, la caduta sulle R X 1 è tale da polarizzare Q7 (o Q8) che entra in

conduzione e blocca la corrente su Q1 (o Q2). Le resistenze R X verranno dimensionate per la corrente di intervento.

12.6 Conclusioni

Gli amplificatori con stadio di uscita non vengono quasi mai usati nei circuiti integrati, la loro presenza deve essere

giustificata da esigenze ben precise. Normalmente infatti i carichi presenti all’interno dei circuiti integrati sono molto

grandi per cui l’esigenza di erogare potenza nasce solo nel momento in cui ci si interfaccia verso l’esterno.

Gli stadi di uscita sono da evitare perché degradano le prestazioni in termini di risposta in frequenza, dissipazione,

distorsione, area di silicio occupata.

In genere in un circuito integrato si realizzano uno o al più due stadi di uscita.

XII - 17