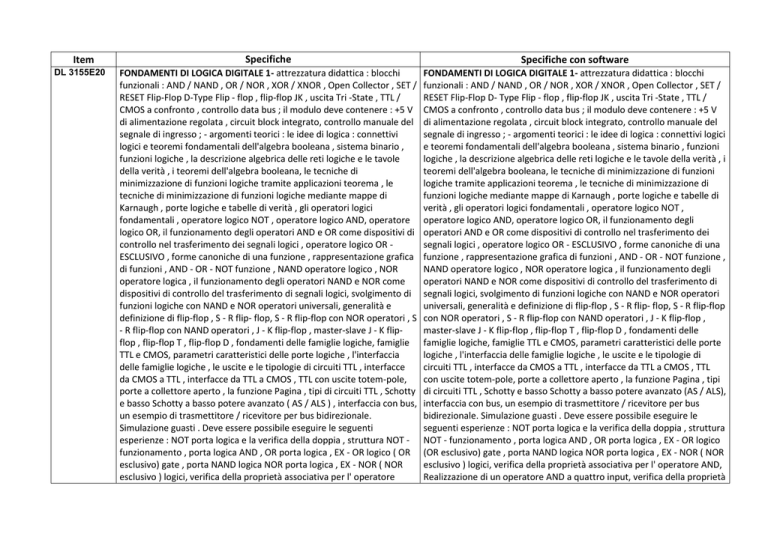

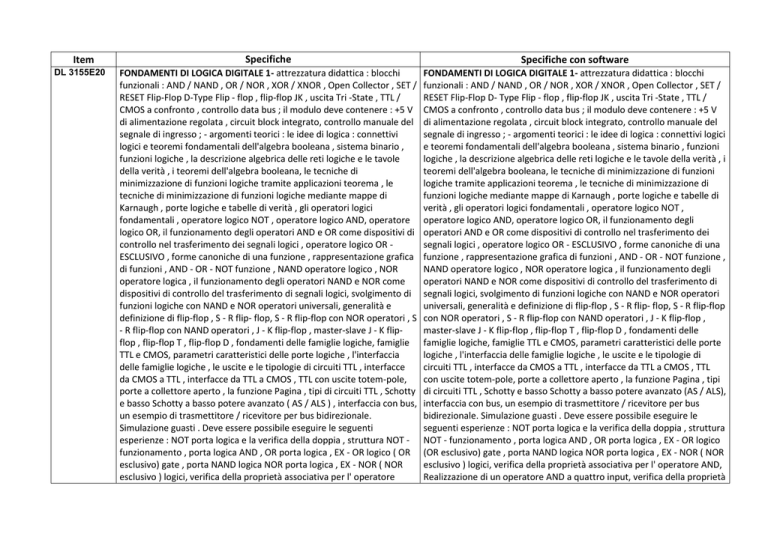

Item

DL 3155E20

Specifiche

Specifiche con software

FONDAMENTI DI LOGICA DIGITALE 1- attrezzatura didattica : blocchi

funzionali : AND / NAND , OR / NOR , XOR / XNOR , Open Collector , SET /

RESET Flip-Flop D-Type Flip - flop , flip-flop JK , uscita Tri -State , TTL /

CMOS a confronto , controllo data bus ; il modulo deve contenere : +5 V

di alimentazione regolata , circuit block integrato, controllo manuale del

segnale di ingresso ; - argomenti teorici : le idee di logica : connettivi

logici e teoremi fondamentali dell'algebra booleana , sistema binario ,

funzioni logiche , la descrizione algebrica delle reti logiche e le tavole

della verità , i teoremi dell'algebra booleana, le tecniche di

minimizzazione di funzioni logiche tramite applicazioni teorema , le

tecniche di minimizzazione di funzioni logiche mediante mappe di

Karnaugh , porte logiche e tabelle di verità , gli operatori logici

fondamentali , operatore logico NOT , operatore logico AND, operatore

logico OR, il funzionamento degli operatori AND e OR come dispositivi di

controllo nel trasferimento dei segnali logici , operatore logico OR ESCLUSIVO , forme canoniche di una funzione , rappresentazione grafica

di funzioni , AND - OR - NOT funzione , NAND operatore logico , NOR

operatore logica , il funzionamento degli operatori NAND e NOR come

dispositivi di controllo del trasferimento di segnali logici, svolgimento di

funzioni logiche con NAND e NOR operatori universali, generalità e

definizione di flip-flop , S - R flip- flop, S - R flip-flop con NOR operatori , S

- R flip-flop con NAND operatori , J - K flip-flop , master-slave J - K flipflop , flip-flop T , flip-flop D , fondamenti delle famiglie logiche, famiglie

TTL e CMOS, parametri caratteristici delle porte logiche , l'interfaccia

delle famiglie logiche , le uscite e le tipologie di circuiti TTL , interfacce

da CMOS a TTL , interfacce da TTL a CMOS , TTL con uscite totem-pole,

porte a collettore aperto , la funzione Pagina , tipi di circuiti TTL , Schotty

e basso Schotty a basso potere avanzato ( AS / ALS ) , interfaccia con bus,

un esempio di trasmettitore / ricevitore per bus bidirezionale.

Simulazione guasti . Deve essere possibile eseguire le seguenti

esperienze : NOT porta logica e la verifica della doppia , struttura NOT funzionamento , porta logica AND , OR porta logica , EX - OR logico ( OR

esclusivo) gate , porta NAND logica NOR porta logica , EX - NOR ( NOR

esclusivo ) logici, verifica della proprietà associativa per l' operatore

FONDAMENTI DI LOGICA DIGITALE 1- attrezzatura didattica : blocchi

funzionali : AND / NAND , OR / NOR , XOR / XNOR , Open Collector , SET /

RESET Flip-Flop D- Type Flip - flop , flip-flop JK , uscita Tri -State , TTL /

CMOS a confronto , controllo data bus ; il modulo deve contenere : +5 V

di alimentazione regolata , circuit block integrato, controllo manuale del

segnale di ingresso ; - argomenti teorici : le idee di logica : connettivi logici

e teoremi fondamentali dell'algebra booleana , sistema binario , funzioni

logiche , la descrizione algebrica delle reti logiche e le tavole della verità , i

teoremi dell'algebra booleana, le tecniche di minimizzazione di funzioni

logiche tramite applicazioni teorema , le tecniche di minimizzazione di

funzioni logiche mediante mappe di Karnaugh , porte logiche e tabelle di

verità , gli operatori logici fondamentali , operatore logico NOT ,

operatore logico AND, operatore logico OR, il funzionamento degli

operatori AND e OR come dispositivi di controllo nel trasferimento dei

segnali logici , operatore logico OR - ESCLUSIVO , forme canoniche di una

funzione , rappresentazione grafica di funzioni , AND - OR - NOT funzione ,

NAND operatore logico , NOR operatore logica , il funzionamento degli

operatori NAND e NOR come dispositivi di controllo del trasferimento di

segnali logici, svolgimento di funzioni logiche con NAND e NOR operatori

universali, generalità e definizione di flip-flop , S - R flip- flop, S - R flip-flop

con NOR operatori , S - R flip-flop con NAND operatori , J - K flip-flop ,

master-slave J - K flip-flop , flip-flop T , flip-flop D , fondamenti delle

famiglie logiche, famiglie TTL e CMOS, parametri caratteristici delle porte

logiche , l'interfaccia delle famiglie logiche , le uscite e le tipologie di

circuiti TTL , interfacce da CMOS a TTL , interfacce da TTL a CMOS , TTL

con uscite totem-pole, porte a collettore aperto , la funzione Pagina , tipi

di circuiti TTL , Schotty e basso Schotty a basso potere avanzato (AS / ALS),

interfaccia con bus, un esempio di trasmettitore / ricevitore per bus

bidirezionale. Simulazione guasti . Deve essere possibile eseguire le

seguenti esperienze : NOT porta logica e la verifica della doppia , struttura

NOT - funzionamento , porta logica AND , OR porta logica , EX - OR logico

(OR esclusivo) gate , porta NAND logica NOR porta logica , EX - NOR ( NOR

esclusivo ) logici, verifica della proprietà associativa per l' operatore AND,

Realizzazione di un operatore AND a quattro input, verifica della proprietà

AND, Realizzazione di un operatore AND a quattro input, verifica della

proprietà associativa per l'operatore OR , verifica dei teoremi

dell'algebra booleana : teoremi di una variabile, Teoremi tra una

variabile ed una costante, Teoremi di assorbimento , il teorema di De

Morgan , la verifica funzionale della forma canonica della EX- OR

operatore , verifica funzionale della prima forma canonica di una

funzione assegnata attraverso la sua tavola delle verità , la verifica

funzionale di un circuito logico attraverso il confronto con la t.t. della sua

logica di funzionamento , la verifica funzionale della minimizzazione

delle funzioni logiche attraverso le mappe del Karnaugh , il controllo di

una lampada con controllo circuito logico combinatorio , selezione

automatica di eventi, flip - flop , la verifica del funzionamento logico di

un flip-flop SR , verifica dell'operazione logica di un master-Slave JK flipflop , la verifica del funzionamento logico di un flip flop D , la verifica del

funzionamento logico di un flop T rovescio, le caratteristiche elettriche

di porte logiche TTL , interfaccia tra porte logiche , sistemi BUS.

I guasti devono essere inseriti da microinterruttori montati sulla scheda ,

il modulo deve essere provvisto di una interfaccia EISA BUS 31 +18 di,

collegamenti e punti di test tramite terminali di due millimetri.

Dimensioni del modulo : 297x260mm .

Il modulo deve esser fornito con un manuale teorico e pratico.

associativa per l'operatore OR , verifica dei teoremi dell'algebra booleana

: teoremi di una variabile, Teoremi tra una variabile ed una costante,

Teoremi di assorbimento , il teorema di De Morgan , la verifica funzionale

della forma canonica della EX- OR operatore , verifica funzionale della

prima forma canonica di una funzione assegnata attraverso la sua tavola

delle verità , la verifica funzionale di un circuito logico attraverso il

confronto con la t.t. della sua logica di funzionamento , la verifica

funzionale della minimizzazione delle funzioni logiche attraverso le mappe

del Karnaugh , il controllo di una lampada con controllo circuito logico

combinatorio , selezione automatica di eventi, flip - flop , la verifica del

funzionamento logico di un flip-flop SR , verifica dell'operazione logica di

un master-Slave JK flip-flop , la verifica del funzionamento logico di un flip

flop D , la verifica del funzionamento logico di un flop T rovescio, le

caratteristiche elettriche di porte logiche TTL , interfaccia tra porte

logiche, sistemi BUS.

I guasti devono essere inseriti tramite software e tramite i

microinterruttori montati sulla scheda. Il modulo deve essere provvisto di

una interfaccia EISA BUS 31 +18 per il collegamento all’alimentazione e al

PC, con un software in grado di consentire lo studio di argomenti teorici

da PC con navigazione ipertestuale secondo lo standard HTML.

Collegamenti e punti di test tramite terminali di 2 mm.

Dimensioni del modulo : 297x260mm.

Il modulo deve essere fornito con un manuale teorico e pratico.