Programma definitivo di Elettronica generale

Classe 3B A.S. 2011-12

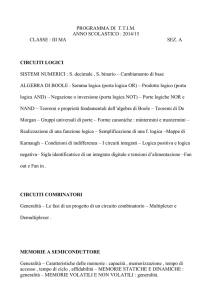

Codici e sistemi di numerazione

a) Sistemi di numerazione:

-Sistemi di numerazione a base 10, base 2, base 8, base 16, in base qualsiasi.

-Conversione da un numero in base 10 a un numero in base qualsiasi

b) Codici binari:

- Concetto di codice.

- Principali codici utilizzati nei sistemi digitali: Binario, Decimale, Gray.

c) Aritmetica binaria:

- Principali forme di rappresentazione di numeri con segno.

-Operazioni aritmetiche tra numeri binari.

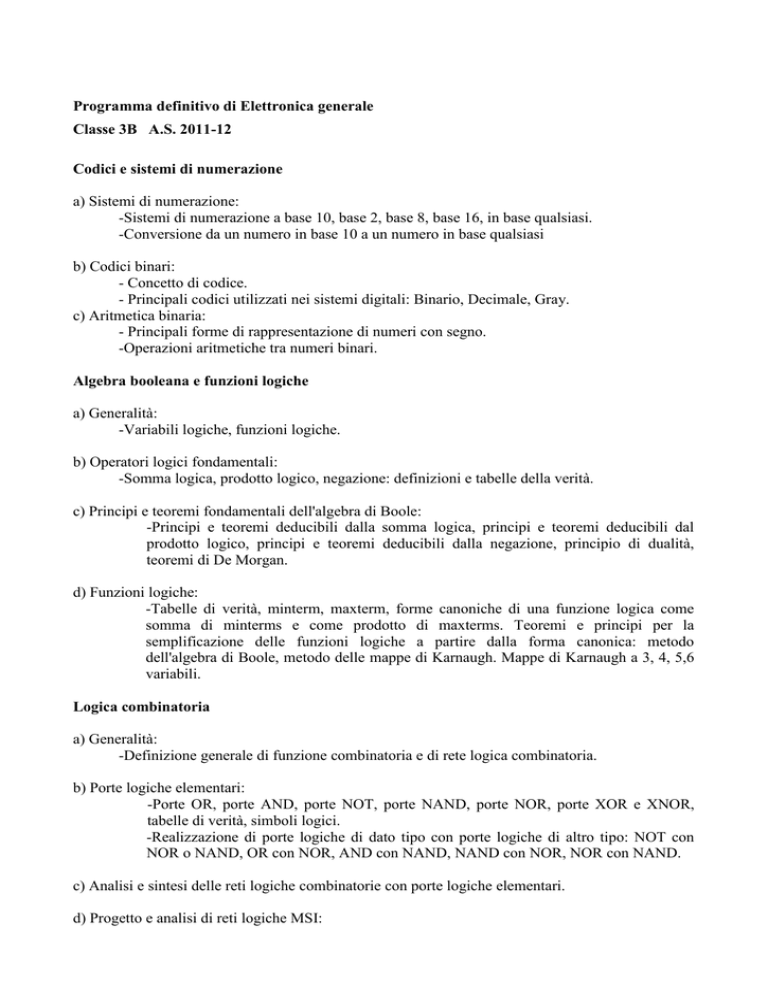

Algebra booleana e funzioni logiche

a) Generalità:

-Variabili logiche, funzioni logiche.

b) Operatori logici fondamentali:

-Somma logica, prodotto logico, negazione: definizioni e tabelle della verità.

c) Principi e teoremi fondamentali dell'algebra di Boole:

-Principi e teoremi deducibili dalla somma logica, principi e teoremi deducibili dal

prodotto logico, principi e teoremi deducibili dalla negazione, principio di dualità,

teoremi di De Morgan.

d) Funzioni logiche:

-Tabelle di verità, minterm, maxterm, forme canoniche di una funzione logica come

somma di minterms e come prodotto di maxterms. Teoremi e principi per la

semplificazione delle funzioni logiche a partire dalla forma canonica: metodo

dell'algebra di Boole, metodo delle mappe di Karnaugh. Mappe di Karnaugh a 3, 4, 5,6

variabili.

Logica combinatoria

a) Generalità:

-Definizione generale di funzione combinatoria e di rete logica combinatoria.

b) Porte logiche elementari:

-Porte OR, porte AND, porte NOT, porte NAND, porte NOR, porte XOR e XNOR,

tabelle di verità, simboli logici.

-Realizzazione di porte logiche di dato tipo con porte logiche di altro tipo: NOT con

NOR o NAND, OR con NOR, AND con NAND, NAND con NOR, NOR con NAND.

c) Analisi e sintesi delle reti logiche combinatorie con porte logiche elementari.

d) Progetto e analisi di reti logiche MSI:

-Decoder ed encoder, progetto e caratteristiche generali, componenti integrati.

-Espansione dei decoder.

-Half adder, Full adder, Half subtractor, Full subtractor, progetto e caratteristiche generali.

-Comparatore tra due numeri di 4 bit, progetto e caratteristiche generali, comparatori

integrati.

-Transcodifica da BCD a 7 segmenti, binario 7 segmenti per display ad anodo e a catodo

comune.

-Multiplexer e demultiplexer, progetto, caratteristiche generali, integrati, espansioni.

-Applicazione del multiplexer nel progetto delle reti con una sola uscita.

-Progetto di reti logiche che effettuano operazioni aritmetiche.

Logica sequenziale

a) Generalità:

-Caratteristica generale di una rete logica sequenziale, modello generale di una rete

logica sequenziale.

b) FLIP FLOP:

-FF asincroni: NOR e NAND latch.

-FF sincroni: segnale di sincronismo, FF tipo D; FF tipo T; FF tipo SR; FF tipo JK.

-FF master slave.

Attività di laboratorio

Il programma è stato integrato con specifiche esercitazioni di laboratorio, con particolare attenzione

alla verifica del funzionamento dei principali componenti via via introdotti nel corso della teoria

quali: verifica e applicazione dei componenti SSI (AND, OR, NOT, NOR, NAND, XOR,) XNOR,

verifica del funzionamento di decoder, multiplexer, encoder, comparatori.

Simulazione dei circuiti con Logic Works 5.

Display a 7 segmenti: decodifica e verifica sperimentale.

Parte delle ore di laboratorio è stata dedicata all'apprendimento di elementi del linguaggio VHDL e

del programma di simulazione e sintesi di reti logiche (ambiente di sviluppo Galaxy di Cypress).

Particolare attenzione è stata dedicata ai circuiti a logica programmabile come elementi su cui

sintetizzare reti logiche descritte con VHDL.

Gli insegnanti:

Turchi Rosalea

Cavalli Giovanni

I rappresentanti degli studenti: