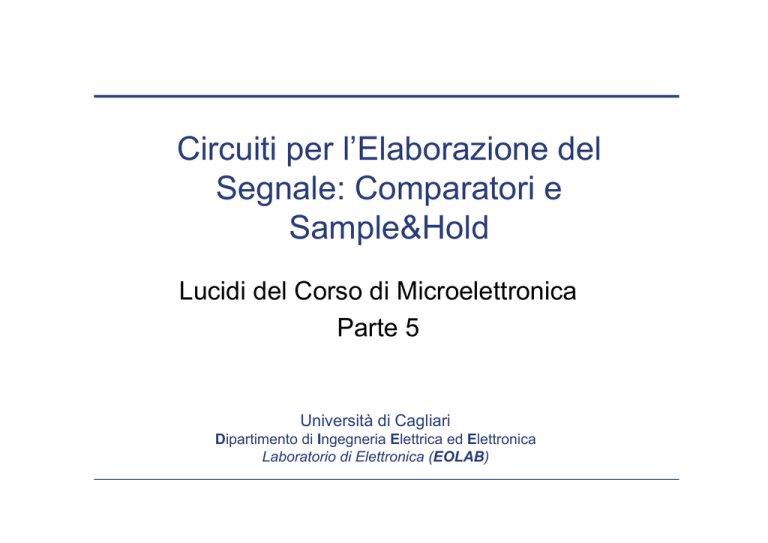

Circuiti per l’Elaborazione

l Elaborazione del

Segnale: Comparatori e

Sample&Hold

Lucidi del Corso di Microelettronica

Parte 5

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

Comparatori

Un comparatore è un dispositivo che confronta un segnale di ingresso (in

tensione) con una soglia dando in uscita un segnale binario che indica se l’

ingresso è maggiore o minore della soglia.

L’implementazione

p

più semplice

p

p

è

data

dall’uso

di

un

amplificatore ad anello aperto.

Se in segnale di ingresso supera

i

limiti

di

linearità

dell’amplificatore l’uscita satura

al valore positivo o negativo.

Problemi:

•La risoluzione del segnale

g

in ingresso

g

è limitata dalla tensione di offset

(segnali in ingresso più piccoli di Vos non possono essere distinti

correttamente perché la Vos non è nota a priori)

•Il tempo di comparazione è limitato dalla banda limitata dell

dell’amplificatore

amplificatore

17 Aprile 2007

UE - Comparatori e S&H

Massimo Barbaro

2

Comparatori: Eliminazione Offset

Una soluzione alternativa prevede l’uso di una capacità (C) per campionare il

valore della Vos (tensione di offset) sottrarla poi al segnale da comparare.

Il funzionamento

f

i

t è diviso

di i in

i due

d fasi:

f i

F1: L’ingresso è scollegato, l’amplificatore è connesso ad inseguitore, la

capacità

p

C è p

posta fra il nodo di uscita e massa; il valore di Vos viene

campionato ai capi di C.

F2: L’amplificatore è posto ad anello aperto, l’ingresso è applicato al bottom

plate della capacità,

capacità siccome la capacità ha ancora memorizzato il valore di

Vos, sull’altro terminale (collegato al morsetto invertente) comparirà Vin+Vos. Il

confronto avviene quindi fra Vin+Vos e Vos ed è quindi indipendente dal valore

di Vos.

Vos

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

3

Comparatori: Velocità

La velocità della comparazione dipende dalla banda dell’amplificatore e dal

suo guadagno.

d

Esempio: un segnale di ampiezza 0.5mV deve essere confrontato con lo

zero. Se la tensione di uscita dell’amplificatore ha un’escursione di 5V e la

frequenza a guadagno unitario dell’opamp è 10MHz qual è la massima

frequenza di confronto?

Se ll’uscita

uscita ha un range di 5V il segnale di 0.5mV

0 5mV deve essere amplificato

10000 volte per avere il massimo range di uscita. In tali condizioni (ricordando

che ωP 1 ≈ ωt / A0) la frequenza a 3dB risulta f-3dB=1kHz, quindi il tempo di

risposta del sistema del primo ordine equivalente risulta ττ=1/(2π

1/(2π f-3dB

0.16ms

3dB))=0.16ms

Richiedendo almeno 6τ perché l’uscita si stabilizzi e supponendo che la fase

(F1) di reset duri quanto quella di confronto si ottiene una frequenza di

comparazione

i

di solili 500Hz

500H

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

4

Comparatori: Velocità

Per aumentare le prestazioni in termini di velocità si può pensare di non

compensare

p

l’amplificatore

p

solo nella fase ((F2)) in cui funziona da

comparatore e quindi è nella configurazione ad anello aperto (in F1

l’amplificatore è in retroazione con guadagno unitario e quindi non può non

essere compensato).

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

5

Comparatore: Iniezione di Carica

Lo schema di comparazione con cancellazione dell’offset è affetto da problemi

legati

g alla p

presenza degli

g switch ed al fenomeno noto come iniezione di carica.

Il funzionamento è infatti basato sulla memorizzazione sulla capacità C della

tensione Vos che è immagazzinata sotto forma di carica.

La presenza di capacitè parassite ed il fatto che lo switch sia costituito da un

transistor acceso fanno sì che in corrispondenza dei fronti di clock si verifichino

due fenomeni parassiti che alterano la carica immagazzinata su C e quindi

modificano il valore della tensione di offset campionata rendendo in questo modo

impreciso il suo valore e peggiorando quindi la risoluzione del comparatore.

I fenomeni che danno luogo all’iniezione di carica sono fondamentalmente due:

•Redistribuzione della carica: quando gli switch si spengono la carica che era

immagazzinata nel canale viene iniettata per metà nel drain e per metà nel

source

•Clock feedthrough: la presenza di capacità parassite genera un accoppiamento

indesiderato fra i terminali di drain e source ed il gate dove è applicato il segnale

di clock,

clock la cui variazione può trasmettersi ai nodi critici.

critici

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

6

Redistribuzione della Carica

Il fenomeno di redistribuzione della carica si verifica quando un MOS usato come

interruttore si spegne.

Quando il MOS è acceso, infatti, il canale è formato ed è quindi presente una

carica (negativa nel caso del NMOS perché formata da elettroni) pari a:

QCH= - WLCOXVeff= - WLCOX(VGS-V

V t)

Quando il MOS si spegne il canale (e quindi la carica associata) deve scomparire;

se il segnale di clock che causa lo spegnimento è sufficientemente veloce la

carica si divide equamente e fluisce per metà attraverso il drain e per metà

attraverso il source.

Se uno dei

S

d i due

d

t

terminali

i li è connesso ad

d un nodo

d critico

iti

ad

d alta

lt impedenza

i

d

l

la

carica iniettata non può scorrere verso l’alimentazione ma rimane immagazzinata

nella capacità associata nel nodo provocando una variazione nel suo potenziale.

∆V=(QCH/2)/C= - [WLCOX(VGS-Vt)]/(2C)

P minimizzare

Per

i i i

l’l’effetto

ff tt bi

bisogna minimizzare

i i i

WL

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

7

Clock Feedthrough

L’effetto di clock feedthrough è legato al fatto che quando il MOS si spegne il

suo potenziale di gate (a cui è applicato il clock) subisce una brusca variazione

di tensione (da Vdd a Vss).

Vss)

Poiché fra il gate ed il drain (o il source) esiste una capacità parassita Cov, tale

variazione si riporta sul drain per accoppiamento capacitivo.

Vg

Cov

La variazione di tensione di drain dovuta alla

capacità

p

di overlap

p Cov dipende

p

dalla variazione di

tensione di gate.

Vd

C

Le due capacità in serie si comportano da partitore

capacitivo.

∆Vd = ∆Vg Cov/(C+Cov)=

= (Vss-Vdd)

(V Vdd) Cov/(C+C

/(C Cov)

Per minimizzare l’effetto è necessario ridurre il rapporto Cov/C

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

8

Comparatori: Iniezione di Carica

Nel caso del nostro circuito le capacità parassite coinvolte sono:

Il clock che determina la prima fase (F1) viene diviso in due parti

leggermente sfasate (F1a va a zero leggermente prima di F1) in modo da

ridurre

id

glili effetti

ff tti di iniezione

i i i

di carica

i aii quelli

lli introdotti

i t d tti dal

d l solo

l Q3.

Q3

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

9

Comparatori: Iniezione di Carica

Se F1a è il clock che va a zero per prima la carica iniettata da Q3 nel suo

source sono critici.

critici La carica che va in Vout infatti viene tranquillamente

assorbita dai transistor di uscita dell’opamp, ma la carica iniettata nel source

viene immagazzinata nella capacità C perché il nodo V’’ è un nodo ad alta

impedenza

p

((da notare che q

quando F1a si apre

p F1 è ancora alto q

quindi l’altro

terminale di C è ancora a massa).

Contributo di redistribuzione di carica:

∆V’’ = - [(Vdd-Vt)COXW3L3]/(2C)

Contributo del Clockfeedthrough:

∆V’’ = (Vss-Vdd)Cov/(Cov +C)

L’effetto finale è dato dalla combinazione dei due (in genere il primo

contributo domina sul secondo). Questo errore sulla tensione al nodo V’’ si

traduce in un errore sulla Vos campionata e quindi sulla risoluzione del

comparatore.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

10

Iniezione di Carica

Perché sfasare F1a rispetto a F1 rende ininfluenti i contributi di iniezione di

carica di Q1 e Q2?

Nel caso di Q1 la cosa è evidente: quando Q1 si spegne la comparazione è

stata già fatta quindi la carica che esso introduce in V

V’ non comporta errore di

comparazione.

Nel caso di Q2 invece il ragionamento è il seguente: se quando Q2 si apre Q3

risulta

i lt già

ià aperto

t la

l carica

i iniettata

i i tt t da

d Q2 in

i V’ non può

ò portare

t

a variazione

i i

di

potenziale sulla capacità C perché questa comporterebbe una variazione di

carica anche su V’’ che è isolato (Q3 è appunto già chiuso e il terminale di

ingresso invertente dell

dell’opamp

opamp è evidentemente un circuito aperto).

aperto) La cosa

chiaramente non funzionerebbe se Q3 si aprisse contemporaneamente o

addirittura dopo Q2.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

11

Riduzione dell’Iniezione di Carica

Gli effetti dell’iniezione di carica possono essere notevolmente ridotti

ricorrendo a topologie fully-differential. In tal caso le cariche iniettate da Q3a e

Q3b si compensano (anche se non perfettamente) poiché danno luogo ad

errori di modo comune che vengono poi cancellati dall’amplificatore fullydifferential.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

12

Comparatori: Multistadio

Oltre all’approccio fully-differential si possono migliorare le prestazioni di un

comparatore usando l’approccio multistadio, ossia utilizzando più amplificatori in

cascata.

cascata

Le fasi F1, F1’, F1’’ e F1’’’ sono organizzate in modo che il primo segnale a

spegnersi sia F1’ seguito da F1’’, F1’’’ e solo per ultimo da F1.

In questo modo la carica iniettata in C1 non produce errore perché OA2 è ancora

connesso ad inseguitore, analogamente la carica iniettata in C2 non produce errore

perché OA3 è connesso ad inseguitore e solo la carica iniettata in C3 da F1’’’

contribuirà a ridurre la risoluzione del comparatore.

comparatore Tale carica,

carica però,

però per essere

confrontata con l’ingresso deve passare attraverso i guadagni A1 e A2 e quindi

risulta molto più piccola.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

13

Comparatori Multistadio

Il problema di un comparatore multistadio è la velocità, essendoci N amplificatori

in cascata bisognerà tenere conto della banda limitata degli N amplificatori.

amplificatori

Si può dimostrare comunque che, a parità di risoluzione (quindi a parità di

guadagno totale) un comparatore multistadio risulta più veloce del suo

equivalente

i l t a singolo

i

l stadio

t di (che

( h dovrebbe

d

bb avere un guadagno

d

parii a A0N dove

d

N

è il numero di stadi e A0 il guadagno del singolo stadio).

Infatti il ritardo del multistadio cresce linearmente con N ((numero di stadi)) mentre

nel caso del singolo stadio il ritardo cresce esponenzialmente con N.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

14

Comparatori: Track and Latch

Per avere comparatori molto veloci è necessario ricorrere ad architetture

differenti e rinunciare all’uso di un amplificatore con elevato guadagno.

Il p

preamplificatore

ea p cato e in ingresso

g esso ha

a guadag

guadagno

o molto

o to ridotto

dotto ((fra

a 4 e 10)

0) in modo

odo da

non limitarne la banda. La comparazione viene fatta dal circuito successivo

(track and latch) che sfrutta una retroazione positiva per aumentare la velocità.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

15

Comparatori: Track and Latch

Quando Vltch è basso il pull-down nmos ed il pull-up pmos sono disconnessi e

l uscite

le

it sono precaricate

i t a 0 (in

(i modo

d che

h non cii sia

i memoria

i tra

t una

comparazione e l’altra). Nel frattempo il preamplificatore amplifica la differenza

di potenziale in ingresso e sbilancia i gate degli nmos del track&latch.

Quando poi Vltch va alto nmos e pmos vengono connessi dando luogo ad una

configurazione che vede due inverter ad anello (il latch) più due transistor che

sbilanciano le uscite del latch di quel tanto che basta ad innescarne la

retroazione positiva e quindi la memorizzazione di uno dei due stati stabili. Lo

stato stabile di arrivo dipende ovviamente dalla differenza di potenziale in

ingresso.

Il ritardo col quale il latch commuta dipende fondamentalmente solo da

parametri di processo e quindi è una costante di una data tecnologia.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

16

Sample & Hold

Un sample&hold è un circuito in grado di campionare (sample) una tensione e

mantenerla

t

l costante

t t (hold)

(h ld) per un determinato

d t

i t periodo

i d di tempo.

t

V

Vengono

tipicamente utilizzati come circuiti di ingresso dei convertitori A/D. La tensione

dovrà essere memorizzata per il tempo necessario ad effettuare la

conversione.

conversione

L’implementazione più

semplice

li

di un sample

l

& hold è data da una

capacità

connessa

all’ingresso

ll’i

per mezzo

di uno switch ed alla

uscita per mezzo di un

buffer di tensione.

tensione

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

17

Sample&Hold: Prestazioni

Le prestazioni di un S&H sono determinate da:

Hold Step: L

L’errore

errore introdotto nel valore campionato a causa del passagio

dallo stato di sample a quello di hold. Tale errore dovrebbe essere

indipendente dal segnale in modo da introdurre un errore sistematico e NON

una

u

ad

distorsione.

so so e

Isolamento: la misura dell’isolamento fra il valore campionato e la variazione

dell’ingresso (in hold mode).

Velocità: la velocità con cui il sample&hold riesce a seguire le variazioni

dell’ingresso nel sample mode.

Droop rate: la rapidità con cui il segnale campionato decade in hold mode,

mode

causato dalle correnti di leakage.

Aperture Jitter: l’errore nell’istante di campionamento.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

18

Sample&Hold: Errori

Le imprecisioni di funzionamento del più semplice sample&hold sono legate

agli

g stessi p

problemi che si p

presentano nei comparatori

p

per via degli

p

g switch.

Lo switch Q1, nell’aprirsi, causa

un’iniezione

un

iniezione di carica nel nodo V

V’

modificando

la

tensione

campionata.

Le componenti di errore sono

due, dovute al clock feedthrough

ed alla redistribuzione di carica.

Contributo di redistribuzione di carica:

∆V’ = - [(Vdd-Vt-Vin)COXWL]/(2Chld)

Contributo del clockfeedthrough:

∆V’ = [(Vss-Vdd)COV]/Chld

Il primo effetto è più grave sia perché maggiore sia perché dipende dal

segnale (attraverso Vin e Vt) ed introduce quindi una distorsione.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

19

S&H: Riduzione Iniezione di Carica

Per ridurre gli effetti di iniezione di carica si può utilizzare un transfer gate,

quindi sostituire lo switch con una coppia di transistor (pmos e nmos) pilotati

da segnali opposti. In tal modo mentre il pmos immagazzina carica positiva e

lo nmos immagazzina carica negativa ed i loro effetti si dovrebbero annullare.

In realtà non è quasi

mai possibile riuscire

ad

d

annullare

ll

esattamente la carica

del pmos e del nmos

(dipendono dalla Veff e

quindi dal segnale di

ingresso) quindi questa

configurazione porta a

miglioramenti ma non

ad annullare l’effetto.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

20

S&H: Riduzione Iniezione di Carica

Un meccanismo migliorare consiste nell

nell’annullare

annullare la carica iniettata per

mezzo di un secondo switch Q2 che è sempre cortocircuitato ma si accende

quando Q1 si spegne. Se Q2 è grande la metà di Q1 dovrebbe riuscire ad

intercettare nel suo canale la carica iniettata da Q1 allo spegnimento.

spegnimento

Anche in questo caso la

cancellazione non è perfetta

(

(soprattutto

tt tt se il clock

l k non

ha fronti sufficientemente

ripidi) ma è comunque più

efficace (non dipende dal

segnale). I due clock devono

comunque

essere

leggermente sfasati per

garantire che la carica di Q2

non sfugga attraverso Q1.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

21

Sample&Hold: Sampling Jitter

Se il segnale di clock ha dei fronti non verticali si verifica il fenomeno di

incertezza (jitter) dell’istante di campionamento. L’istante esatto del

campionamento viene cioè a dipendere dal segnale.

segnale Lo switch infatti si

spegne quando il clock è inferiore al segnale di una soglia, quindi il

campionamento avviene prima o dopo dell’istante ideal.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

22

Sample&Hold: Miglioramenti (1)

Le prestazioni del circuito elementare possono essere migliorate complicando la

topologia circuitale. In questo caso si introduce un opamp nell’anello di

retroazione aumentando ll’impedenza

impedenza di ingresso del S&H. Questa

configurazione permette anche di ridurre l’offset del buffer, dividendolo per il

guadagno dell’opamp (l’offset dell’opamp non viene però cancellato). L’unica

controindicazione è data dall’aumento del tempo

p di risposta

p

dovuta alla

necessità di garantire la stabilità in configurazione ad anello chiuso. Inoltre,

quando l’opamp è ad anello aperto (hold mode) la sua uscita tende a saturare e

ciò introduce un ritardo nella capacità di seguire l’ingresso passando al sample

mode.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

23

Sample&Hold: Miglioramenti (2)

Per risolvere i problemi del circuito precedente si può adottare questa

topologia In questo modo in hold mode ll’opamp

topologia.

opamp non satura ma viene

connesso ad inseguitore e quindi sarà più pronto nel seguire l’ingresso

tornando in sample mode.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

24

Sample&Hold: Miglioramenti (3)

Per migliorare ulteriormente le prestazioni si utilizza questa configurazione. Il

capacitore di hold non è connesso a massa ma in controreazione su un

opamp. In sample mode (Fclk alto) l’uscita è uguale all’ingresso (su un

terminale di Chld c’è la massa virtuale). In hold mode Chld rimane carica.

L’iniezione

L

iniezione di carica dovuta a Q1 diventa indipendente dal segnale perché sul

suo drain è presente la massa virtuale. Inoltre l’uscita di OpAmp1, in hold

mode, è tenuta da Q2 al potenziale di massa che sarà quello da assumere in

sample

p mode.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

25

Sample&Hold: Miglioramenti (4)

Questa topologia è simile alla precedente, ne conserva i vantaggi, con in più

la presenza di C

C’hld che riduce ll’hold

hold step dovuto all

all’apertura

apertura di Q1 grazie

all’iniezione di una carica identica, tramite Q2, sul terminale non invertente di

OpAmp2. Questo riduce l’offset sistematico introdotto da Q1. Le

controindicazioni di questi due ultimi circuiti sono legate alla necessità di

garantire la stabilità ad anello chiuso di due opamp in cascata.

29 Aprile 2006

UE - Comparatori e S&H

Massimo Barbaro

26