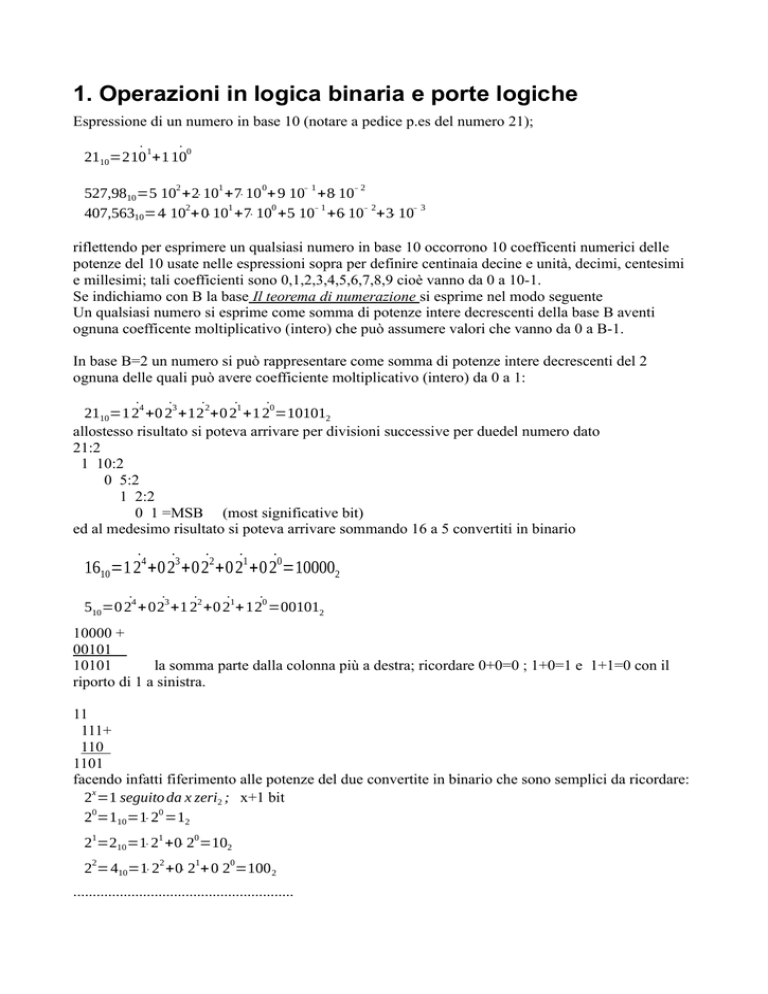

1. Operazioni in logica binaria e porte logiche

Espressione di un numero in base 10 (notare a pedice p.es del numero 21);

˙0

2110=2 10˙ 1+1 10

527,9810=5⋅ 102 +2⋅ 101 +7⋅ 10 0+ 9⋅ 10− 1 +8⋅ 10− 2

407,56310=4⋅ 102+ 0⋅ 101 +7⋅ 100 +5⋅ 10− 1 +6⋅ 10− 2+3⋅ 10− 3

riflettendo per esprimere un qualsiasi numero in base 10 occorrono 10 coefficenti numerici delle

potenze del 10 usate nelle espressioni sopra per definire centinaia decine e unità, decimi, centesimi

e millesimi; tali coefficienti sono 0,1,2,3,4,5,6,7,8,9 cioè vanno da 0 a 10-1.

Se indichiamo con B la base Il teorema di numerazione si esprime nel modo seguente

Un qualsiasi numero si esprime come somma di potenze intere decrescenti della base B aventi

ognuna coefficente moltiplicativo (intero) che può assumere valori che vanno da 0 a B-1.

In base B=2 un numero si può rappresentare come somma di potenze intere decrescenti del 2

ognuna delle quali può avere coefficiente moltiplicativo (intero) da 0 a 1:

2110=1 2̇4 +0 2̇3 +1 2˙2+0 2˙1 +1 2̇0=101012

allostesso risultato si poteva arrivare per divisioni successive per duedel numero dato

21:2

1 10:2

0 5:2

1 2:2

0 1 =MSB (most significative bit)

ed al medesimo risultato si poteva arrivare sommando 16 a 5 convertiti in binario

1610=1 2̇4 +0 2̇3 +0 2̇2 +0 2̇1 +0 2̇0=100002

510=0 2˙4 + 0 2˙3 +1 2̇2 +0 2̇1+1 2˙0 =001012

10000 +

00101

10101

la somma parte dalla colonna più a destra; ricordare 0+0=0 ; 1+0=1 e 1+1=0 con il

riporto di 1 a sinistra.

11

111+

110

1101

facendo infatti fiferimento alle potenze del due convertite in binario che sono semplici da ricordare:

x

2 =1 seguito da x zeri2 ; x+1 bit

20=110=1⋅ 20 =12

2 =210=1⋅ 2 +0⋅ 2 =102

1

1

0

22=410=1⋅ 22 +0⋅ 21+ 0⋅ 20=100 2

.........................................................

25=3210=1⋅ 25 +0⋅ 24 +0⋅ 23+ 0⋅ 22 +0⋅ 21 +0⋅ 20=1000002

(6 bit)

......................................................................................

210=100.0000 .00002=1 K

(11 bit)

e fondamentali per stabilire immediatamente il numero di bit necessari per effettuare una codifica

per esempio quella degli alunni di una classe: per es N=29

per poter codificare ciscuno è come assegnare ad ugnuno un numero, e in sostanza come riuscire a

contare da 0 a 28 che osservando le potenze del 2 sopra espresse si riesce a fare con 5 bit. Se invece

si considerasse una classe di 37 elementi la codifica siriesce a fare utilzzando 6 bit e lasciando

inutilizzati tutti numeri dal 37 fino al 63 compresi.

2n °bit − 1≥ n°elementi dellacodifica;

In generale

(ovviamente n°bit il più piccolo possibile).

n°bit è il numero di bit necessari per effettuare la codifica;

n° elementi della codifica sono per es glialunni da numerare.

Se per esempio il numero degli alunni da codificare è 16 (basterà saper contare da 0 a 15) e si

utilizzeranno 4 bit infatti

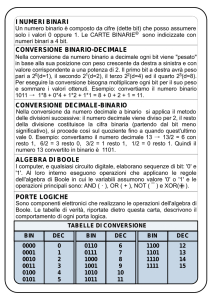

dec bin ESA

0 0000 0

1 0001 1

2 0010 2

3 0011 3

4 0100 4

5 0101 5

6 0110 6

7 0111 7

8 1000 8

9 1001 9

10 1010 A

11 1011 B

12 1100 C

13 1101 D

14 1110 E

15 1111 F

per convertire in base 16 esadecimale un numero binario p.es. 1011.0111.1110.0001 una parola

"word" di 16 bit si scompone a gruppi di 4 bit partendo dal LSB (bit meno significativo) e se ne

legge la codifica esadecimale riportata in tabella cosi il codice binario diventa B7E1 in base 16

il byte 1010.1111 diventa AF in base 16.

Le operazioni in logica binaria sono dette Booleane e sono la somma logica (OR) e il prodotto

logico (AND) Queste operazioni sono definite attraverso la cosiddetta tabella di verità. Le tabelle di

verità della porta AND e OR sono le seguenti

A

B

AND

U

A

B

U(AND)

0

0

0

1

0

0

0

1

0

1

1

1

A

B

U(OR)

0

0

0

1

0

1

0

1

1

1

1

1

Per ottenere l'espressione e l'operazione logica rappresentata da una certa tabella di verità si applica

il teorema di De Morgan riguardante la prima espressione canonica detta somma di prodotti, oppure

la seconda espressione canonica detta prodotti di somme.

Per quanto riguarda la prima espressione canonica si selezionano le righe in cui l'uscita è pari a 1

(nel caso della Tab porta AND solo l'ultima riga), si fa il prodotto degli ingressi (nel ns caso A e B)

mettendo A se nella riga considerata A=1 e mettendo Ā se nella riga considerata A=0 e poi si

sommano fra loro i prodotti di tutte le righe (vedi calcolo porta OR);

risulta per la porta AND la prima espressione canonica

A⋅ B

(Espressione algebrica porta AND detto prodotto logico)

Per la porta OR la prima espressione canonica risulta

A⋅ B+ A⋅ B+ A⋅ B

difficile da semplificare; in quest caso meglio utilizzare la seconda forma dell'espressione canonica

detta prodotti di somme: si selezionano le righe in cui l'uscita è pari a 0

(nel caso della Tab porta OR solo la prima riga), si fa la somma degli ingressi (nel ns caso A e B)

mettendo A se nella riga considerata A=0 e mettendo Ā se nella riga considerata A=1 e poi si fa il

prodotto delle somme di ogni riga; per la porta OR la seconda forma della espressione canonica è

A + B (Espressione algebrica porta OR detta somma logica)

Porta XOR

A⋅ B+ A⋅ B= A . XOR . B

A

B

U(XOR)

0

0

0

1

0

1

0

1

1

1

1

0

Porta NOT

Ᾱ

A

A

U(NOT)

0

1

1

0

Vi sono poi le porte NAND, NOR e XNOR o EXNOR che sono le porte che danno uscita negata N

rispetto alle porte AND, OR e XOR il loro schema è il seguente:

esercizio 1.

In una classe sono contenuti 16 studenti realizzare un circuito digitale con porte logiche che faccia

accendere un led (suonare uno speaker ecc...) da 1.2 Volt e 10 mA di corrente nominale quando due

studenti sono fuori posto.

Si osserva che lo studio riguarda sia la realizzazione del circuito elettrico riguardante l'accensione

del led in questo caso è il circuito attuatore, sia del circuito elettronico combinatorio di porte

logiche senza elementi di memoria in cui l'uscita al rempo t dipende solo sallo stato degli ingressi al

tempo t, sia del circuito trasduttore che è costituito ad esempio da interruttori a bottone monostabili

normalmente aperti (NA) inseriti sulla sedia del banco di ogni studente: quando lo studente è seduto

si schiaccia l'interuttore (è come l'interuttore del campanello) chiudendo il circuito ad esso collegata

.

Si osserva che il sistema in esame è molto simile all'es. Di pag 136 del libro di testo vol 1 e la cui

soluzione è riportata sul sito nella parte delle esercitazioni. Ci sarà bisogno ovviamente di

componentistica con un numero maggiore di ingressi con classi per es di 30 studenti e a cui si

devolve allo studente il compito di identificare i chip o le architetture idonee previste nella vasta

gamma di scelte.

con U1= interuttori monostabili NA ; X1 Encoder (codificatore) decimale-binario; X2 porta NOT;

X5 decoder Decodificatore binario display sette segmenti; X6 Decoder binario decimale.

Per risolvere espressioni di tabelle di verità in molte variabili di ingresso e composte da molti

monomi di semplificare è necessario conoscere il metodo di minimizzazione delle espressioni di

Karnaugh;

Di seguito si riporta la tabella di verità dell'esercizio 1 (uscita 1 quando 2 studenti sono in piedi):

A B C D U

0

0 0 0 0

0

0 0 1 0

0

0 1 0 0

0

0 1 1 1

0

1 0 0 0

0

1 0 1 1

0

1 1 0 1

0

1 1 1 0

1

0 0 0 0

1

0 0 1 1

1

0 1 0 1

1

0 1 1 0

1

1 0 0 1

1

1 0 1 0

1

1 1 0 0

1

1 1 1 0

AB CD+C D( A B+B A)+AB CD + DC ( A B+B A)= ABCD + ABCD +( A B+ B A)(C D+ DC )

che si può scrivere

[(A-AND-B) -XOR- (C-AND-D )]OR[(A-XOR-B)AND(C-XOR-D)

Esercizio 2

Si considerino i numeri da 1 a 15 e si realizzi un circuito che accenda un led con le caratteristiche

dell'es.1 quando il decimale codificato in binario corrisponde ad un numero primo.

d AB CDU

0

0 0 0 0 0

1

0 0 0 1 1

2

0 0 1 0 0

3

0 0 1 1 1

4

0 1 0 0 0

5

0 1 0 1 1

6

0 1 1 0 0

7

0 1 1 1 1

8

1 0 0 0 0

9

1 0 0 1 0

10 1 0 1 0 0

11 1 0 1 1 1

12 1 1 0 0 0

13 1 1 0 1 1

14 1 1 1 0 0

15 1 1 1 1 0

si possono eseguire raggruppamenti di 2,4 ,8,16... celle adiacenti orizzontalmente o verticalmente,

si osserva che le colonne terminali sono da considerarsi adiacenti come se il piano fosse in realtà un

cilindro con asse verticale rispetto al foglio e unito attraverso gli estremi delle colonne iniziale e

finale.

I tre raggruppamenti (uno da 4 elementi e due da 2 elementi )originano la seguente espressione della

tabella di verità proposta nell'es.2

B CD + A D+ B C D= A D+D(B C+C B) che si può scrivere

(NOT A -AND-D) OR [D-AND-(B -XOR-C)]

es-3

Progettare un circuito combinatorio con 8 ingressi numerati da 0 a 7 tale che in uscita si abbia la

codifica binaria corrispondente all'ingresso considerato che viene all'istante alimentato. NB solo un

ingresso per volta.

Disegno dello schema funzionale es 3

Disegno dello schema funzionale es 4

CE (chip Enable)

N0

N1

N2

N3

N4

N5

N6

N7

Codificatore decimale binario

U0

U1

U2

MSB

1

U0

0

U1

0

U2

LSB

CE

N0

.....

.....

.....

N4

.....

.....

N7

Decodificatore Binario Decimale

Esercizio 4

Progettare il circuito che esegua l'operazione opposta rispetto all'esercizio precedente ossia un

sistema combinatorio con tre ingressi che quando corrispondono alla codifica binaria della linea in

uscita corrispondente al numero decimale codificato, attiva tale uscita

Esercizio 5 Multiplexer digitale

Progettare un circuito combinatorio tale da avere 8 ingressi sui quali può essere presente o meno un

segnale 5V o GND (in logica diretta rispettivamente 1 e 0 logico) ed una sola linea di uscita U Il

circuito deve essere tale, mediante delle linee di selezione in codice binario dell'ingresso desiderato

numerato decimale, da collegare tale ingresso con l'uscita(Multiplexer digitale).

Esercizio 6 Demultiplexer digitale

Progettare il circuito che svolge l'operazione inversa ossia 1 solo ingresso e mediante canali di

selezione binari metterlo in collegamento con l'uscita desiderata numerata in decimale

(Demultiplexer Digitale)

Disegno dello schema funzionale es 5

Disegno dello schema funzionale es 6

CE (chip Enable)

N0

N1

N2

N3

N4

N5

N6

N7

MSB S0 S1 S2

1 1 0

CE

N0

.....

U

I

.....

.....

N4

.....

.....

N7

MSB S0 S1 S2

1 0 0