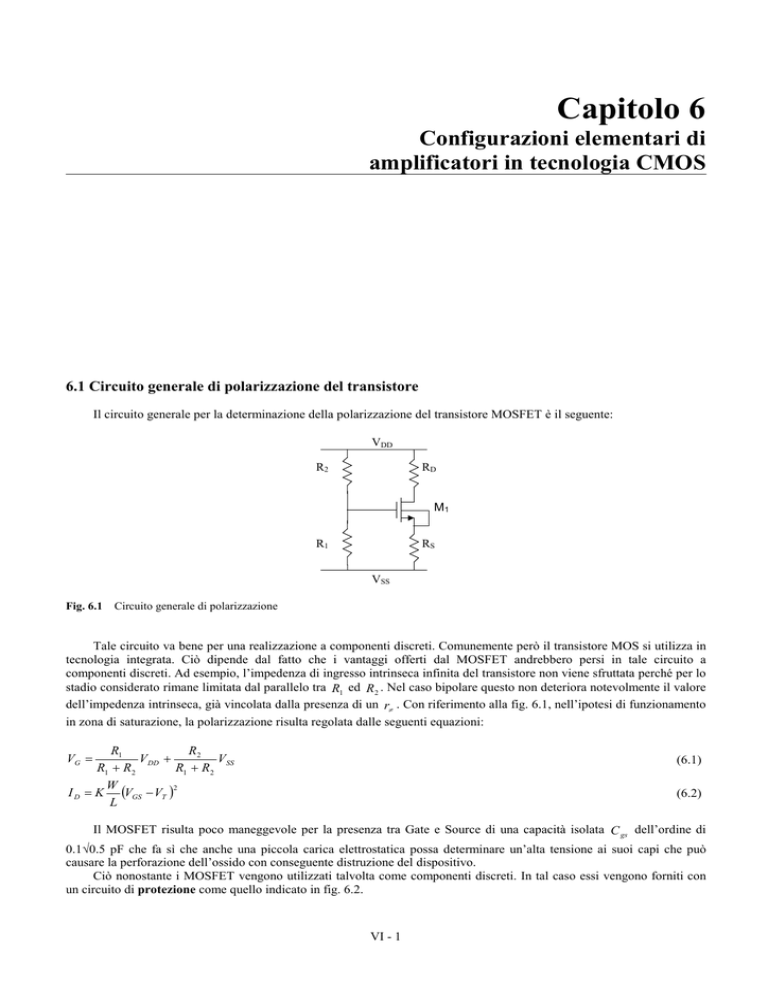

Capitolo 6

Configurazioni elementari di

amplificatori in tecnologia CMOS

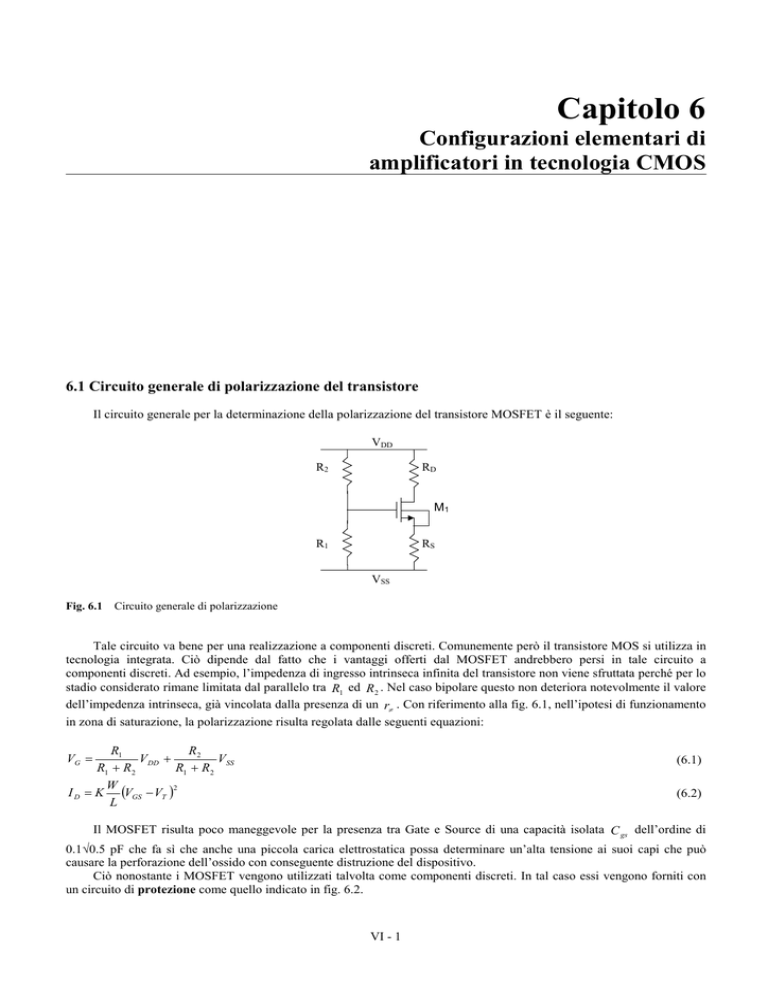

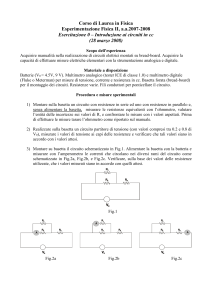

6.1 Circuito generale di polarizzazione del transistore

Il circuito generale per la determinazione della polarizzazione del transistore MOSFET è il seguente:

VDD

R2

RD

M1

R1

RS

VSS

Fig. 6.1

Circuito generale di polarizzazione

Tale circuito va bene per una realizzazione a componenti discreti. Comunemente però il transistore MOS si utilizza in

tecnologia integrata. Ciò dipende dal fatto che i vantaggi offerti dal MOSFET andrebbero persi in tale circuito a

componenti discreti. Ad esempio, l’impedenza di ingresso intrinseca infinita del transistore non viene sfruttata perché per lo

stadio considerato rimane limitata dal parallelo tra R1 ed R2 . Nel caso bipolare questo non deteriora notevolmente il valore

dell’impedenza intrinseca, già vincolata dalla presenza di un rπ . Con riferimento alla fig. 6.1, nell’ipotesi di funzionamento

in zona di saturazione, la polarizzazione risulta regolata dalle seguenti equazioni:

R1

R2

V DD +

V SS

R1 + R2

R1 + R2

W

2

I D = K (VGS − VT )

L

VG =

(6.1)

(6.2)

Il MOSFET risulta poco maneggevole per la presenza tra Gate e Source di una capacità isolata C gs dell’ordine di

0.1÷0.5 pF che fa sì che anche una piccola carica elettrostatica possa determinare un’alta tensione ai suoi capi che può

causare la perforazione dell’ossido con conseguente distruzione del dispositivo.

Ciò nonostante i MOSFET vengono utilizzati talvolta come componenti discreti. In tal caso essi vengono forniti con

un circuito di protezione come quello indicato in fig. 6.2.

VI - 1

Configurazioni elementari di amplificatori in tecnologia CMOS

VDD

VD

D1

VG

M1

D2

VSS

Fig. 6.2

VS

Circuito di protezione per dispositivi MOS

6.2 Configurazione a source comune

Lo schema di un source comune si ottiene dal circuito di fig. 6.1 con l’introduzione delle capacità C G e C S :

VDD

R2

vi

RD

vo

CG

M1

R1

RS

CS

VSS

Fig. 6.3

Amplificatore a source comune

6.2.1 Risposta a bassa frequenza per lo stadio a source comune

Alle basse frequenze il comportamento è influenzato dalla presenza di C G e C S . E’ presente uno zero in continua, a

causa della capacità C G , un altro zero dovuto a C S e due poli. Calcolando le resistenze equivalenti rG ed rS viste

rispettivamente da C G e da C S si scopre che il polo a frequenza più bassa sarà quello dovuto a C G poiché la rG è

notevolmente più grande rispetto alla rS .

rG = R1 || R2

rS = RS ||

(6.3a)

1

1

≅

gm gm

(6.3b)

Il guadagno alla frequenza del primo polo si calcola allora considerando C G già cortocircuitata e C S ancora un

circuito aperto. Si ottiene:

AV =

RD

RS

(6.4)

Per trovare la frequenza dello zero bisogna vedere quando si annulla l’uscita. L’espressione di vo è:

VI - 2

Configurazioni elementari di amplificatori in tecnologia CMOS

vi

ZS

(6.5)

RS

1 + sC S R S

(6.6)

vo = −i d R D = − R D

dove:

Z S = R S || C S =

Imponendo quindi vo = 0 :

vo = −

RD

(1 + sC S RS )vi = 0

RS

(6.7)

si ha:

s=−

1

C S RS

(6.8)

Il guadagno massimo si ottiene appena si cortocircuita anche la C S :

A Max = g m R D

(6.9)

Il segnale v s in ingresso dovrà quindi avere una frequenza minima:

f min =

1 gm

2π C S

(6.10)

La risposta a bassa frequenza di questo stadio è rappresentata in fig. 6.4.

vo

vi

(dB)

g m RS

RD

RS

1

( R1 || R2 )C G

Fig. 6.4

1

RS C S

gm

CS

Risposta a bassa frequenza dello stadio a source comune

6.2.2 Risposta a media frequenza per lo stadio a source comune

VI - 3

log ω

Configurazioni elementari di amplificatori in tecnologia CMOS

Utilizzando il modello per piccolo segnale di fig. 6.5, si calcolano le resistenze d’ingresso, d’uscita e il guadagno:

ri = ∞

(6.11)

ro = rd

(6.12)

AV =

vo

= − g m (R D || rd ) ≅ − g m R D

vi

(6.13)

RD

Vo

vi

M1

ro

ri

Fig. 6.5

Modello equivalente a media frequenza

6.3 Configurazione a drain comune

Lo stadio a drain comune è mostrato in fig. 6.6.

VDD

R2

vi

RD

CG

CD

M1

vo

R1

RS

VSS

Fig. 6.6

Amplificatore a drain comune

6.3.1 Risposta a bassa frequenza per lo stadio a drain comune

Il comportamento a basse frequenze è dovuto alla presenza di C G e C D . In continua è presente uno zero dovuto a C G

che determina anche un polo con la resistenza equivalente rG :

rG = R1 || R2

(6.14)

Il blocco costituito da R D e C D è praticamente ininfluente perché dà un polo ed uno zero che si compensano essendo

a frequenze molto vicine. Il grafico della risposta a bassa frequenza è nella fig. 6.7.

VI - 4

Configurazioni elementari di amplificatori in tecnologia CMOS

vo

(dB)

vi

log ω

1

( R1 || R 2 )C G

Fig. 6.7

Risposta a bassa frequenza dello stadio a drain comune

6.3.2 Risposta a media frequenza per lo stadio a drain comune

Si analizza ora il circuito per piccolo segnale calcolando resistenza d’ingresso, resistenza d’uscita e guadagno tramite

il modello equivalente di fig. 6.8.

vi

M1

Vo

ri

RS

ro

Fig. 6.8

Modello equivalente a media frequenza

Anche adesso è immediato determinare:

ri = ∞

(6.15)

1

1

≅

gm gm

v

g m (R S || rd )

AV = o =

vi 1 + g m ( R S || rd )

ro = R S ||rd ||

(6.16)

(6.17)

6.4 Configurazione a gate comune

VDD

R2

RD

vo

M1

CG

R1

RS

VSS

Fig. 6.9

Amplificatore a gate comune

VI - 5

ii

Configurazioni elementari di amplificatori in tecnologia CMOS

6.4.1 Risposta a media frequenza per lo stadio a gate comune

Le resistenze d’ingresso e d’uscita del circuito di fig. 6.10 sono:

rd + R D

1 + g m rd

ro = rd + R S + g m rd R S ≅ g m rd R S

ri =

(6.18)

(6.19)

Si calcola il guadagno utilizzando il modello equivalente di Norton (fig. 6.11), con la corrente iocc di cortocircuito e la

resistenza equivalente ro , date rispettivamente dalla (6.20) e (6.19):

iocc = i s =

RS

ii

R S + ri

(6.20)

Risulta:

vo

= ro || R D ≅ R D

iocc

(6.21)

e quindi:

vo

RS

= RD

io

RS + ri

(6.22)

RD

Vo

M1

ro

iocc

RS

Fig. 6.10

ro

RS

vo

ri

ii

Modello equivalente a media frequenza

Fig. 6.11

Modello equivalente di Norton per il calcolo del

guadagno

6.5 Amplificatore Cascode

La cascata tra uno stadio a source comune ed uno a gate comune viene utilizzato per ottenere prestazioni simili ad un

source comune ma in un intervallo di frequenze più ampio.

Per la polarizzazione si utilizza una rete a tre resistenze (fig. 6.12); la capacità C G1 ha lo scopo di disaccoppiare in

continua vi dal resto del circuito, mentre C S 1 è una capacità di bypass che pone il source di M1 a massa per piccolo

segnale. Infine C G 2 pone il gate di M2 a massa per piccolo segnale.

La polarizzazione, nell’ipotesi di funzionamento in regione di saturazione, è retta dalle seguenti equazioni:

I S 1 = I D1 = I D 2

(6.23)

VI - 6

Configurazioni elementari di amplificatori in tecnologia CMOS

VGS1 = VT +

VGS 2 = VT +

I D1

W

K

L 1

(6.24)

I D1

W

K

L 2

(6.25)

VG 2 min = V S1 + V DSsat1 + VGS 2

(6.26)

VG 2 max = V D 2 − V DSsat 2 + VGS 2

(6.27)

VDD

R3

RD

vo

CG2

M2

R2

CG1

M1

vi

R1

RS1

CS1

VSS

Fig. 6.12

Amplificatore Cascode

6.5.1 Risposta a media frequenza per l’amplificatore Cascode

Si considera ora il comportamento a centro banda e quindi si calcola il guadagno e le resistenze d’ingresso e d’uscita

tramite il modello semplificato mostrato in fig. 6.13.

RD

vo

M2

ro

rS2

M1

vi

Fig. 6.13

Modello equivalente a media frequenza

VI - 7

Configurazioni elementari di amplificatori in tecnologia CMOS

Le correnti sono:

i d 1 = g m1 vi

(6.28)

rd 1

id 1

rd 1 + rs 2

= is 2

is2 =

(6.29)

id 2

(6.30)

Risulta:

vo = − R D i d 2

(6.31)

quindi:

vo

rd 1

= − g m1

RD

vi

rd 1 + rs 2

(6.32)

dove:

rs 2 =

rd 2 + R D

g m 2 rd 2

(6.33)

Se si fa l’ipotesi che rd 1 >> R D , essendo rs 2 ≅ 1 g m 2 e rd 1 >> 1 g m1 , il guadagno avrà la seguente espressione:

vo

≅ − g m1 R D

io

(6.34)

La resistenza d’ingresso, ovviamente è infinita, quella d’uscita è invece data da:

ro = rd 2 + rd 1 + g m 2 rd 2 rd 1 ≅ g m 2 rd 2 rd 1

(6.35)

6.3 Resistenze d’ingresso e uscita di più transistori in cascata

Nelle figure che seguono sono mostrate le resistenze viste dai terminali di più dispositivi (MOS e BJT) in cascata.

β3rc3=β2rc2

gm3rd3gm2rd1rd2

Q3

M3

M3

β2rc2

gm2rd1rd2

Q2

M2

rd1

rc1

Q1

M1

Fig. 6.14

Resistenze viste dai drain e dai collettori

VI - 8

Configurazioni elementari di amplificatori in tecnologia CMOS

Q3

Q2

Q1

Q1

rc3

Q2

rc2

β2rc2

Q1

1/gm

2/gm1

rπ/2

Fig. 6.15

Resistenze viste dall’emettitore di un base comune

Nel primo caso la resistenza d’ingresso sarà:

re = rπ ||

rc

1

≅

1 + g m rc g m

(6.36)

essendo nulla la RC . Nel secondo caso:

re = rπ ||

rc 2 + rc

2

≅

1 + g m rc g m

(6.37)

essendo RC la resistenza d’uscita di un base comune PNP senza resistenza di emettitore.

Nel terzo caso, infine, la resistenza d’ingresso sarà:

re = rπ ||

βrc + rc

βr

r

≅ rπ || c = π

1 + g m rc

g m rc 2

(6.38)

essendo RC la resistenza d’uscita di due base comune PNP in cascata.

In modo analogo si calcolano le resistenze viste dal source di un gate comune:

M3

M2

M1

M1

rd3

rd2

M2

M1

1/gm

rd2rd3gm2

2/gm1

rd2rd3gm2 rd1gm1

Fig. 6.16

Resistenze viste dal source di un gate comune

6.4 Stadio differenziale

Lo stadio differenziale MOS (fig. 6.17) si presenta in modo del tutto simile a quello del BJT, anche in questo caso si

fa dunque l’ipotesi che la struttura sia perfettamente simmetrica, in particolare che i due transistori M1 ed M2 abbiano gli

stessi fattori di forma, si suppone cioè: (W L )1 = (W L )2 e R D1 = R D 2 .

VI - 9

Configurazioni elementari di amplificatori in tecnologia CMOS

VDD

RD1

RD1

vo1

vi1

vo2

M1

M2

vi2

ISS

VSS

Fig. 6.17 Stadio differenziale MOS

In polarizzazione i gate dei due transistori sono alla stessa tensione VG , che deve essere almeno pari alla tensione di

soglia VT per mantenere M1 ed M2 in saturazione. Dall’equazione alla maglia d’ingresso si ottiene:

VGS1 = VGS 2

(6.39)

Questo comporta che le due correnti di drain sono uguali:

I D1 = I D 2

(6.40)

ed essendo:

I SS = I D1 + I D 2

(6.41)

risulta:

I D1 = I D 2 =

I SS

2

(6.42)

Quindi:

VO1 = VO 2 = V DD − R D

I SS

2

(6.43)

6.4.1 Analisi di piccolo segnale

Sia la resistenza d’ingresso di modo comune che quella di modo differenziale sono infinite in quanto i gates sono

isolati dall’ossido. Si calcola il guadagno di modo differenziale, utilizzando il modello di fig. 6.18. Risulta:

vi1 =

vi

2

vi 2 = −

(6.44a)

vi

2

v o1 = − g m1 (R D1 || rd 1 )

(6.44b)

vi

2

(6.45a)

VI - 10

Configurazioni elementari di amplificatori in tecnologia CMOS

vo 2 = g m 2 (R D 2 || rd 2 )

vi

2

(6.45b)

Essendo:

vo = v o 2 − v o1

(6.46)

si ha:

Ad =

1

(g m1 R D1 + g m 2 R D 2 ) = g m1, 2 RD

2

RD1

M1

RD1

RD2

vo2

vo1

vi /2

(6.47)

M2

vo2

vo1

vi

- vi /2

M1

2RSS

Fig. 6.18

RD2

M2

vi

2RSS

Modello equivalente per il calcolo del guadagno di Fig. 6.19 Modello equivalente per il calcolo del guadagno di modo

modo differenziale

comune

Per il calcolo del guadagno di modo comune si utilizza il modello di fig. 6.19 costituito da due source comune con

resistenza di source 2 R SS , dove RSS è la resistenza equivalente del generatore di corrente. Si può notare come il guadagno

di modo comune sarebbe nullo se la struttura fosse perfettamente simmetrica, difatti si ha:

vi

2 R SS

v

= − RD 2 i

2 RSS

v o1 = − R D1

(6.48a)

vo 2

(6.48b)

Ed essendo:

vo = v o1 − v o 2

(6.49)

si ottiene:

Ac =

R D1 − R D 2

2 RSS

(6.50)

Rimane da calcolare il rapporto tra il guadagno di modo differenziale e quello di modo comune:

CMRR = g m1, 2 RD

2 RSS

RD1 − RD 2

(6.51)

Nel caso ideale questo rapporto avrà valore infinito e lo stadio differenziale amplificherà solo ingressi differenziali.

VI - 11