Esperimentazioni di Fisica 3

AA 2013-2014

“Tracking ADC”

M. De Vincenzi

1

Introduzione

La digitalizzazione di segnali analogici si realizza tramite dispositivi che vengono

detti ADC (acronimo per Analog to Digital Converter). La conversione del

valore analogico di una tensione in un corrispondente valore digitale, si può

ottenere con tecniche differenti, alcune delle quali, sono descritte nel testo di

Millman e Grabel [1].

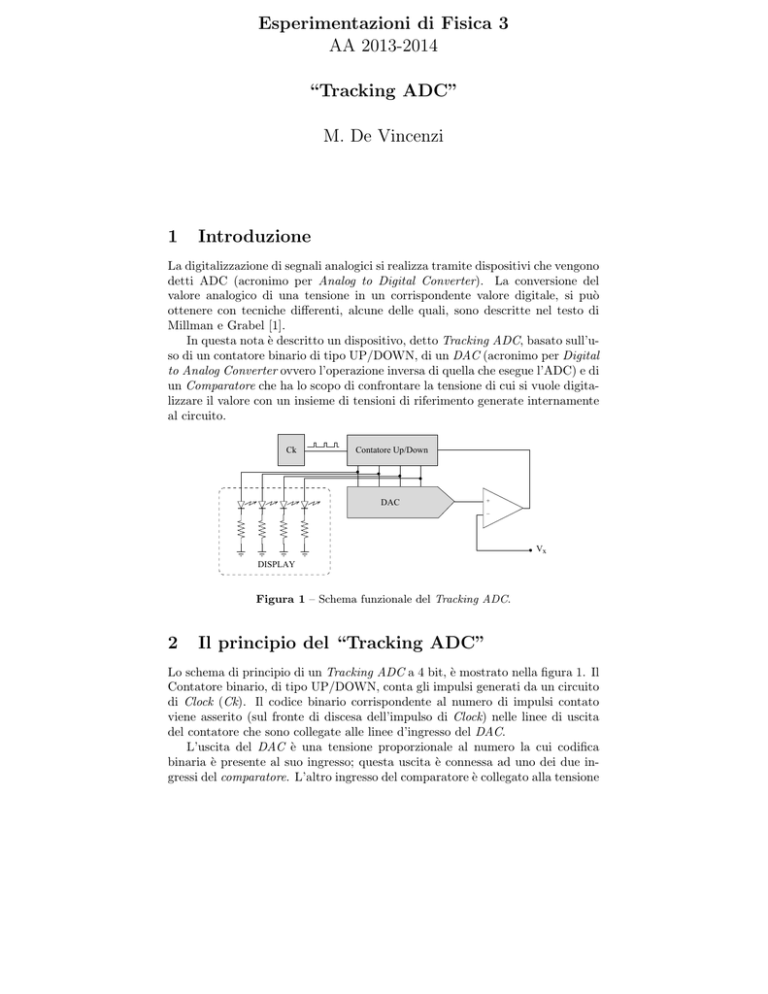

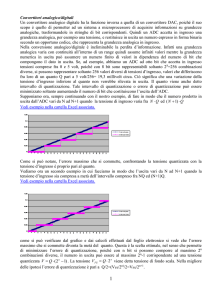

In questa nota è descritto un dispositivo, detto Tracking ADC, basato sull’uso di un contatore binario di tipo UP/DOWN, di un DAC (acronimo per Digital

to Analog Converter ovvero l’operazione inversa di quella che esegue l’ADC) e di

un Comparatore che ha lo scopo di confrontare la tensione di cui si vuole digitalizzare il valore con un insieme di tensioni di riferimento generate internamente

al circuito.

Ck

Contatore Up/Down

DAC

+

−

Vx

DISPLAY

Figura 1 – Schema funzionale del Tracking ADC.

2

Il principio del “Tracking ADC”

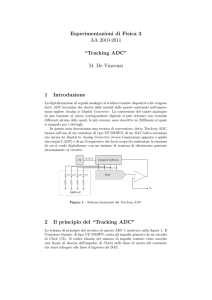

Lo schema di principio di un Tracking ADC a 4 bit, è mostrato nella figura 1. Il

Contatore binario, di tipo UP/DOWN, conta gli impulsi generati da un circuito

di Clock (Ck). Il codice binario corrispondente al numero di impulsi contato

viene asserito (sul fronte di discesa dell’impulso di Clock) nelle linee di uscita

del contatore che sono collegate alle linee d’ingresso del DAC.

L’uscita del DAC è una tensione proporzionale al numero la cui codifica

binaria è presente al suo ingresso; questa uscita è connessa ad uno dei due ingressi del comparatore. L’altro ingresso del comparatore è collegato alla tensione

analogica (Va ) che si vuole digitalizzare. L’uscita del comparatore, collegata al

controllo della modalità di conteggio del contatore, sarà “bassa” (=0), se la

tensione Va è minore di quella in uscita al DAC e di conseguenza il contatore è

nello stato UP (ovvero incrementa il valore del registro che contiene il numero

di impulsi contati), mentre risulterà “alta” (=1) se la tensione Va è maggiore di

quella in uscita al DAC e conseguentemente il contatore sarà nello stato DOWN

(ovvero decrementa il valore del registro che contiene il numero di impulsi contati). Di conseguenza il numero binario immagazzinato dal contatore oscillerà

di un bit attorno alla sua conversione digitale. Lo stato delle linee che indicano

il contenuto del registro di memoria del contatore è ispezionabile tramite un

dispositivo di DISPLAY, che nello schema di figura 1 è realizzato tramite diodi

LED e resistenze di protezione.

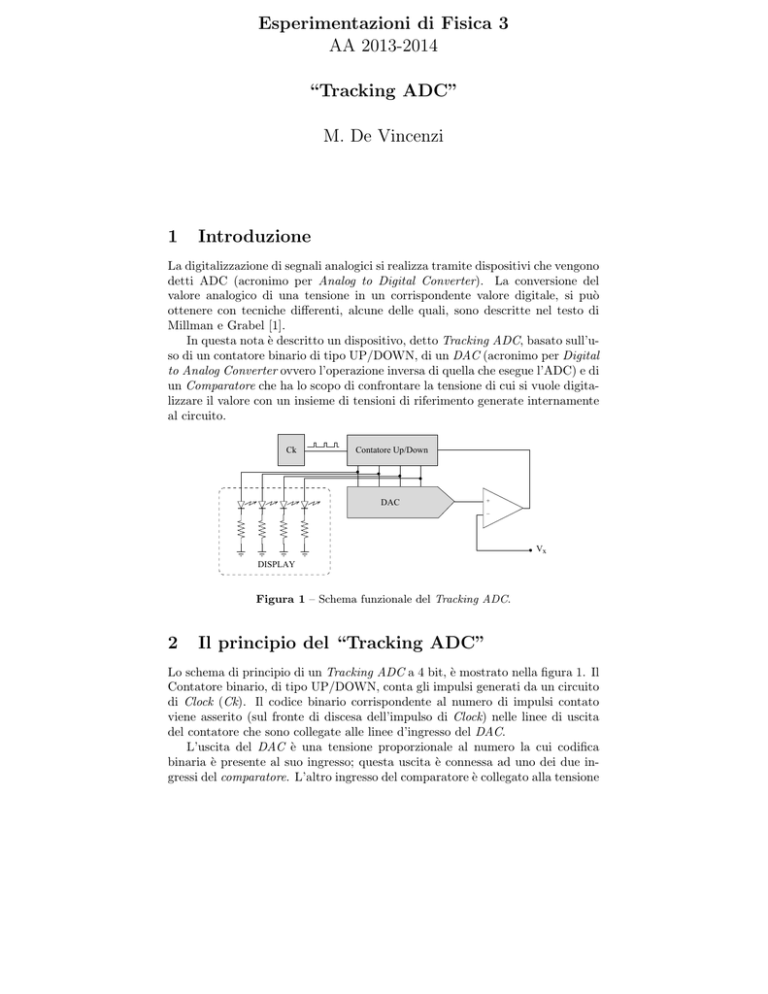

Figura 2 – Nella figura è mostrato l’andamento della risposta di un Tracking

ADC a un segnale analogico (non troppo rapidamente variabile rispetto alla frequenza del clock). Il segnale da convertire è rappresentato dalla linea continua nel

grafico in alto. La risposta dell’ADC è rappresentata dal segnale a scaletta che

prima raggiunge il valore della tensione da convertire e successivamente oscilla ±

un bit attorno al valore analogico. Si noti che il codice binario (Digital output)

“segue” il segnale analogico, effetto che giustifica il nome di Tracking che viene

dato a questo ADC.

3

Il circuito del “Tracking ADC” a 4 bit

Un semplice Tracking ADC a quattro bit può essere realizzato con un contatore Up/Down TTL a quattro bit (74LS191) che conta gli impulsi di un clock

esterno. L’uscita binaria del contatore è collegata ad un DAC (Digital to Analog

Converter) realizzato con un operazionale del tipo uA741 che verrà illustrato

nel seguito. Lo stato delle quattro linee digitali di uscita del contatore è ispezionabile tramite un elementare DISPLAY che utilizza dei diodi emettitori di

luce (LED) e resistenze limitatrici di corrente. Per la funzione di comparatore

è stato scelto il circuito integrato la cui sigla è LM311.

2

Descriviamo nel seguito le caratteristiche principali dei singoli componenti

che costituiscono il progetto di questo Tracking ADC.

Il contatore “74LS191”. E’ un circuito integrato che contiene un contatore

sincrono a 4 bit con una linea di controllo D/U . Nella figura 3 è riportato

lo schema delle connessioni1 dell’integrato con una loro descrizione sommaria.

Per la descrizione completa della funzionalità di questo circuito è opportuna la

consultazione del data sheet disponibile in laboratorio.

Figura 3 – Schema delle connessioni del “74LS191”. QA (LSB), QB , QC ,

QD (M SB) sono le uscite e D/U è l’ingresso per la modalità di conteggio.

A, . . . , D sono gli ingressi (necessari se si intende utilizzare il preset) che vengono memorizzati tramite l’ingresso LOAD. Il pin 14 (CLK) è l’ingresso degli

impulsi che vengono contati. CT EN è l’ingresso per l’abilitazione al conteggio

(CounT ENable). RCO e M AX/M IN sono due uscite necessarie quando più

74LS191 sono connessi in cascata per ottenere un contatore con un numero di bit

maggiore di 4.

Il “DAC”. Il convertitore digitale-analogico (DAC dall’inglese Digital to Analog Converter) può essere realizzato tramite il circuito mostrato in figura 4 che

utilizza una rete detta a scala R-2R in grado di sommare in modo pesato gli

ingressi indicati con 0, 1, 2, 3. I pesi degli ingressi 0, 1, 2, 3 sono proporzionali

rispetticamente a 20 , 21 , 22 , e 23 . La tensione di uscita dell’operazionale è:

Vu = (V0 RF /6R)(b0 2−3 + b1 2−2 + b2 2−1 + b3 20 ),

dove V0 è la tensione corrispondente al bit “1” e b0 , b1 , b2 , b3 rappresentano il

codice binario del numero da convertire (b0 LSB e b3 MSB). Nel progetto si

devono dimensionare correttamente le resistenze R e RF in modo tale che la

tensione massima (in valore assoluto) di uscita, pari a 15V0 RF /16R non superi

il valore della tensione di alimentazione dell’operazionale. Si noti inoltre che

questa configurazione cambia il segno della tensione di uscita rispetto a quella

di ingresso.

1 Alle volte, nei testi tecnici in lingua italiana, lo schema delle connessioni è detto “Piedinatura”, termine gergale, traduzione del termine inglese pinout, con cui si indicano l’insieme

delle caratteristiche, funzioni e disposizione geometrica delle connessioni (pin) di un circuito,

tipicamente un circuito integrato. Il termine non è riportato nella maggior parte dei vocabolari

italiani.

3

"0"

"1"

"2"

"3"

RF

2R

2R

R

2R

2R

R

2R

2R

R

Figura 4 – Schema del DAC a scala R-2R

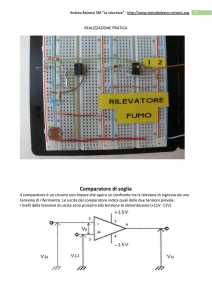

Il Comparatore di tensione Il comparatore di tensione a disposizione (LM311)

è del tipo Open Collector (vedi figura 5) e potrebbe funzionare anche alimentato

in modo asimmetrico (ovvero tra 0 V e 5 V ), tuttavia nel circuito proposto, con

tensioni negative in ingresso, questo tipo di alimentazione del LM311 non si deve utilizzare. Per funzionare correttamente il comparatore LM311 ha bisogno di

una resistenza “Pull-Up” del valore di qualche kΩ (tipico valore della resistenza

di collettore di un transistor).

V CC

+

Resistenza di "Pull−Up"

−

+

−

Figura 5 – La tecnica dell’open-collector nel comparatore LM311.

Osservazioni pratiche. Le transizioni generate dal LM311, da “0” a “1” e

viceversa, sono molto veloci e possono facilmente generare interferenza all’interno del circuito integrato del contatore (accoppiamento capacitivo) modificando

in modo imprevedibile il contenuto del registro del contatore. È opportuno

quindi collegare l’uscita del comparatore a massa con una capacità dell’ordine

di 100 nF per attenuare le componenti ad alta frequenza dell’impulso e quindi

aumentare adeguatamente i tempi di salita e di discesa del segnale d’uscita del

comparatore .

Ground 1

8 V+

+

Input + 2

7 Out

−

6 Balance/Strobe

Input −3

5 Balance

V−4

Figura 6 – Schema delle connessioni o “Piedinatura” del LM311.

4

Il DISPLAY. Per ispezionare lo stato delle linee digitali si può usare il semplice dispositivo mostrato in figura 1, che consiste di un diodo LED con in serie

un’opportuna resistenza che limita la corrente nel diodo. Se la linea è “alta” il

diodo è polarizzato direttamente e quindi conduce. Il passaggio della corrente

in questo tipo di diodi provoca l’emissione di luce ed il diodo appare come una

lampadina accesa. Se la linea da ispezionare è “bassa” il diodo è spento e non

emette luce. Quindi se il diodo relativo ad una generica linea n è emette luce

potremo dire che il bit n-simo è “1” altrimenti sarà a “0”. Dal punto di vista

elettrico la potenza necessaria all’accensione dei diodi viene generata dal circuito del contatore per cui i livelli di tensione trasferiti al DAC, se il valore della

resistenza limitatrice di corrente fosse troppo basso, potrebbero influenzare la

linearità dell’ADC.

4

Caratterizzazione dell’ADC

Quali sono le principali caratteristiche dell’ADC costruito? Come qualsiasi strumento di misura anche questo ADC, una volta realizzato, deve essere caratterizzato, ovvero se ne devono misurare e documentare le caratteristiche principali.

A questo scopo è molto utile fare uso del grafico della cosiddetta Funzione di

Trasferimento dell’ADC che consiste nel rappresentare il codice binario, uscita dell’ ADC, in funzione della tensione analogica da digitalizzare (vedi figura

7). Dall’esame della funzione di trasferimento possono essere ricavate alcune

caratteristiche di particolare importanza come la Risoluzione, l’Accuratezza e la

Non-linearità che descriveremo di seguito.

Risoluzione. La risoluzione di un ADC è determinata dal numero n di bit

usati per la conversione e dal valore della tensione di fondo scala VF S , e vale

VF S /2n . Questo valore rappresenta la minima variazione della tensione d’uscita

e rappresenta l’ampiezza in volt del bit meno significativo (LSB).

Accuratezza. Un ADC converte tutti i valori di un segnale analogico compresi

in un definito intervallo di ampiezza VLSB , in un unico codice binario. Quindi

la conversione analogico–digitale genera un’incertezza (standard)

√ di principio

legata all’interizzazione del segnale analogico che vale (VLSB )/ 12.

Non-Linearità. In generale gli ADC sono progettati in modo che il codice binario d’uscita rappresenti un numero proporzionale al segnale analogico al loro

ingresso: ADC lineari2 . Nella realtà questa richiesta può essere solo approssimativamente soddisfatta a causa di molte cause come le incertezze su parametri

e i comportamenti non ideali dei componenti dell’ ADC. Alcuni di questi effetti,

essendo sistematici, possono essere parzialmente corretti attraverso procedure

2 In particolari applicazioni quando, ad esempio, è necessario estendere la dinamica dei

segnali da convertire si utilizzano ADC con scale di conversione non lineari, ad esempio scale

logaritmiche, lineari a tratti, quadratiche e altre

5

Funzione di trasferimento

Figura 7 – Esempio di Funzione di trasferimento di un ADC a 3 bit con fondo

scala di 8.0 V . Nella figura sono mostrate la funzione di trasferimento ideale e una

possibile reale. La retta (a punto–linea) tracciata nel grafico congiunge i centri

dei “gradini” della funzione di trasferimento ideale.

di taratura. La valutazione quantitativa della non-linearità di un ADC viene generalmente espressa da due parametri detti Non-Linearità Differenziale (DNL)

e Non-Linearità Integrale (INL).

DNL. La non-linearità differenziale DN L è un parametro definito per ogni

valore del codice D di conversione da analogico a digitale e vale:

DN L =

|VD+1 − VD |

−1

VLSB

(1)

dove VD è il (minimo) valore analogico convertito nel codice D e VLSB è il valore

analogico associato al bit meno significativo (di progetto). A parole potremo

dire che il parametro DN L rapporta l’ampiezza dei “gradini” della funzione di

trasferimento reale con quella di progetto sottraendo 1, in modo tale che se le

due ampiezze sono uguali il parametro DN L è nullo.

INL. Il parametro IN L (non-linearità integrale) per il “gradino” in esame, è

pari alla distanza fra il centro del gradino della funzione di trasferimento reale

e quella ideale. E’ facile dimostrare che la non-linearità integrale per un dato

codice è pari alla somma dei DNL dei codici precedenti.

Come esempio di quanto esposto riportiamo comportamento e analisi di un

ipotetico ADC a 3 bit con un fondo scala di progetto di 8 V . La funzione di trasferimento di questo ADC è riportata in due versioni nella figura 7. Nella figura

la scala tratteggiata rappresenta la funzione di trasferimento ideale e quella a

tratto continuo una (possibile) funzione di trasferimento reale. Nella tabella 1

6

sono riportati i valori numerici dell’esempio citato assieme alla valutazione del

DNL e del INL.

Tabella 1 – Esempio di un ipotetico ADC a 3 bit

Numero

progressivo

0

1

2

3

4

5

6

7

5

Codice

binario

000

001

010

011

100

101

110

111

Tensione

ideale (V)

1.00

2.00

3.00

4.00

5.00

6.00

7.00

8.00

Tensione

reale (V)

0.80

2.16

3.12

3.60

4.80

5.60

7.04

8.00

DNL

INL

-0.20

0.36

-0.04

-0.52

0.20

-0.20

0.44

0.0

-0.20

0.16

0.12

-0.40

-0.20

-0.40

-0.004

0.

Osservazioni pratiche

E’ opportuno “bloccare” la tensione di alimentazione di ogni “chip” localmente

(ovvero in prossimità del circuito) con una capacità dell’ordine delle centinaia di

nF . Questo accorgimento vale in generale per ogni tipo di circuito alimentato

da un tensione costante, ma in particolare è valido per i circuiti digitali. In questi ultimi infatti sono presenti segnali con fronti di salita rapidi che richiedono

alimentazioni in grado di erogare potenza in modo sufficientemente veloce. I

fili che portano le alimentazioni e le connessioni nella “basetta” hanno un induttanza che moltiplicata per la resistenza del circuito alimentato dà il tempo

caratteristico necessario al ripristino della tensione di alimentazione. In questo

intervallo temporale, con una tensione di alimentazione che varia net tempo,

il circuito può mostrare comportamenti imprevedibili che ne compromettono il

corretto funzionamento.

Riferimenti Bibliografici

[1] – Milman e Grabel Microelectronics McGraw Hill. Si veda il cap. 16

paragrafo 4.

7