4

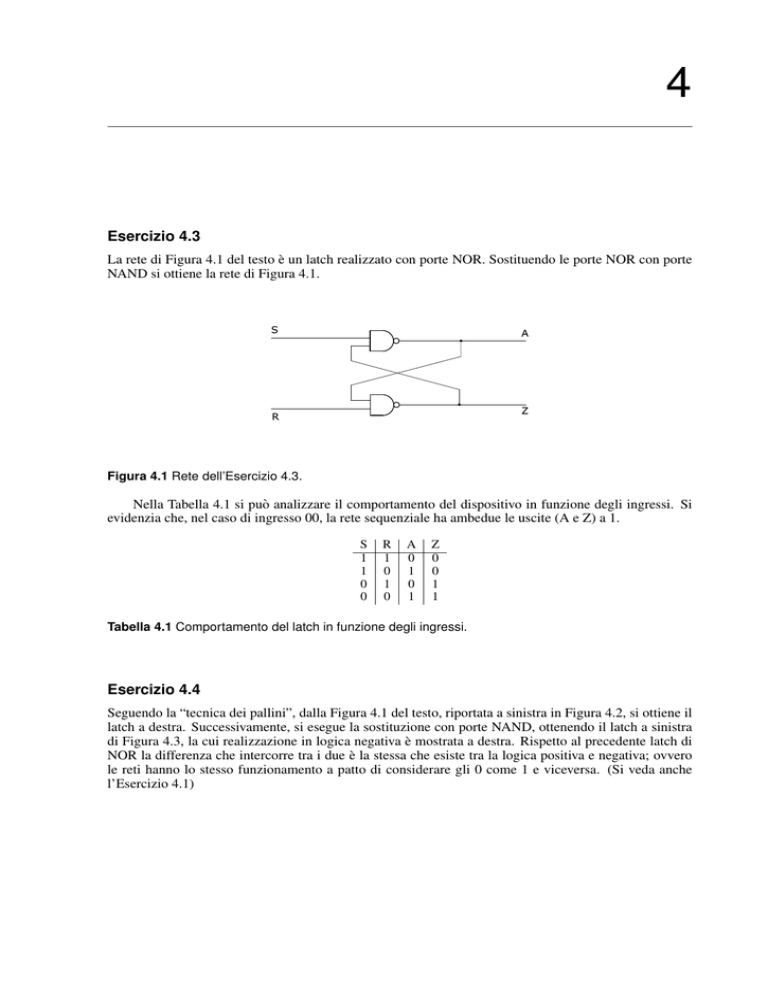

Esercizio 4.3

La rete di Figura 4.1 del testo è un latch realizzato con porte NOR. Sostituendo le porte NOR con porte

NAND si ottiene la rete di Figura 4.1.

Figura 4.1 Rete dell’Esercizio 4.3.

Nella Tabella 4.1 si può analizzare il comportamento del dispositivo in funzione degli ingressi. Si

evidenzia che, nel caso di ingresso 00, la rete sequenziale ha ambedue le uscite (A e Z) a 1.

S

1

1

0

0

R

1

0

1

0

A

0

1

0

1

Z

0

0

1

1

Tabella 4.1 Comportamento del latch in funzione degli ingressi.

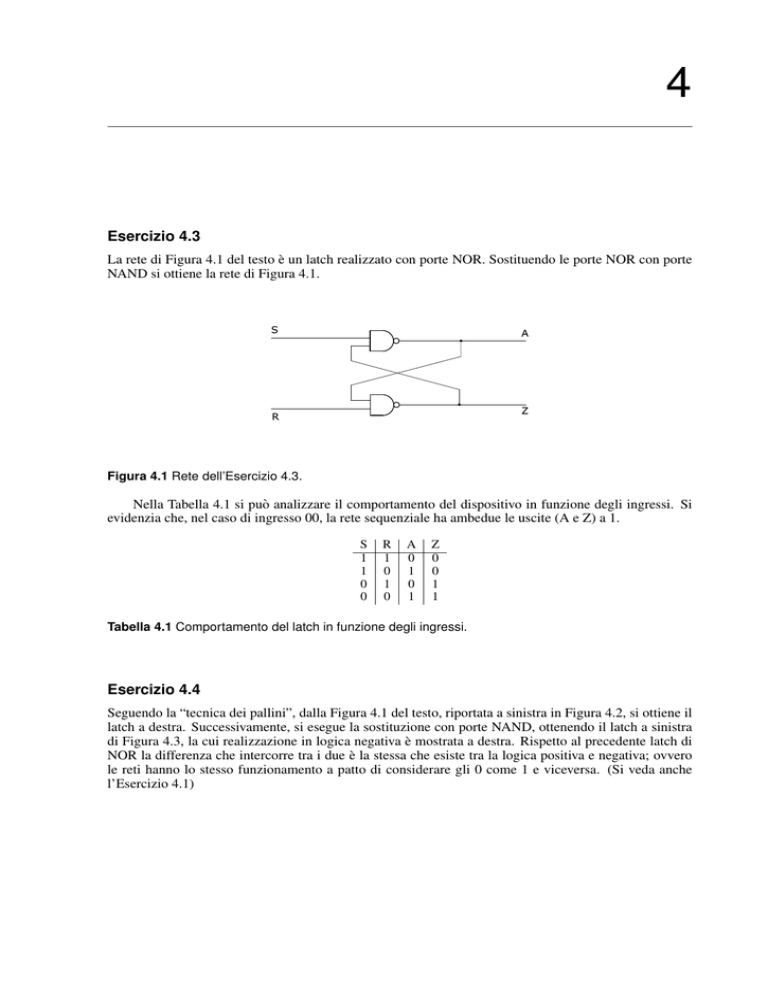

Esercizio 4.4

Seguendo la “tecnica dei pallini”, dalla Figura 4.1 del testo, riportata a sinistra in Figura 4.2, si ottiene il

latch a destra. Successivamente, si esegue la sostituzione con porte NAND, ottenendo il latch a sinistra

di Figura 4.3, la cui realizzazione in logica negativa è mostrata a destra. Rispetto al precedente latch di

NOR la differenza che intercorre tra i due è la stessa che esiste tra la logica positiva e negativa; ovvero

le reti hanno lo stesso funzionamento a patto di considerare gli 0 come 1 e viceversa. (Si veda anche

l’Esercizio 4.1)

Figura 4.2 Latch di soli NOR di Figura 4.1 del testo e sua trasformazione in rete di NAND.

Figura 4.3 Latch di soli NAND in logica positiva, a sinistra, e in logica negativa, a destra.

Esercizio 4.5

In Figura 4.4 viene presentato lo schema generale di soluzione del problema. Si tratta di definire la rete

combinatoria che nel caso (a) ha come ingressi S, R e y, e la cui uscita T ha l’effetto di far commutare

il flip flip in modo che appaia come un SR. Questo schema, mutatis mutandis, si usa per qualunque

trasformazione tra diversi tipi di flip flop.

Figura 4.4 Schematizzazione del problema della creazione di un FFSR sfruttando un FFT. Lo schema

è valido anche nel caso generale.

Il problema del caso (a) è schematizzato in Figura 4.4. In Tabella 4.2 sono mostrati gli ingressi

richiesti per le possibili transizioni dei due tipi di FF.

La mappa di y’ in funzione di S, R e y è mostrata a sinistra in Figura 4.5, applicando il procedimento

descritto al paragrafo A.5 del testo, dalla mappa di y’ si passa alla mappa di T, che assume la forma a

destra in Figura 4.5, la cui copertura porta alla seguente espressione per T:

T = Sy + Ry

2

y → y’

0→0

0→1

1→0

1→1

S

0

1

0

-

R

0

1

0

T

0

1

1

0

Tabella 4.2 Transizioni di stato e corrispondenti ingressi per i Flip Flop SR e T.

La rete corrispondente è riportata in Figura 4.6.

Figura 4.5 Mappe Esercizio 4.4a.

Figura 4.6 Rete Esercizio 4.4a.

Il punto (b) chiede di ricavare un FFSR da un FFD e un FFJK da un FFD. In Tabella 4.3 sono

mostrate le 3 tabelle di transizione per i FF usati. Mentre in Figura 4.7 le mappe relative alle transizioni.

y → y’

0→0

0→1

1→0

1→1

S

1

0

-

R

0

1

0

J

0

1

0

0

K

0

0

1

0

D

0

1

0

1

Tabella 4.3 Transizioni di stato e corrispondenti ingressi per i FFSR, FFJK e FFD

Poichè per un FFD vale l’equazione di stato y ′ = D, si tratta semplicemente di imporre D = S +Ry

per il caso della trasformazione FFSR → FFD e D = Jy + Ky per la trasformazione FFJK → FFD. Si

trovano cosı̀ le reti mostrate rispettivamente a sinistra e destra in Figura 4.8.

3

Figura 4.7 Mappa Esercizio 4.4b (FFSR e FFJK da FFD).

Figura 4.8 Reti che realizzano, a sinistra un FFSR a partire da un FFD, mentre a destra un FFJK da un

FFD.

Per quanto ci si riferisce alla costruzione di un FFD da un FFT, si riportano in Tabella 4.4 le

transizioni di stato e in Figura 4.9 le mappe di T corrispondenti. In Figura 4.10 la rete risultante.

y → y’

0→0

0→1

1→0

1→1

T

0

1

1

0

D

0

1

0

1

Tabella 4.4 Transizioni di stato e corrispondenti ingressi per i FFT e FFD

Figura 4.9 Mappa Esercizio 4.4c (FFD da FFT). T = y ⊕ D.

Esercizio 4.6

Il valore F0h corrisponde a 1111 0000b. Qualunque sia il tipo di FF utilizzato per realizzare il registro, si

tratta di legare PR e CL a massa o a Vcc in modo da portare i singoli FF al valore richiesto all’atto della

messa sotto tensione (Figura 4.11). La rete a destra di Figura 4.11 genera il segnale Clear/Set quando

viene asserito R. Si noti la presenza di un inverter Schmitt triggered, per generare un’onda il più possibile

quadra.

4

Figura 4.10 Rete che realizza un FFD da un FFT.

Figura 4.11 A sinistra i collegamenti necessari per il caricamento in presenza di un segnale di Clear/Set;

a destra la rete che genera il segnale Clear/Set.

Esercizio 4.7

La rete che deve essere progettata, ha un unico ingresso (x) e una sola uscita (z) che al 5◦ clock presenta

la parità, mentre sui precedenti presenta x. In Figura 4.12 è mostrato lo schema in questione.

Figura 4.12 Schema per l’ Esercizio 4.7.

In Figura 4.13 c’è il diagramma di transizione degli stati. La notazione usata per etichettare gli archi

è quella relativa al modello di Mealy. La colonna a sinistra (senza apici) individua un numero pari di 1,

quella a destra un numero dispari. Supponendo di seguire lo schema a “parità pari”, sul 5◦ clock si ha

z=0 se si è nello stato 4, altrimenti z=1 se si è nello stato 4’, (indipendentemente da x).

Si può ora ricavare la tabella di flusso e delle transizioni di stato (Tabella 4.5).

Codificando gli stati come sotto si ottengono le mappe in Figura 4.14.

0:0000

1:0001 1’:1001

2:0010 2’:1010

3:0011 3’:1011

4:0100 4’:1100

5

Figura 4.13 Diagramma degli stati per l’Esercizio 4.7.

SP

0

1

2

3

4

1’

2’

3’

4’

x

1,0

2,0

3,0

4,0

0,0

2’,0

3’,0

4’,0

0,1

z

1’,1

2’,1

3’,1

4’,1

0,0

2,1

3,1

4,1

0,1

Tabella 4.5 Tabella di flusso corrispondente al diagramma di stato di Figura 4.13

Si noti che questa non è la codifica più conveniente in termini di minimizzazione della rete, ma è

quella più naturale (rende comprensibile lo stato). Dalle mappe si ricavano le seguenti funzioni di stato

e uscita, dalle quali può essere dedotto lo schema della rete.

y0′ = y1 (y0 ⊕ x)

y1′ = y2 (y3 + y0 )

y2′ = y0 y3 + y0 y1 y2

y3′ = y3 (y0 y2 + y0 y2 ) + y0 y1 y2 y3

z = y0 y1 y2 y3 x + x(y0 + y1 ).

Soluzione alternativa

Possiamo scomporre il problema in modo da avere

• Un contatore che fornisce il segnale c sul 5◦ clock

• Una rete che calcola p (parità)

• Una rete che presenta su z il segnale x sui clock da 0 a 3, e p clock 4.

Ne deriva lo schema di Figura 4.15.

Il generatore di parità di Figura 4.15 ha il diagramma di stato di Figura 4.16. Il diagramma rappresenta una macchina di Mealy. In ingresso c’è la coppia x, c. L’ ingresso c è dato dall’uscita di un

6

Figura 4.14 Mappe che rappresentano la Tabella 4.5 secondo la codifica indicata.Esercizio 4.6.

Figura 4.15 Schema riassuntivo della soluzione alternativa all’ Esercizio 4.6.

semplice contatore modulo 5. Dalla copertura della mappa si ricava:

p = yx + yc + yxc

Figura 4.16 A sinistra è mostrato il diagramma di stato del generatore di parità dell’Esercizio 4.6, sugli

archi viene riportato xc/p . A destra la mappa relativa.

La rete che realizza il generatore di parità è in Figura 4.17.

7

Figura 4.17 Generatore di parità dell’ Esercizio 4.7 risultante dalla soluzione alternativa.

Esercizio 4.8

La sequenza riconosciuta è 10011. Z1 =1 solo dopo il fronte di clock che ha fatto caricare nel registro

questa configurazione (il quinto fronte). Con riferimento alla notazione di Figura 4.18, se i FF commutano sul fronte di salita (a sinistra in Figura), Z è 1 durante il △1 del clock che ha caricato 10011 mentre

se i flip flop commutano sul fronte di discesa (a destra in Figura), Z è 1 durante △2 del medesimo clock.

Figura 4.18 Tempi di commutazione per i FF dell’Esercizio 4.8.

Esercizio 4.9

Il diagramma della macchina che riconosce la sequenza 10011 è rappresentato in Figura 4.19. Essendo

5 gli stati da codificare, ci servono 3 bit. Ad esempio si può utilizzare la seguente codifica:

A 000

B 001

C 011

D 010

E 100

dalla quale deriva la Tabella delle transizioni 4.6.

Notare che la rete riconosce le finestre, ma in modo non sovrapposto. A titolo di esempio si mostra

l’uscita in riferimento a un flusso di dati in ingresso:

x

z

1001100110011

0000100000001

Le corrispondenti mappe sono mostrate nella Figura 4.20, la cui copertura porta alle funzioni a destra

nella stessa Figura. La rete è realizzata in Figura 4.21.

Per analizzare quale delle due soluzioni sia la migliore in termini di porte e FF basta semplicemente

contare. La Figura 4.60 del testo risolve il problema con uno shift register, che sarà composto da 5 FF, 2

8

Figura 4.19 Diagramma di stato del riconoscitore della sequenza 10011, riconosciuta in ordine da

sinistra a destra. Esercizio 4.9.

y1

0

0

0

0

0

0

0

0

1

1

y2

0

0

0

0

1

1

1

1

0

0

y3

0

0

1

1

1

1

0

0

0

0

y1′

0

0

0

0

0

0

1

0

0

0

x

1

0

1

0

1

0

1

0

1

0

y2′

0

0

0

1

0

1

0

0

0

1

y3′

1

0

1

0

1

0

0

0

0

1

z

0

0

0

0

0

0

0

0

1

0

Tabella 4.6 Tabella delle transizioni del riconoscitore della sequenza 10011, Esercizio 4.8.

y1′ = y2 y3 x

y2′ = y3 x + y1 x

y3′ = y3 x + y1 x

z = y1 x

Figura 4.20 Mappe e funzioni relative alla Tabella di transizione 4.6 dell’Esercizio 4.9.

porte NOT e 2 porte AND. La soluzione presentata in Figura 4.21 utilizza 1 porta NOT, 5 porte AND, 2

porte OR e 3 FF. Dire quale delle due soluzioni sia la migliore è difficile.

Un’ analisi di questo tipo ha però poco senso, in quanto va visto come i componenti vengano resi

disponibili sul mercato. Si hanno allora delle sorprese. Per costruire lo shift register a 5 bit di Figura 4.60

occorre utilizzare il componente SN74198, un 8 bit Universale Bidirezionale Shift Register, a 28 piedini

mentre per le altre 4 porte si può utilizzare, facendo qualche trasformazione, il componente SN7400,

costituito da 4 porte NAND a 2 ingressi, con un totale di 14 piedini. Con 2 componenti si risolve il

circuito. Per la rete in Figura 4.21 servono 2 componenti SN7474, ognuno dei quali è composto da 2

FFD Positive Edge Triggered a 14 piedini, e per le porte, basta utilizzare 2 integrati SN7400, specificati

sopra (ciò presuppone però una strutturazione della rete in forma di soli NAND).

Nel primo caso si è quindi utilizzato 2 componenti integrati con un totale di 42 piedini di collegamento, mentre nel secondo caso sono serviti 4 integrati per un totale di 56 piedini collegati. Specifiche

9

Figura 4.21 Rete logica che riconosce la sequenza 10011. Esercizio 4.9.

sugli integrati, specificatamente sulla serie SN74xx si trovano su:

http://www.rodaronline.com/ci/ci2.htm.

Esercizio 4.10

La rete di Figura 4.48 è un contatore modulo 3 realizzato con FFJK. Tenuto conto del funzionamento del

FFJK (Tabella 4.7), il comportamento della rete, a partire dallo stato 00 è quello di Tabella 4.8.

J

0

0

1

1

K

0

1

0

1

y′

y

0

1

y

Tabella 4.7 Modalità di funzionamento del flip flop JK.

Clock n◦

0

1

2

y0 y1

00

01

10

y0′ y1′

01

10

00

Tabella 4.8 Funzionamento del contatore di Figura 4.61. Con y0 e y1 si indicano rispettivamente l’uscita

del FF di sinistra e di destra di Figura 4.61.

Esercizio 4.11

Utilizzando per gli stati A,B,C la seguente codifica: A 00, B 01 e C 10, si ottiene la tabella delle

transizioni mostrata in Figura 4.22.

Alla tabella delle transizioni corrispondono le mappe a destra di Figura 4.23 dalle quali si ricavano

le funzioni a sinistra della stessa Figura. Infine la realizzazione della rete è mostrata in Figura 4.24.

10

Figura 4.22 Tabella delle transizioni Esercizio 4.11.

y0′ = y0 x + y1 x

y1′ = y0 y1 x

z = y0

Figura 4.23 Mappe e funzioni della Tabella 4.22 dell’Esercizio 4.11.

Figura 4.24 Rete logica dell’ Esercizio 4.11.

Esercizio 4.12

Cominciamo con la realizzazione tramite FFJK. Per semplicità consideriamo il caso n = 2. Si tratta di

collegare i flip flop in modo tale che ciascun FF divida la frequenza del clock per 2 e di usare lo stato del

FF come clock per il successivo. Con FFJK ciò si ottiene come in Figura 4.25. Ovviamente se n > 2 si

tratta di aggiungere il corrispondente numero di FF.

Nel caso di flip flop D, la divisione di frequenza del primo FF (y0 ) comporta che esso deve cambiare

stato ad ogni clock, ciò impone che l’ingresso sia il complemento dello stato. Dunque:

D 0 = y0

da cui deriva la rete di sinistra in Figura 4.26. Per quanto riguarda il secondo FF, esso si comporterà

come il precedente, ma userà come clock il segnale y0 . Ne deriva la rete a destra di Figura 4.26.

11

Figura 4.25 Realizzazione del contatore dell’Esercizio 4.11 con FFJK. L’uscita y0 è un segnale periodico

con frequenza pari a metà di quella del clock. Il segnale y1 ha frequenza pari a metà di quella di y0 .

Figura 4.26 A sinistra la divisione di frequenza in un FFD; a destra la realizzazione del contatore dell’Esercizio 4.11 con FFD. L’uscita y0 è un segnale periodico con frequenza pari a metà di quella del clock.

Il segnale y1 ha frequenza pari a metà di quella di y0 .

Esercizio 4.13

Per progettare un contatore sincrono modulo N ̸= 2n conviene partire direttamente dalla tabella di flusso,

si tratta di una tabella degenere, in quanto è priva di ingressi. In Figura 4.27 vengono riportati la tabella

di flusso di un generico contatore sincrono modulo N , quella di un contatore modulo 5 e la tabella delle

transizioni di stato corrispondenti a quest’ultima (avendo codificato gli stati in modo naturale).

Sp

0

1

...

N-2

N-1

Sf

1

2

...

N-1

0

Sp

0

1

2

3

4

Sf

1

2

3

4

0

y1 y0

000

001

010

011

100

y1′ y0′

001

010

011

100

000

Figura 4.27 Tabella di flusso di un contatore modulo N (a sinistra), tabella di flusso di un contatore

modulo 5 (al centro) e transizione degli statio per quest’ultimo (a destra) .

Dalla copertura delle mappe a sinistra in Figura 4.28, ricaviamo le funzioni a destra nella stessa

Figura. Mentre in Figura 4.29 è mostrata la rete che realizza il contatore.

12

y0′ = y1 y2

y1′ = y2 y1 + y1 y2

y2′ = y0 y2

Figura 4.28 Mappe e funzioni che realizzano il contatore modulo 5 dell’Esercizio 4.13.

Figura 4.29 Rete che realizza il contatore modulo 5 dell’ Esercizio 4.13.

Esercizio 4.14

Il flip flop T cambia stato quando l’ingresso T è a 1. Dunque, essendo tutti gli ingressi dei flip flop

permanentemente a 1 essi sono soggetti a cambiare stato ad ogni clock. Il primo FF commuta in tutti i

clock, il secondo essendo collegato all’uscita del primo commuta con frequenza dimezzata, il terzo con

frequenza ulteriormente dimezzata. Si veda la Tabella 4.9. Si deduce che quello di Figura 4.49 è un

contatore asincrono modulo 8.

Esercizio 4.15

In Figura 4.30 viene riportato il diagramma di stato in cui gli stati sono già codificati. Ad esso corrisponde

la Tabella 4.10 e le mappe di Figura 4.31, dalle quali si ricavano le funzioni a destra nella stessa Figura.

Se si impiegano dei FFD queste espressioni corrispondono agli ingressi dei FF. Si ottiene allora la rete in

Figura 4.32.

13

Clock n◦

0

1

2

3

4

5

6

7

y3′ y2′ y1′

000

001

010

011

100

101

110

111

y3 y2 y1

111

000

001

010

011

100

101

110

Tabella 4.9 Funzionamento della rete di Figura 4.62. In neretto le variabili di stato corrispondenti ai FF

che ricevono il clock.

Figura 4.30 Diagramma di stato per l’ Esercizio 4.14. Sui rami sono riportati i valori dell’ingresso. Si noti

che il passaggio tra le due modalità di conteggio avveniene solo in corrispondenza dello stato 100.

y0 y1 y2

000

001

010

011

100

101

110

x

0

001

010

011

100

101

110

000

1

001

010

011

100

000

110

000

Tabella 4.10 Tabella transizione stati Esercizio 4.15.

Esercizio 4.16

Si faccia riferimento a un contatore sincrono realizzato con FFJK. Indicando con y1 . . . yn le uscite dei

FF, il generico F Fi−esimo deve avere un ingresso pari a (y1 · y2 · . . . · yi−1 ) ⊕ yi se conta in salita e pari a

(yi+1 · yi+2 · . . . · yn ) ⊕ yi se conta in discesa. La Figura 4.33 illustra la struttura dell’i-esimo dispositivo.

14

y0′ = y1 y2 + y0 y2 + y0 y1 x,

y1′ = y0 y1 y2 + y2 y1

y2′ = y0 y2 + y1 y2 y.

Figura 4.31 Mappe dell’ Esercizio 4.15, dalla cui copertura si ricavano le funzioni a destra.

Figura 4.32 Rete logica Esercizio 4.15.

Esercizio 4.18

Per risolvere l’Esercizio si possono usare due contatori a caricamento parallelo. Per il numero A possiamo usare un up-counter e per B possiamo utilizzare un down-counter. Si caricano entrambi i numeri nei

contatori e si inizia il conteggio. Quando si attiva il CO di B, in A avremo la somma dei due numeri. CO

è il segnale che un contatore attiva quando raggiunge il valore massimo, se è un up-countero minimo se è

un down-counter, serve a capire se siamo arrivati a fine conteggio. Avendo fatto proseguire il conteggio

di A per B volte abbiamo eseguito la somma dei due numeri. L’unica attenzione è riguardo all’overflow,

cioè A+B deve sempre essere inferiore al massimo valore conteggiabile dal contatore A, altrimenti si

avrebbe un reset dello stesso e un mal funzionamento della rete. Il collegamento dei due contatori è in

Figura 4.34.

Esercizio 4.19

A parte il clock, l’unico segnale di comando è X. Esso deve servire a comandare il caricamento di RA e

RB e ad avviare il conteggio, a cui sarà legati il trasferimento del risultato il RC al momento dovuto.

15

Figura 4.33 FFi−esimo dell’Esercizio 4.16. Il segnale UD imposta la modalità di funzionamento. Con

UD=1 conta in avanti mentre con UD=0 il dispositivo conta all’indietro.

Figura 4.34 Sommatore A+B. Esercizio 4.18. Si noti che il passaggio a 1 di x fa operare i due contatori.

Il passaggio a 1 di CO ferma l’incremento del contatore di sinistra. I valori di A e B devono essere

precaricati nei due contatori prima del passaggio a 1 di x (non mostrato in figura).

Per quanto si riferisce al caricamento di RA e RB la specifica sottintende che esso deve essere fatto

in parallelo. Si deve quindi immaginare l’esistenza di due percorsi che portano in RA e RB i dati da

caricare.

Supporremo di effettuare il caricamento dei registri secondo la tecnica (sincrona) rappresentata dalle

Figure 4.29 e 4.37 del testo. Facciamo l’ipotesi che il comando di caricamento prevalga sullo scorrimento

in modo che il clock che trova il segnale di caricamento a 1 faccia solo caricare. In conclusione si tratta

di generare due opportuni segnali temporali noti, RAeBin e RCin . Il segnale RAeBin può essere anche

usato per azzerare lo stato del flip flop che memorizza il riporto.

RAeBin deve essere asserito solo sul clock su cui si caricano i registri (clock 0). Poichè non è

specificata la durata di X, occorre generare RAeBin da X. Supponendo che i registri RA e RB operino

sul fronte di discesa del clock, conviene che RAeBin duri esattamente un periodo di clock, ma tra i fronti

di salita. Dunque RAeBin deve avere la temporizzazione di Figura 4.35. Il segnale viene portato a 1 sul

fronte di salita del clock che trova X a 1 e riportato a 0 sul fronte di salita seguente. In tal modo RA e RB

vengono caricati sul fronte di discesa intermedio del clock 0. I successivi 5 impulsi di clock determinano

il caricamento in RA dei bit di somma (calcolati via via).

16

Figura 4.35 Temporizzazione dei segnali RAeBin e RC rispetto al clock ed al segnale X. Esercizio 4.19.

La somma viene perciò a trovarsi in RA dal fronte intermedio del clock 5. Se anche RC opera sul

fronte di discesa il trasferimento del risultato in questo registro può essere effettuato sul clock successivo

(clock 6), avendo asserito RCin .

In conclusione si deve progettare la rete (di Moore, operante sui fronti di salita) che genera i segnali

temporizzati RAeBin e RCin , come in Figura 4.35. La schematizzazione della rete è riportata in alto in

Figura 4.36.

Figura 4.36 In alto: schema della rete per la generazione dei segnali RAeBin e RCin a partire dal

segnale X e dal clock. In basso: il diagramma di stato della rete. Le uscite sono ordinatamente, RAeBin

e RCin .

Si tratta di un problema analogo a quello della generazione del segnale di WAIT del Paragrafo 4.5.1

del testo. Il diagramma di stato è quello in basso in Figura 4.36. Un eventuale ritorno a 1 di X prima

17

della conclusione dell’operazione è ininfluente.

Si noti che, diversamente, da quanto indicato nel testo, il trasferimento in RC avviene sul (fronte di

discesa del) clock 6. In Figura 4.37 è riportato lo schema finale della soluzione.

Figura 4.37 Schema finale della interconnessione tra la rete di generazione dei segnali RAeBin e RCin

e lo schema di somma dell’esercizio. Si noti che il segnale RAeBin viene usato anche per azzerare lo

stato del flip-flop usato per tenere traccia del riporto.

Esercizio 4.20

Per eseguire il trasferimento al 7◦ clock, basta aggiungere uno stato al diagramma di Figura 4.36.

Esercizio 4.23

Questo esercizio non era inizialmente nel testo. Si veda l’errata corrige.

In Figura 4.38 viene dato lo schema di principio. La rete GENW genera un segnale di WAIT, della

Figura 4.38 Schema di principio per la generazione di un segnale di WAIT.

durata di uno o più periodi di clock, quando viene asserito l’ingresso X. Nello schema di figura il blocco

GX rappresenta un componente del sistema (memoria o periferica di ingresso/uscita) che richiede la

generazione del segnale WAIT. Nel caso della memoria, la linea X passa allo stato di asserito a seguito

18

della generazione da parte della CPU di un indirizzo relativo a blocco di memoria lento (rispetto alla

CPU).

La specifica viene sintetizzata dal diagramma temporale di Figura 4.39. Per garantire che l’uscita

WAIT duri esattamente un periodo di clock, basta renderla sincrona rispetto al clock, ovvero renderla

funzione del solo stato della rete. Occorre quindi riferirsi al modello di Moore. In Figura 4.40 è stato

disegnato il diagramma di stato deducibile dalle specifiche.

Figura 4.39 Diagramma temporale per il WAIT. Il diagramma riporta in corrispondenza del clock lo stato

in cui si trova la rete (secondo il diagramma di stato di Figura 4.40).

A

B

C

D

X=0

B

C

D

D

X=1

A

C

A

A

−

0

0

1

0

Figura 4.40 Diagramma degli stati della macchina di Moore che sintetizza le specifiche del generatore

di WAIT e relativa tabella di flusso. Lo stato A corrispondente è quello in cui si trova la rete a riposo.

Al passaggio di X a zero la rete si porta nello stato B, dove l’uscita è mantenuta a zero in modo da

far scorrere un periodo di clock. Al clock successivo la rete passa nello stato C, dove l’uscita è uno,

e ci resta solo per un periodo di clock, come previsto dal punto 4 della specifica. Lo stato D serve ad

attendere il ritorno di X a uno.

Essendo 4 gli stati occorrono 2 variabili di stato, cioè due flip-flop per codificarli.1 Se si codificano

gli stati nel seguente modo: A = 00, B = 01, C = 11, D = 10, si ottengono la tabella delle transizioni

di Figura 4.41 e le corrispondenti mappe di Karnaugh riportate a fianco.

Dalle mappe di Figura 4.41 si ottengono le relazioni seguenti per y1′ , y2′ e WAIT:

y1′ = y1 x + y1 y2 ;

y2′ = y2 y1 + y1 x;

WAIT = y1 y2

da cui si deduce immediatamente lo schema della rete nel caso di realizzazione con FFD (basta porre

D1 = y1′ e D2 = y2′ ).

Se si usano flip-flop JK si ottiene:

J1 = y2 ;

K1 = x;

J2 = y1 x;

K2 = y1

La rete risultante è disegnata in Figura 4.42. Vale la pena di osservare che se si fosse voluto avere WAIT

= 1 per k periodi di clock, sarebbe bastato sostituire lo stato C con una sequenza obbligata di k stati

(C1 , C2 , ..., Ck ). In questo caso ogni variazione di X nell’intervallo dallo stato B allo stato Ck compresi

1

Prendiamo flip-flop che commutano sul fronte di discesa.

19

sarebbe stato irrilevante. È anche facile ottenere WAIT = 1 dopo m impulsi di clock anziché dopo 1;

basta sostituire lo stato B con la sequenza (B1 , B2 , ...Bm ).

La rete di Figura 4.42 è stata ottenuta adottando un metodo formale per la sua sintesi. Molto spesso

il progettista logico usa tecniche e trucchi che gli consentono di arrivare a una soluzione senza passare

attraverso tutti i passi del procedimento rigoroso. Nella rete di Figura 4.43, ottenuta con ragionamenti

di carattere intuitivo, il segnale X viene usato come ingresso di clock al primo flip-flop D (i flip-flop

commutano sui fronti di discesa).

X

y1 y2

00

01

11

10

y1′ y2′

0

01

11

10

10

X

1

00

11

00

00

y1 y2

00

01

11

10

0

0

1

1

1

X

1

0

1

0

0

y1′

y1 y2

00

01

11

10

0

1

1

0

0

y1 y2

00

01

11

10

1

0

1

0

0

y2′

0

0

1

0

WAIT

Figura 4.41 Tabella delle transizioni e mappe di Karnaugh per y1′ e y2′ e per l’uscita WAIT.

Figura 4.42 Generatore di WAIT attraverso una rete sintetizzata col metodo formale.

Figura 4.43 Generazione del WAIT con una rete costruita con metodo intuitivo.

Assumiamo che tutti i flip-flop della rete di Figura 4.43 siano in stato basso. La situazione non varia

fintantoché X=1. Quando X commutata da 1 a 0 causa la variazione da 0 a 1 dell’uscita del primo FF

(l’ingresso D di questo flip-flop è posto permanentemente a 1). Al prossimo impulso di clock la stessa

variazione si propaga in uscita al secondo flip-flop e, contemporaneamente, l’uscita del primo va a 0 per

a causa di CL asserito.2 Dopo un altro impulso di clock anche l’uscita dell’ultimo FF, cioè WAIT, passa

a 1 e vi resta solo per un periodo di clock perché l’uscita del secondo FF è intanto tornata a 0.

Si noti che la rete di Figura 4.43 riconosce comunque il passaggio basso di X, mentre la rete di

Figura 4.42 richiede che X debba essere mantenuto basso almeno fino al fronte del clock che lo campiona.

2

Si assume che in presenza di CL asserito il clock non abbia effetto.

20

![Presentazione Clock [modalità compatibilità]](http://s1.studylibit.com/store/data/003543129_1-d679fb4379e8cadb2a904da83b8d5b1a-300x300.png)