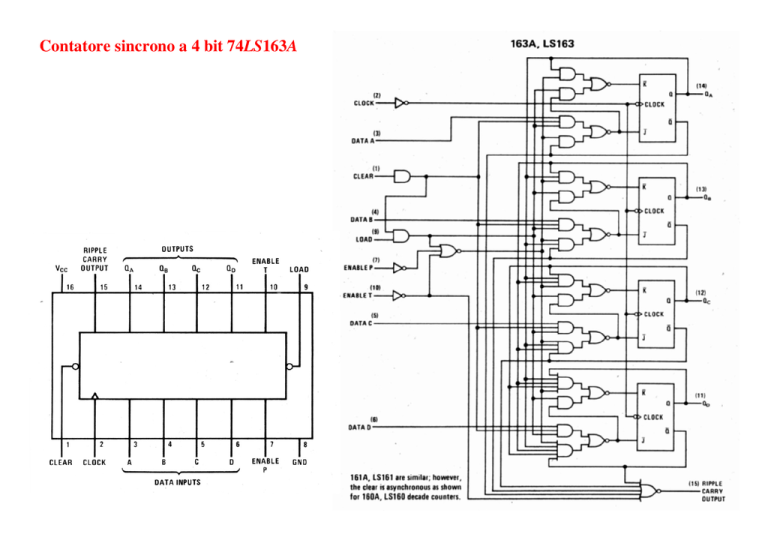

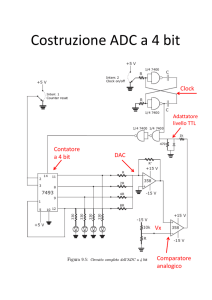

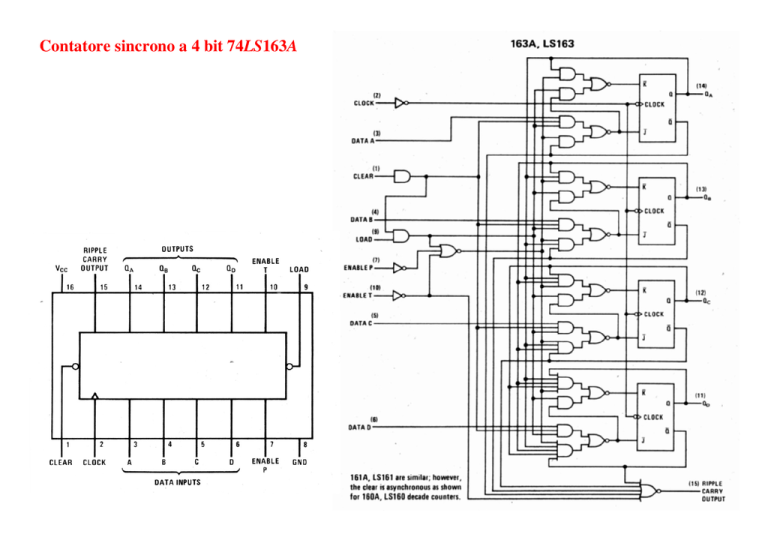

Contatore sincrono a 4 bit 74LS163A Contatore 74LS163A SSI Small Scale Integration (~ 10)

MSI Medium Scale Integration (~ 100)

LSI Large Scale Integration (~ 1k)

VLSI Very Large Scale Integration (~ 10k)

. . . . . . . . Contatore 74LS163A schema base di un contatore modulo N

+5

Contatore modulo N

Quando le uscite Q sono tutte 1 diventa 1 anche l'uscita RC (riporto) mentre l'ingresso LD (load) diventa 0, predisponendo per il caricamento dei dati.

Al successivo fronte di salita del clock viene caricato il dato presente agli ingressi A B C D (1100) ed RC torna a zero.

+5

16

9

+5 RC QA QB QC QD ET LD

CL Ck

logica positiva

logica negativa

A

74LS163A

B

C

D EP

1

1100

1101

1110

1111

1100

1101

12 (3)

13 (2)

14 (1)

15 (0)

12 (3)

13 (2)

8

+5

clock

CL

1

0

QA

1

0

QB

1

0

QC

1

0

QD

1

0

RC

1

0

LD

1

0

G

+5

0

1

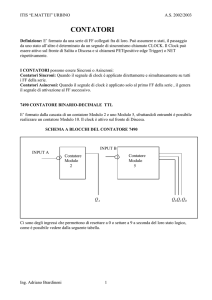

Un contatore modulo N conta ciclicamente gli impulsi al suo ingresso (clock) da 0 a N­1:

0 1 2 . . . N ­ 2 N ­ 1 0 1 . . . e fornisce all'uscita un impulso ogni N impulsi di ingresso (divisore di frequenza per N).

Visualizzazione dei dati

Si possono utilizzare diodi led (light emitting diode) per visualizzare lo stato logico dei segnali del circuito.

I diodi led (rossi) a base di semiconduttori composti (areniuro di gallio) hanno una tensione di polarizzazione diretta VD ≃ 1.5 V.

+5

1 2 4 8

Una porta della serie TTL­LS puo' erogare (assorbire – sink) nello stato basso una corrente IL = 8 mA a VOL = 16

0.4 V.

Con R = 470 si ha nel led una corrente:

ID = (5 – 1.5 ­ 0.4) V / 470 = 6.6 mA

Il led viene pilotato con logica negativa: acceso per indicare lo stato Low (0).

Non e' possibile accendere un led con una porta TTL nello stato alto in quanto IOH load

conteggio

9

+5 RC QA QB QC QD ET LD

CL Ck

+5

A

74LS163A

B

C

D

1

IL

470

segnale di clock

= 800 A.

Stato alto (> 2.4 V): led spento

Stato basso (< 0.4 V): led acceso

Circuito di pilotaggio di un diodo led

EP

G

8

1

RC

Gli ingressi enable EP ed ET non sono utilizzati e sono ~clock

in posizione sempre attivi.

2

LD

L'ingresso clear CL non e' utilizzato ed e' in posizione 4

inattivo.

3

+5

Il segnale di riporto RC viene combinato con il segnale clock per ridurre la durata del segnale load LD al solo 4

5

5

3

8

+5

9

+5

16

9

+5 RC QA QB QC QD ET LD

2

CL Ck

La porta NAND all'ingresso serve solo a ridurre il fan­in

del circuito (circuito buffer).

1

~clock

10

+5

La lunghezza del conteggio viene programmata mediante ponticelli. In logica negativa: ponticello inserito = 1; il valore impostato indica l'inizio del conteggio, decrescente fino a zero; i led (a logica negativa) riportano il conteggio in discesa.

(1 ≤ N ≤ 16) ~clock

6 x 470

mezzo ciclo low del clock.

Contatore modulo N

6

A

74LS163A

B

C

D

1

1

EP

1

5

3

8

+5

+5

clock

1 2 4 8

2

0

+5

+

G

10 F

+5

4

Caratteristiche elettriche del 74LS163A

Tempi di commutazione del 74LS163A

Tempi di commutazione del 74LS163A

4

Contatore

programmabile

+

modulo N

6

74HC00

10

5

8

+

9

6 x 470

(1 ≤ N ≤ 16) +

+

16

9

+5 RC QA QB QC QD ET LD

CL Ck

74HC00

1

~clock

A

B

C

D

EP

1

1

2

4

8

+

+

+

+

2

+

G

8

+

3

0

+5

74HC163A

10 F

+

+

a

k

diodi led

k

6 x

470

+

10 F

Vista dal lato dei componenti

condensatore elettrolitico

xyz

+

a

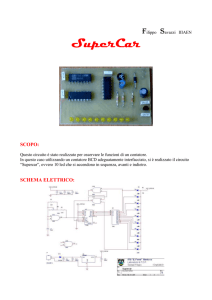

Contatore programmabile modulo N (1 ≤ N ≤ 16) 4

+

6

74HC00

10

5

Collegare un generatore all'ingresso ~clock;

8

●

regolare per una frequenza bassa (< 10 Hz) e verificare che la sequenza di conteggio sia corretta, per diversi valori di N.

●

Aumentare la frequenza di clock e misurare (con l'oscilloscopio) i ritardi tra l'ingresso Ck e +

9

6 x 470

+

+

16

le uscite Q ed RC ed il tempo di propagazione 9

+5 RC QA QB QC QD ET LD

CL Ck

74HC00

1

~clock

A

B

C

D

EP

1

1

2

4

8

+

+

+

+

2

+

G

8

+

3

0

+5

74HC163A

10 F

+

+

attraverso le porte NAND.

●

Aumentare ancora la frequenza e determinare (se possibile) la frequenza massima di conteggio.