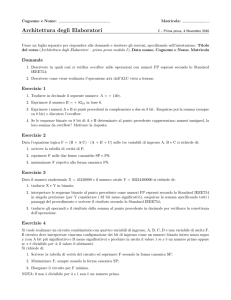

Riepilogo Attività Registro del Professore

Classe: 4G PROFESSIONALE

Anno: 2015/2016

DocentI: DAMIANI NICOLA, MAMMI MARINO

Materia:TECNOLOGIE ELETTRICO ELETTRONICHE E APPLICAZIONI

Sistemi di numerazione in base 2, 8,10 e 16, conversione numerica da un sistema numerico a un altro, complemento a uno e

complemento a due di un numero binario, numeri binari a 8 bit dotati di segno,

Addizione binaria, numeri binari dotati di segno.

Circuiti combinatori, tabelle della verità delle porte logiche elementari AND, OR, NOT, NAND E NOR e relativi simboli logici.

Verifica sperimentale della tabella della verità di una funzione logica combinatoria mediante sistema AOI con ausilio di breadboard.

Teoremi e postulati dell'algebra di Boole; Sistemi universali di porte logiche: AOI, NAND e NOR.

Prima e seconda forma canonica, Teorema dell'adiacenza e sue applicazioni.

Laboratorio Hardware: Verifica sperimentale della universalità della porta NAND.

Teorema di De Morgan e sue applicazioni.

Mappe di Karnough: minimizzazione di una funzione logica, criteri di minimizzazione.

Decoder binario decimale 2 a 4, decoder binario decimale 3 a 8, decoder per generare funzioni, condizioni don't care. Encoder

decimale binario 4 a 2, Multiplexer, multiplexer 4 a 1: tabella della verità e circuito logico, funzioni con multiplexer 4 a 1 e multiplexer

8 a 1.

Porte logiche XOR e XNOR, Half adder e full adder.

Decoder drive BCD 7 segmenti.

Laboratorio hardware: decoder binario decimale 2 a 4

Laboratorio hardware: verifica sperimentale multiplexer per generare funzioni.

Latch SR a porte NAND e a porte NOR, analisi del circuito, tabella della verità, possibile applicazione: debouncer, diagrammi

temporali di un Latch SR, Latch SR con ENABLE, circuito logico e true table, diagramma temporali, latch SR

con ENBLE; latch di tipo D, circuito logico e true table, diagramma temporali.

Laboratorio hardware: verifica sperimentale di un latch SR.

Differenza tra dispositivo sincrono e asincrono, differenza tra dispositivo logico combinatorio e dispositivo sequenziale, Flip Flop SR

con PRESET e CLEAR, diagrammi temporali, FF - JK e FF - T tabella della verità è diagrammi temporali.

Il materiale presente in questa dispensa intende affiancare e non sostituire gli appunti e le schede esercitative delle

lezioni svolte durante l’anno!

TECNOLOGIE ELETTRICO ELETTRONICHE E APPLICAZIONI

MATERIALE ESTIVO PER IL RECUPERO DEL DEBITO a.s. 2015/2016

I SEGNALI ANALOGICI: I SEGNALI ANALOGICI SONO SEGNALI CHE VARIANO CON

CONTINUITÀ NEL TEMPO.

I SEGNALI DIGITALI O DISCRETI: I SEGNALI DIGITALI SONO SEGNALI CHE NON VARIANO

CON CONTINUITÀ, MA POSSONO ASSUMERE SOLO UN NUMERO DISCRETO DI VALORI.

SISTEMI NUMERICI

I SISTEMI NUMERICI SONO DEL TIPO POSIZIONALE PESATO, SONO DETTI COSÌ PERCHÉ

OGNI CIFRA ASSUME UN VALORE DIVERSO A SECONDA DELLA SUA POSIZIONE NEL

NUMERO.

SISTEMA DECIMALE

LE CIFRE DI UN NUMERO DECIMALE SONO 0,1,2,3,4,5,6,7,8,9

CIASCUNA CIFRA DEL NUMERO VIENE MOLTIPLICATA PER IL SUO PESO CHE È UNA

POTENZA DEL 10:

LA PRIMA CIFRA A DESTRA VA MOLTIPLICATA PER 100, SPOSTANDOSI A SINISTRA, LA

SECONDA CIFRA VA MOLTIPLICATA PER 101, LA TERZA CIFRA VA MOLTIPLICATA PER 102

E COSÌ VIA.

SISTEMA BINARIO

LE CIFRE DI UN NUMERO BINARIO SONO 0,1

CIASCUNA CIFRA VIENE DETTA BIT DA BINARY DIGIT.

IL VALORE DECIMALE DEL NUMERO È DETERMINATO MOLTIPLICANDO CIASCUNA CIFRA

DEL NUMERO PER IL SUO PESO CHE È UNA POTENZA DEL 2:

LA PRIMA CIFRA A DESTRA VA MOLTIPLICATA PER 20, SPOSTANDOSI A SINISTRA, LA

SECONDA CIFRA VA MOLTIPLICATA PER 21, LA TERZA CIFRA VA MOLTIPLICATA PER 22 E

COSÌ VIA.

UNA NIBBLE È UN GRUPPO DI 4 BIT

UN BYTE È UN GRUPPO DI 8 BIT

UNA WORD È UN GRUPPO DI 32 BIT

UNA DOUBLE WORD È UN GRUPPO DI 64 BIT

SISTEMA OTTALE

LE CIFRE DI UN NUMERO DECIMALE SONO 0,1,2,3,4,5,6,7

IL VALORE DECIMALE DEL NUMERO È DETERMINATO MOLTIPLICANDO CIASCUNA CIFRA

DEL NUMERO PER IL SUO PESO CHE È UNA POTENZA DEL 8:

LA PRIMA CIFRA A DESTRA VA MOLTIPLICATA PER 80, SPOSTANDOSI A SINISTRA, LA

SECONDA CIFRA VA MOLTIPLICATA PER 81, LA TERZA CIFRA VA MOLTIPLICATA PER 82 E

COSÌ VIA.

SISTEMA ESADECIMALE

LE CIFRE DI UN NUMERO DECIMALE SONO 0,1,2,3,4,5,6,7,8,9, A, B, C, D, E, F

IL VALORE DECIMALE DEL NUMERO È DETERMINATO MOLTIPLICANDO CIASCUNA CIFRA

DEL NUMERO PER IL SUO PESO CHE È UNA POTENZA DEL 16:

LA PRIMA CIFRA A DESTRA VA MOLTIPLICATA PER 160, SPOSTANDOSI A SINISTRA, LA

SECONDA CIFRA VA MOLTIPLICATA PER 161, LA TERZA CIFRA VA MOLTIPLICATA PER 162

E COSÌ VIA.

CONVERSIONI DA BASE A BASE

DA QUALSIASI BASE VERSO LA BASE 10: USIAMO IL METODO DEI PESI

1. (10010110001)2

1

(1201)10

0 0 1 0 1 1 0 0 0 1

10

2 29 28 27 26 25 24 23 22 21 20

sotto a ciascun bit posizioniamo il relativo peso, siamo in binario quindi il peso è una

potenza del 2, da destra verso sinistra l'esponente della potenza cresce partendo da 0

mentre la base resta sempre 2, si parte da 20 poi 21 , poi 22 e così via .

(10010110001)2 = 1⋅ 210 + 0 ⋅ 29 + 0 ⋅ 28 + 1 ⋅ 27 + 0 ⋅ 26 + 1 ⋅ 25 + 1⋅ 24 + 0 ⋅ 23 + 0 ⋅ 22 + 0 ⋅ 21 + 1⋅ 20 =

=1024 + 128 + 32 + 16 + 1 = 1201

Infine si fa la somma di ciascun bit per il relativo peso.

2. (111001101110)2

1

1

11

10

(3694)10

1 0 0 1 1 0 1 1 1 0

2 2 29 28 27 26 25 24 23 22 21 20

sotto a ciascun bit posizioniamo il relativo peso, siamo in binario quindi il peso è una

potenza del 2, da destra verso sinistra l'esponente della potenza cresce partendo da 0

mentre la base resta sempre 2, si parte da 20 poi 21 , poi 22 e così via .

(10010110001)2 = 1⋅ 211 + 1⋅ 210 + 1⋅ 29 + 0 ⋅ 28 + 0 ⋅ 27 + 1⋅ 26 + 1⋅ 25 + 0 ⋅ 24 + 1⋅ 23 + 1⋅ 22 + 1⋅ 21 + 0 ⋅ 20 =

=2048+1024 + 512 + 64 + 32 + 8 + 4 + 2 = 3694

Infine si fa la somma di ciascun bit per il relativo peso.

3. (573)8

(379)10

5 7 3

82 81 80

sotto a ciascuna cifra ottale mettiamo il relativo peso, siamo in ottale quindi il peso è una potenza del 8

da destra verso sinistra la potenza cresce partendo da 80 .

( 573)8 = 5 ⋅ 82 + 7 ⋅ 81 + 3 ⋅ 80 = 5 ⋅ 64 + 7 ⋅ 8 + 3 ⋅1 = 320 + 56 + 3 = 379

Infine si fa la somma di ciascuna cifra ottale per il relativo peso.

4. (FFF1)16

(65521)10

F F F 1

163 162 161 160

sotto a ciascuna cifra esadecimale posizioniamo il relativo peso, siamo in esadecimale quindi il peso

è una potenza del 16, da destra verso sinistra l'esponente della potenza cresce partendo da 0

mentre la base resta sempre 16, si parte da 160 poi 161 , poi 16 2 e così via .

( FFF1)16 = 15 ⋅163 + 15 ⋅162 + 15 ⋅161 + 1⋅160 = 15 ⋅ 4096 + 15 ⋅ 256 + 15 ⋅16 + 1 = 61440 + 3840 + 240 + 1 = 65521

Infine per determinare il numero decimale si fa la somma di ciascuna cifra esadecimale per il

relativo peso.

5. (A062)16

(41058)10

A 0 6 2

163 162 161 160

sotto a ciascuna cifra esadecimale posizioniamo il relativo peso, siamo in esadecimale quindi il

peso è una potenza del 16, da destra verso sinistra l'esponente della potenza cresce partendo da 0

mentre la base resta sempre 16, si parte da 160 poi 161 , poi 162 e così via.

( A062 )16 = 10 ⋅163 + 0 ⋅162 + 6 ⋅161 + 2 ⋅160 = 10 ⋅ 4096 + 6 ⋅16 + 2 ⋅1 = 40960 + 96 + 2 = 41058

Infine per determinare il numero decimale si fa la somma di ciascuna cifra esadecimale per il

relativo peso.

6. (110111, 10001)2

(55,53125)10

1 1 0 1 1 1 ,

1

4

3

2

1

0

−1

0

0

0

−2

−3

−4

1

2 2 2 2 2 2

2 2 2 2 2 −5

sotto a ciascuna cifra binaria posizioniamo il relativo peso, siamo in binario quindi il peso

5

è una potenza del 2, da destra verso sinistra partendo dalla virgola l'esponente della potenza

cresce partendo da 0 mentre la base resta sempre 2, si parte da 20 poi 21 , poi 22 e così via;

a destra della virgola l'esponente della potenza decresce partendo da -1 mentre la base resta

sempre 2, si parte da 2−1 , poi 2−2 , poi 2−3 e così via.

(110111,10001)2 = 1 ⋅ 25 + 1 ⋅ 24 + 0 ⋅ 23 + 1 ⋅ 22 + 1⋅ 21 + 1⋅ 20 + 1⋅ 2−1 + 0 ⋅ 2−2 + 0 ⋅ 2−3 + 0 ⋅ 2−4 + 1⋅ 2−5 =

=32 + 16 + 4 + 2 + 1 + 0,5 + 0, 03125 = 55, 53125

Infine per determinare il numero decimale si fa la somma di ciascuna cifra binaria per il

relativo peso.

DALLA BASE 8 ALLA BASE 16 E VICEVERSA, DALLA BASE 2 ALLE BASI 8

VICEVERSA SI USA IL METODO DEI GRUPPI

7. (736,23)8

E 16 E

(1DE,4E)16

7

3

6

,

2

3

ciascuna cifra ottale si decomprime in gruppi di 3 bit

⟨1 1 1⟩ ⟨ 0 1 1⟩ ⟨1 1 0⟩ , ⟨ 0 1 0⟩ ⟨ 0 1 1⟩

si raggruppano i bit a quattro a quattro partendo dalla virgola,

in testa e in coda si aggiungono gli zeri

⟨ 0 0 0 1⟩ ⟨1 1 0 1⟩ ⟨1 1 1 0⟩ , ⟨ 0 1 0 0⟩ ⟨1 1 0 0⟩

1

D

E

,

4

C

8. (AD,BC)16

(255,57)8

A

D

,

B

C

ciascuna cifra esadecimale si decomprime in gruppi di 4 bit

⟨1 0 1 0⟩ ⟨1 1 0 1⟩ , ⟨1 0 1 1⟩ ⟨1 1 0 0⟩

si raggruppano i bit a tre a tre partendo dalla virgola,

in testa e in coda si aggiungono gli zeri

⟨ 0 1 0⟩ ⟨1 0 1⟩ ⟨1 0 1⟩ , ⟨1 0 1⟩ ⟨1 1 1⟩ ⟨ 0 0 0⟩

2

5

5 ,

5

7

0

(524,26)8

9. (101010110,01011)2

101010110, 01011

si raggruppano i bit a tre a tre partendo dalla virgola,

in testa e in coda si aggiungono gli zeri

⟨1 0 1⟩ ⟨ 0 1 0⟩ ⟨1 1 0⟩ , ⟨ 0 1 0⟩ ⟨1 1 0⟩

5

2

4

,

2

6

DALLA BASE 10 VERSO QUALSIASI ALTRA BASE SI USA IL METODO DELLE DIVISIONI

RIPETUTE PER LA BASE DI ARRIVO

10. (46)10

(101110)2

Q

46 ÷ 2 = 23

23 ÷ 2 = 11

11 ÷ 2 = 5

R

0 ← LSB

1

1

5÷2= 2

2÷2=1

1÷2=0

1

0

1 ← MSB

Q = QUOZIENTE DELLADIVISIONE

R = RESTO DELLA DIVISIONE

LSB = LEAST SIGNIFICATIVE BIT

MSB = MOST SIGNIFICATIVE BIT

Il numero nella nuova base di arrivo sarà costituito dai resti della divisione, dal MSB (ultimo resto)

al LSB (primo resto della divisione), quindi:

(46)10 = (101110)2

11. (3956,8)10

(7564,6314)8

Dalla base 10 verso qualsiasi altra base si usa il metodo delle divisioni ripetute per la base di

arrivo per la parte intera del numero

Q

R

3956 ÷ 8 = 494

494 ÷ 8 = 61

4 ← LSB

6

61 ÷ 8 = 7

7÷8= 0

5

7 ← MSB

Il numero nella nuova base di arrivo sarà costituito dai resti della divisione, dal MSB (ultimo resto)

al LSB (primo resto della divisione) per la parte intera

0,8×8 = 6 ,4

0,4×8 = 3 ,2

0, 2×8 = 1 , 6

0,6×8 = 4 ,8

Per la parte frazionaria applicando il metodo delle moltiplicazioni ripetute ed arrestando lo sviluppo

alla quarta cifra dopo la virgola

12. (3956,6)10

(F74,C)16

Dalla base 10 verso qualsiasi altra base si usa il metodo delle divisioni ripetute per la base di

arrivo per la parte intera del numero

Q

R

3956 ÷ 16 = 247

4 ← LSB

247 ÷ 16 = 15

7

15 ÷ 16 = 0

(F) 15 ← MSB

Il numero nella nuova base di arrivo sarà costituito dai resti della divisione, dal MSB (ultimo resto)

al LSB (primo resto della divisione) per la parte intera;

0,8×16 = 12 ,8

C

Per la parte frazionaria applicando il metodo delle moltiplicazioni ripetute.

OPERAZIONI ARITMETICHE NEL SISTEMA BINARIO

ADDIZIONE BINARIA

0+

0

=

0

0+

1

=

1

1+

0

=

1

1+

1

=

10

somma

Riporto(carry)

NUMERI BINARI CON SEGNO

DEFINIZIONE: IL COMPLEMENTO A UNO DI UN NUMERO BINARIO (N)2 PUÒ ESSERE

OTTENUTO COMPLEMENTANDO LE SINGOLE CIFRE DEL NUMERO BINARIO STESSO, CIOÈ

SOSTITUENDO OGNI 0 CON 1 E OGNI 1 CON 0.

SUPPONIAMO DI AVERE IL SEGUENTE NUMERO BINARIO: (N)2=(10110011)2 RICAVIAMO

ORA IL COMPLEMENTO A 1:

1 0 1 1 0 0 1 1

↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓

0 1 0 0 1 1 0 0

QUINDI IL COMPLEMENTO A 1 DEL NUMERO BINARIO (N)2=(10110011)2 È (N)C1=(01001100)2

ES: DATO IL NUMERO BINARIO A OTTO BIT (N)2 =(10011100)2, DETERMINARNE LA

NOTAZIONE IN COMPLEMENTO A 1.

RISULTA:

( N )2

= (1 0 1 1 0 0 1 1)

↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓

( N )C1 = (0

1 0 0 1 1 0 0)

NOTAZIONE IN COMPLEMENTO A 2

PER CONVERTIRE IL NUMERO BINARIO (N)2 NELLA NOTAZIONE IN COMPLEMENTO A 2:

• Si determina (N)C1, complemento a uno di (N)2;

• Si aggiunge 1 al complemento a uno: (N)C2=(N)C1 + 1.

LA NOTAZIONE IN COMPLEMENTO A 2 CONSENTE LA RAPPRESENTAZIONE DI NUMERI

CON SEGNO.

• I numeri positivi sono rappresentati come nel sistema binario, ed hanno uno 0 come cifra più

significativa (MSB);

• I numeri negativi sono rappresentati nella forma di complemento a 2 dei corrispondenti numeri

positivi, ed hanno un 1 come cifra più significativa.

RICORDA CHE IN UN NUMERO BINARIO IL MSB (MOST SIGNIFICATIVE BIT) È IL PRIMO BIT

A SINISTRA MENTRE IL LSB (LEAST SIGNIFICATIVE BIT) È IL PRIMO BIT A PARTIRE DA

DESTRA

MSB

1011010101010110

LSB

ES: Convertire il decimale -127 in complemento a due.

127 2

63 2

LSB → 1 31 2

1 15 2

1

72

1 32

1 12

1 0

1 ← MSB

Quindi (+127)10 = (01111111)2

Determiniamo infine prima il complemento a 1 e poi il complemento a 2

(N)2= (+127)10= (01111111)2

(N)C1 = (10000000)2

(N)C2 = (-127)10 = (10000001)2.

ES: Convertire il decimale - 96 in complemento a due con n=8 bit.

96 2

48 2

LSB → 0

24 2

0

12 2

0

62

0

32

0

12

1 0

1 ← MSB

Quindi (+96)10 = (01100000)2 aggiungiamo uno 0 in testa per avere un numero di 8 bit che sia

positivo.

Determiniamo infine prima il complemento a 1 e poi il complemento a 2

(N)2= +(96)10=(01100000)2

(N)C1 = (10011111)2

(N)C2 = (- 96)10 = (10100000)2.

OPERAZIONI CON NUMERI DOTATI DI SEGNO CON NUMERI A 8 BIT

(+127)10 –( 96)10 = (+127)10 + (-96)10 = (+31)10

1 11

01111111+

10100000=

1 00011111

Il primo bit a sinistra (il nono bit) va scartato quindi il numero è (00011111)2=(+31)10 , l’ottavo bit (il

primo bit a sinistra ) vale 0 per cui il numero è positivo.

Proviamo ora a fare la seguente operazione:

(+96)10 –(+ 127)10 = (+ 96)10 + (-127)10 = (-31)10

01100000+

10000001=

11100001

Il numero ottenuto è negativo perché il primo bit è 1, per cui il numero è espresso come

complemento a 2

(N)C2=(11100001)

(N)C1=(00011110)

(00011110)+

1=

(00011111)=(+31)

PORTE LOGICHE ELEMENTARI

TABELLA DELLA VERITA’

PORTA NOT

A

Y =A

A

A

0

1

1

0

TABELLA DELLA VERITA’

PORTA AND

A

B

Y = A⋅ B

0

0

0

0

1

0

1

0

0

1

1

1

TABELLA DELLA VERITA’

PORTA OR

A

B

Y=A+B

0

0

0

0

1

1

1

0

1

1

1

1

TABELLA DELLA VERITA’

PORTA NAND

A

B

Y = A⋅B

A

B

Y=A ⋅ B

PORTA NOR

A

B

Y= A+B

PORTA XOR

0

0

1

0

1

1

1

0

1

1

1

0

TABELLA DELLA VERITA’

A

Y = A⊕B

Y = A+B

0

0

1

0

1

0

1

0

0

1

1

0

TABELLA DELLA VERITA’

A

PORTA XNOR

B

B

Y = A⊕B

0

0

0

0

1

1

1

0

1

1

1

0

TABELLA DELLA VERITA’

A

B

Y = A⊕B

0

0

1

1

0

1

0

1

1

0

0

1

MINTERMINI E MAXTERMINI

MINTERMINE: PRODOTTI CHE CONTENGONO TUTTE LE VARIABILI DI INGRESSO DI UNA

FUNZIONE BOOLEANA; OGNI MINTERMINE SI COSTRUISCE FACENDO IL PRODOTTO

DELLE VARIABILI, NEGATE SE ALLA VARIABILE CORRISPONDE UNO 0, NON NEGATE SE

ALLA VARIABILE CORRISPONDE UN 1.

I MINTERMINI SONO COSÌ DETTI IN QUANTO PER UNA DATA COMBINAZIONE DI VALORI

DELLE VARIABILI DI INGRESSO IL MINIMO NUMERO DI TERMINI PRODOTTO È UGUALE AD

1.

MAXTERMINE: SOMME CHE CONTENGONO TUTTE LE VARIABILI DI INGRESSO DI UNA

FUNZIONE BOOLEANA; OGNI MAXTERMINE SI COSTRUISCE FACENDO LA SOMMA DELLE

VARIABILI, NEGATE SE ALLA VARIABILE CORRISPONDE UN 1, NON NEGATE SE ALLA

VARIABILE CORRISPONDE UNO 0.

I MAXTERMINI SONO COSÌ DETTI IN QUANTO PER UNA DATA COMBINAZIONE DI VALORI

DELLE VARIABILI DI INGRESSO È MASSIMO IL NUMERO DI TERMINI SOMMA UGUALE AD

1.

FORME CANONICHE

NELLA FORMA CANONICA SOMMA DI PRODOTTI INDICATA ANCHE CON SOP (SUM OF

PRODUCT), LA FUNZIONE BOOLEANA È ESPRESSA COME SOMMA DEI MINTERMINI, PER

CUI LA FUNZIONE VALE 1.

NELLA FORMA CANONICA PRODOTTI DI SOMME INDICATA ANCHE CON POS (PRODUCT

OF SUM), LA FUNZIONE BOOLEANA È ESPRESSA COME PRODOTTO DEI MAXTERMINI,

PER CUI LA FUNZIONE VALE 0.

Esempio 1: Data la seguente funzione logica:

F = A⋅ B ⋅ C ⋅ D + A⋅ B ⋅C ⋅ D + A⋅ B ⋅C ⋅ D

a) Scrivere la tabella della verità

b) Disegnare il circuito logico combinatorio

Svolgimento

La tabella della verità si può costruire in due modi in questo caso, il primo modo è quello dell’analisi

della funzione e cioè il seguente:

A B C D A B C D A⋅ B ⋅C ⋅ D A ⋅ B ⋅C ⋅ D A ⋅ B ⋅C⋅ D F

0 0 0 0 1 1 1 1

0

0

0

0

0 0 0 1 1 1 1 0

0

0

1

1

0 0 1 0 1 1 0 1

0

0

0

0

0 0 1 1 1 1 0 0

0

0

0

0

0 1 0 0 1 0 1 1

0

0

0

0

0 1 0 1 1 0 1 0

0

0

0

0

0 1 1 0 1 0 0 1

0

1

0

1

0 1 1 1 1 0 0 0

0

0

0

0

1 0 0 0 0 1 1 1

0

0

0

0

1 0 0 1 0 1 1 0

0

0

0

0

1 0 1 0 0 1 0 1

1

0

0

1

1 0 1 1 0 1 0 0

0

0

0

0

1 1 0 0 0 0 1 1

0

0

0

0

1 1 0 1 0 0 1 0

0

0

0

0

1 1 1 0 0 0 0 1

0

0

0

0

1 1 1 1 0 0 0 0

0

0

0

0

Il secondo modo molto più rapido è quello di sfruttare la teoria dei mintermini, essendo la funzione

espressa con la prima forma canonica allora basta mettere in uscita gli 1 della funzione in

corrispondenza della combinazione dei mintermini che costituiscono la funzione.

A

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

mi

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

F

0

1

0

0

0

0

1

0

0

0

1

0

0

0

0

0

Esempio 2: Data la funzione Y espressa dalla seguente tabella della verità:

A

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

mi

Mi

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A⋅ B ⋅C ⋅ D

A+ B +C + D

A+ B+C + D

A+ B+C + D

A+ B+C + D

A+ B+C + D

A+ B+C + D

A+ B+C + D

A+ B+C + D

A+ B+C + D

A+ B+C + D

A+ B+C + D

A+ B+C + D

A+ B+C + D

A+ B+C + D

A+ B+C + D

A+ B+C + D

Y

1

1

1

0

1

1

0

1

1

1

0

1

1

0

1

1

F

0

1

0

0

0

0

1

0

0

0

1

0

0

0

0

0

a) Determinare la funzione Y con la seconda forma canonica e disegnarne il circuito logico

combinatorio.

b) Determinare la funzione F con la prima forma canonica e disegnarne il circuito logico

combinatorio.

Svolgimento

Per la seconda forma canonica dobbiamo guardare gli 0 della funzione di uscita, in corrispondenza

degli 0 consideriamo i maxtermini e infine scrivere la seconda forma canonica come prodotto di quei

maxtermini per i quali la funzione vale 0. Risulterà:

Y = ( A + B + C + D ) ⋅ ( A + B + C + D) ⋅ ( A + B + C + D ) ⋅ ( A + B + C + D)

Per la prima forma canonica dobbiamo guardare gli 1 della funzione di uscita, in corrispondenza

degli 1 consideriamo i mintermini e infine scrivere la prima forma canonica come somma di quei

mintermini per i quali la funzione vale 1. Risulterà:

F = A⋅ B ⋅C ⋅ D + A⋅ B ⋅C ⋅ D + A⋅ B ⋅C ⋅ D

POSTULATI, PROPRIETÀ E TEOREMI NELL’ALGEBRA DI BOOLE

POSTULATI

Elenchiamo i postulati sui quali si costruisce l’algebra di Boole:

1. Una variabile booleana A può assumere solo due valori: A = 0 oppure A = 1;

2. 0∙0 = 0;

3. 1∙1 = 1

4. 1∙0 = 0∙1 = 0

5. 0 + 0 = 0;

6. 1 + 1 = 1;

7. 1 + 0 = 0 + 1 = 1;

8. 1 = 0 e 0 = 1 .

I precedenti postulati sono facilmente verificabili con le definizioni delle operazioni logiche viste

prima.

PROPRIETÀ

1. Commutativa: A + B = B + A e A∙B = B∙A;

2. Associativa: A+B+C = (A+B)+C = A+(B+C) e A∙B∙C = (A∙B)∙C = A∙(B∙C)

3. Distributiva dell’AND sull’OR: A∙(B + C) = A∙B + A∙C;

4. Distributiva dell’OR sull’AND: A + (B∙C) = (A + B)∙(A + C);

5. Idempotenza: A + A = A e A∙A = A;

6. Involuzione: A = A ;

7. Applicazione: A + A∙B = A e A∙(A + B) = A;

8. Identità: 0 + A = 1∙A = A;

9. Dominanza: 1 + A = 1 e 0∙A = 0;

10. Complementazione: A + A = 1 e A ⋅ A = 0

11. Assorbimento: A + A ∙B = A + B e A∙(A + B) = A∙B

TEOREMA DI DE MORGAN

Il teorema di De Morgan è di fondamentale importanza sia nell’algebra di Boole sia nella sua

applicazione ai circuiti elettronici digitali.

Il teorema di De Morgan è enunciato dalle seguenti due espressioni:

A + B = A⋅ B

A⋅ B = A + B

Queste espressioni sono riferite a sole due variabili, ma si possono generalizzare a più variabili

come segue:

A + B + C = A⋅ B ⋅C

A⋅ B ⋅C = A + B + C

Il teorema di De Morgan è di fondamentale importanza in quanto, in parole, enuncia il fatto che ogni

funzione booleana può essere espressa in termini delle sole operazioni AND e NOT oppure delle

sole OR e NOT.

Minimizzazione booleana tramite Mappe di Karnaugh

Tra le proprietà dell’algebra di Boole, le seguenti consentono di semplificare notevolmente le

espressioni booleane:

(

A⋅ B + A⋅ B = A⋅ B + B

)

(

= A

)

A⋅ B ⋅C + B ⋅C + B ⋅C + B ⋅C = A

Le mappe di Karnaugh sono una particolare forma di tabella di verità, che consente di individuare

immediatamente la possibilità di fare queste semplificazioni.

Ad esempio, la seguente tabella di verità della funzione Y = Y(A,B,C)

A

B

C

Y

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

0

1

0

1

1

1

Può essere ridisegnata così:

Dalla tabella di verità o dalla mappa di Karnaugh è immediato ottenere l’espressione booleana della

funzione Y come “somma” di “prodotti”, cioè come OR di tanti termini AND quante sono le caselle

in cui la funzione vale 1; ciascuno di questi termini AND (detti mintermini) è costituito dall’AND delle

variabili di ingresso, negate oppure no a seconda che il valore della variabile associato a quella

casella sia 0 oppure 1.

Y = A⋅ B ⋅C + A⋅ B ⋅C + A⋅ B ⋅C + A⋅ B ⋅C

Nel caso di funzioni di 4 variabili, ad es. Z=Z(A,B,C,D), la mappa di Karnaugh ha 4 righe e quattro

colonne:

Mappa di Karnaugh della funzione Z

Nelle mappe di Karnaugh i valori della funzione Z sono scritti dentro le caselle.

I valori delle variabili A, B, C, D sono indicati come “coordinate” delle caselle. Esaminando queste

“coordinate, si constata che le coppie di valori di A e B (di C e D) associate alle colonne (alle righe)

sono ordinate in modo che tra due caselle adiacenti (della medesima riga o della medesima colonna)

cambia il valore di una sola delle variabili, mentre quello di tutte le altre rimane lo stesso; questa

proprietà vale anche tra le caselle estreme di ciascuna riga e di ciascuna colonna (che, sotto questo

aspetto, possono quindi essere considerate “adiacenti”, in senso circolare).

Si osserva che, in virtù di questo fatto, a ciascuna coppia di caselle adiacenti contrassegnate con il

valore 1 corrispondono, nella espressione booleana, due termini “prodotto” (mintermini) nei quali

una variabile è presente negata in una e non negata nell’altra, mentre tutte le altre variabili hanno

lo stesso valore. E` allora possibile semplificare l’espressione sostituendo quei due termini con un

unico termine nel quale non è più presente la variabile che cambia valore. Ad esempio le ultime

due caselle della seconda riga nella mappa della funzione Y portano alla seguente semplificazione:

A⋅ B ⋅C + A⋅ B ⋅C = A⋅C

Allo stesso modo, quaterne di caselle adiacenti tutte con il valore 1 (sulla stessa riga o sulla stessa

colonna) corrispondono a quattro termini che si riducono ad uno; ad esempio le quattro caselle della

terza riga nella mappa della funzione Z portano alla seguente semplificazione:

C ⋅ D ⋅ ( A⋅B + A ⋅ B + A ⋅ B + A ⋅ B) = C ⋅ D

le quattro caselle della terza colonna nella mappa della funzione Z portano alla seguente

semplificazione:

A ⋅ B ⋅ (C ⋅ D + C ⋅ D + C ⋅ D + C ⋅ D) = A ⋅ B

Così pure quaterne adiacenti disposte secondo un quadrato producono un unico termine; ad

esempio le quattro caselle in basso a sinistra nella mappa della funzione Z portano alla seguente

semplificazione:

A ⋅ C ⋅ ( B ⋅ D + B ⋅ D + B ⋅ D + B ⋅ D) = A ⋅ C

Analogo discorso vale per gruppi di otto caselle adiacenti tutte con il valore 1.

Per semplificare l’espressione booleana di una funzione, si tratta dunque di individuare, nella

relativa mappa di Karnaugh, i gruppi di (2 o 4 o 8) caselle adiacenti con il valore 1.

Nel far ciò conviene tenere presente la proprietà A+A=A, che consente di utilizzare più volte la

stessa casella (ovvero più volte lo stesso mintermine nell’espressione booleana), per formare

gruppi diversi, al fine di operare il maggior numero di semplificazioni possibile.

Individuando un insieme di gruppi (da 1, 2, 4 o 8) che copre tutte le caselle in cui compare il valore

1, si ottiene una espressione semplificata, costituita dall’OR dei termini corrispondenti a ciascun

gruppo.

Si devono creare gruppi o raggruppamenti degli 1 che si trovano in celle adiacenti rispettando le

seguenti regole:

1) I raggruppamenti si effettuano per rettangoli o quadrati per un numero di celle pari ad una

potenza del 2: 1,2,4,8,16... .

2) I raggruppamenti devono comprendere il maggior numero di celle possibili nel rispetto della

regola 1).

3) Una o più celle possono appartenere a più raggruppamenti.

4) I raggruppamenti devono ricoprire tutte le celle contenenti un 1; in altre parole, ogni cella con

un 1 deve far parte di un raggruppamento, che al limite può essere costituito da una sola cella.

5) Ad ogni raggruppamento corrisponde un prodotto delle variabili d'entrata così strutturato: il

prodotto comprende solo quelle variabili che nel raggruppamento in esame non cambiano di

stato, complementando quelle che sono allo stato 0. La funzione logica semplificata è data

dalla somma dei questi prodotti generati dai raggruppamenti.

Riprendendo l’esempio della funzione Z, si possono individuare i gruppi segnati in figura:

AB

CD

00

01

11

10

1

00

01

1

11

1

10

1

1

1

1

1

1

1

1

Con questi raggruppamenti si ottiene, immediatamente, l’espressione semplificata di Z:

Z = A⋅C + A⋅ B + B ⋅ D

Nell’esempio si può osservare che si sono considerate adiacenti anche le caselle estreme delle

righe o delle colonne.

Si osserva che si possono individuare diversi raggruppamenti che coprono tutte le caselle in cui Z

vale 1, ciascuno dei quali porta a diverse espressioni di Z equivalenti (più o meno semplificate).

Esempio:

Esempio:

Esempio:

ESEMPIO:

CONDIZIONI DON’T CARE

Una funzione booleana si dice parzialmente definita se il suo valore è specificato solo per alcune

combinazioni dei valori delle variabili.

Nella pratica si ha a che fare con funzioni booleane parzialmente definite in due casi: o quando le

altre combinazioni dei valori delle variabili non si possono verificare mai, oppure quando, anche se

si verificano, i corrispondenti valori della funzione non importano (possono essere indifferentemente

0 od 1, perché comunque non vengono usati).

Nella tabella di verità (o nella mappa di Karnaugh) di una funzione parzialmente definita, i valori non

specificati sono comunemente indicati con una ics e corrispondono a ciò che si chiama “condizioni

di indifferenza”, ovvero don’t care conditions (d.c.c.).

La presenza delle condizioni don’t care nelle caselle di una mappa di Karnaugh può essere

convenientemente sfruttata, sostituendone alcune con il valore 1, al fine di ottenere gruppi (da 2, 4,

8) che portano a semplificare l’espressione della funzione.

Ad esempio, considerando la funzione parzialmente definita W la cui tabella di verità è riportata qui

sotto insieme con la relativa mappa di Karnaugh:

A

B

C

W

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

0

1

0

1

1

1

Si possono sostituire due condizioni don’t care con altrettanti 1:

e individuare la quaterna che consente di ottenere la seguente espressione semplificata di W:

W = B

Esempio:

ENCODER

Gli encoder (codificatori) sono dispositivi elettronici che trasformano una informazione non binaria

(ottale, decimale, codice gray, ecc.) in un codice binario. Ad esempio l’encoder di figura codifica una

cifra ottale in un numero binario.

In figura la configurazione dei bit di uscita è composta da “C B A” (A rappresenta il bit meno

significativo o LSB, C rappresenta il bit più significativo o MSB). La tabella di verità del suddetto

encoder è la seguente:

Quando si vorrà ad esempio codificare il numero (5)8, in ingresso sarà alto l’ingresso 5 e saranno

bassi tutti gli altri ingressi, in uscita si presenterà la configurazione (101)2 corrispondente al (5)8 in

binario.

Sintesi di un encoder

Si ricorda che il funzionamento di un encoder è basato sull’ipotesi che, in ogni istante, una e una

sola delle variabili di ingresso abbia il valore 1.

Si consideri il caso dell’encoder con 4 ingressi e due uscite:

Le due funzioni d’uscita Y0 ed Y1 sono, dunque, parzialmente definite perché le combinazioni di

valori delle variabili d’ingresso diverse da quelle in cui vi è un solo valore uguale ad 1 non si possono

presentare mai (la rete logica a monte sarà tale da produrre valori di Xi che soddisfano questa

ipotesi).

Delle 16 righe della tabella di verità sono significative solo le 4 nelle quali Y0 ed Y1 sono definite:

La corrispondente mappa di Karnaugh per la funzione Y0 è:

X0X1

X2X 3

00

01

11

10

00

0

1

X

0

01

1

X

X

X

11

X

X

X

X

10

0

X

X

X

Sfruttando le condizioni di indifferenza presenti in questa mappa, si possono disegnare i due

raggruppamenti da 8 caselle indicati in figura:

X0X1

X2X 3

00

01

11

10

00

0

1

X

0

01

1

X

X

X

11

X

X

X

X

10

0

X

X

X

E ottenere l’espressione semplificata: Y0 = X1 + X3

Analogamente si può ottenere: Y1 = X2 + X3

DECODER

Funzione inversa dell’encoder è realizzata dal decoder, cioè trasforma un codice binario in un codice

di tipo diverso (ottale, decimale, codice gray, ecc.). In Fig. 2 è riportato lo schema di un decoder da

codice binario BCD a cifra decimale.

La tabella di verità del suddetto decoder è la seguente:

Quando ad esempio in entrata si presenta la

configurazione binaria “011”, in uscita sarà alta

l’uscita 3 mentre tutte le altre uscite saranno

basse.

DECODER PER GENERARE FUNZIONI LOGICHE

Esempio: Si vuole realizzare la funzione Y = A + A ⋅ B con decoder binario decimale.

Svolgimento:

Il decoder decimale binario deve avere 2 ingressi e 4 uscite:

Il decoder ha la seguente tabella della verità:

Le funzioni di uscita sono:

I1

I2

I3

A

B

Io

I0 = A ⋅ B

0

0

1

0

0

0

I1 = A ⋅ B

0

1

0

1

0

0

I2 = A ⋅ B

1

0

0

0

1

0

I3 = A ⋅ B

1

1

0

0

0

1

Y = A + A ⋅ B = A ⋅ B + A ⋅ B + A ⋅ B =I3+I2+I1

Esempio: Si vuole realizzare la funzione Y = A ⋅ B ⋅ C + B con decoder binario decimale.

Il decoder decimale binario deve avere 3 ingressi e 8 uscite:

Il decoder ha la seguente tabella della verità:

Le funzioni di uscita sono:

A B C Io I1 I2 I3 I4 I5 I6 I7

I0 = A ⋅ B ⋅ C

0

0

0

1

0

0

0

0

0

0

0

I1 = A ⋅ B ⋅ C

0

0

1

0

1

0

0

0

0

0

0

I2 = A ⋅ B ⋅ C

0

1

0

0

0

1

0

0

0

0

0

I3 = A ⋅ B ⋅ C

0

1

1

0

0

0

1

0

0

0

0

I4 = A ⋅ B ⋅ C

1

0

0

0

0

0

0

1

0

0

0

I5 = A ⋅ B ⋅ C

1

0

1

0

0

0

0

0

1

0

0

I6 = A ⋅ B ⋅ C

1

1

0

0

0

0

0

0

0

1

0

I7 = A ⋅ B ⋅ C

1

1

1

0

0

0

0

0

0

0

1

Svolgimento:

Y = A⋅ B ⋅C + B = A⋅ B ⋅C + A⋅ B ⋅C + A⋅ B ⋅C + A⋅ B ⋅C + A⋅ B ⋅C = A⋅ B ⋅C + A⋅ B ⋅C + A⋅ B ⋅C + A⋅ B ⋅C =

= I 6 + I 2 + I3 + I7

(

)(

)

Esempio: Si vuole realizzare la funzione Y = A + B + C ⋅ A + B + C con decoder binario decimale.

Svolgimento:

(

)(

) (

)(

) (

)(

) (

)(

) (

)

Y = A + B + C ⋅ A + B + C = A + B + C ⋅ A + B + C = A⋅ B ⋅C ⋅( A⋅ B ⋅C ) = A⋅ B ⋅C + A⋅ B ⋅C =

= I3 + I7

Oppure

(

)(

)

Y = A + B + C ⋅ A + B + C = A + B + C ⋅ A + B + C = A + B + C ⋅ A + B + C = A⋅ B ⋅C + A⋅ B ⋅C =

= I3 + I7

A

B

C

DEC

3

a

8

Bin - Dec

I0

I1

I2

I3

I4

I5

I6

I7

Y

MULTIPLEXER

Un multiplexer è semplicemente una specie di interruttore fisico hardware in grado di connettere

l’uscita con uno dei n ingressi, ed in particolare con l’input scelto attraverso appositi segnali di

pilotaggio. Nel caso di un multiplexer a 4 ingressi e un’uscita (detto anche mux 4–1) in particolare

avrà:

• 4 segnali di ingresso;

• 2 segnali di pilotaggio, per selezionare l’ingresso 1, 2, 3 oppure 4;

Tabella di funzionamento per il multiplexer 4–1:

S1

S0

Yout

0

0

I0

0

1

I1

1

0

I2

1

1

I3

L’uscita del MUX sarà la seguente:

Yout = S1 ⋅ S0 ⋅ I 0 + S1 ⋅ S0 ⋅ I1 + S1 ⋅ S0 ⋅ I 2 + S1 ⋅ S0 ⋅ I 3

Il circuito che implementa questa funzione è il seguente:

Y

S0

S1

Nel caso di multiplexer 8 a 1, si avranno 8 ingressi dati, e 3 ingressi di selezione, la tabella della

verità risulta e il circuito che implementa il MUX 8 a 1 sono i seguenti:

C

B

A

F

0

0

0

D0

0

0

1

D1

0

1

0

D2

0

1

1

D3

1

0

0

D4

1

0

1

D5

1

1

0

D6

1

1

1

D7

Esempio: Realizzare la funzione Y = B ⋅ A + A ⋅ B con un multiplexer:

Svolgimento;

Useremo un multiplexer 4 a 1 con due ingressi di selezione A e B:

A

B

Yout

0

0

I0

0

1

I1

1

0

I2

1

1

I3

Yout = A ⋅ B ⋅ I 0 + A ⋅ B ⋅ I1 + A ⋅ B ⋅ I 2 + A ⋅ B ⋅ I 3

Con I0=I3=1 e I1=I2=0 otteniamo la funzione desiderata:

Esempio: Realizzare la funzione Y = A ⋅ B + A ⋅ C mediante un multiplexer:

Svolgimento;

Useremo un multiplexer 8 a 1 con tre ingressi di selezione A, B e C:

A B C Y

0

0

0 I0

0

0

1 I1

0

1

0 I2

0

1

1 I3

1

0

0 I4

1

0

1 I5

1

1

0 I6

1

1

1 I7

La funzione dell’esempio è

Y = A⋅ B + A⋅C = A⋅ B ⋅C + A⋅ B ⋅C + A⋅ B ⋅C + A⋅ B ⋅C

La funzione del multiplexer è:

Yout = A ⋅ B ⋅ C ⋅ I 0 + A ⋅ B ⋅ C ⋅ I1 + A ⋅ B ⋅ C ⋅ I 2 + A ⋅ B ⋅ C ⋅ I3 + A ⋅ B ⋅ C ⋅ I 4 + A ⋅ B ⋅ C ⋅ I5 + A ⋅ B ⋅ C ⋅ I 6 + A ⋅ B ⋅ C ⋅ I 7

Y = Yout se e solo se: I1 = I3 = I4 = I5 = 1 e I0 = I2 = I6 = I7 =0

I0

I1

I2

MUX

8

a

1

I3

I4

Y0

I5

I6

I7

A

B

C

Half Adder e Full Adder

L'half adder è un circuito logico che somma due bit e fornisce in uscita la somma (S) e il valore del

riporto (C).

La tabella di verità dell'half adder è la seguente:

A

B

S

C

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

Analizzando la tabella è chiaro come l'half adder si componga di una porta XOR e di una porta AND.

S = A⊕ B

S = A⋅C

Una limitazione dell'half adder, che fa sì che non possa essere utilizzato nella somma di numeri

binari con più bit, e che non tiene conto in ingresso del riporto generato da una somma precedente.

Per superare questa limitazione si introduce il full adder.

Il full adder presenta in ingresso anche il riporto della somma dei bit precedenti, quindi è una rete

a tre ingressi e due uscite.

Il full adder si compone di due half adder in sequenza secondo il seguente schema:

Con il primo half adder vengono sommati due bit ottenendo un valore e un riporto.

Con il secondo half adder sommo il riporto Cin al valore ottenuto dal primo half adder.

In uscita al full adder ottengo il bit valore della somma e il bit di riporto (come OR tra i riporti dei

due half adder).

Cin è il riporto di una eventuale somma tra due bit precedenti

Cout è il riporto generato dalla somma del bit A e del bit B, S è il valore della somma tra A,B e il

riporto Cin.

Il full adder lavora su una sola coppia di bit, per sommare numeri a n bit ho bisogno di n full adder

in sequenza.

Ad esempio per numeri a 4 bit avrei la seguente rete:

Dove:

A0 ... A3 sono i bit del primo numero

B0 ... B3 sono i bit del secondo numero.

S0 ... S3 sono i risultati delle somme delle coppie di bit

C0 ... C4 sono i riporti delle somme delle coppie di bit

es:

A = 1101; B = 0011

A + B = 1 0000

Decodificatore BCD a 7 segmenti

Un decodificatore BCD a 7 segmenti è una rete che ha 4 variabili di ingresso, che vanno interpretate come

la codifica in base 2 di una cifra decimale, e produce 7 uscite, che vanno ad accendere i segmenti di un display

a cristalli liquidi che illumina la cifra data in ingresso.

BCD sta per Binary Coded Decimal, ed è un modo per rappresentare i numeri naturali, tipico delle calcolatrici

tascabili con display LCD. Con tale tipo di rappresentazione, ciascuna cifra decimale viene rappresentata su

4 bit.

0

1

2

3

4

5

6

7

8

9

X3 X2 X1 X0

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

a

1

0

1

1

0

1

1

1

1

1

b

1

1

1

1

1

0

0

1

1

1

c

1

1

0

1

1

1

1

1

1

1

d

1

0

1

1

0

1

1

0

1

1

Ricaviamo la funzione e:

e = X 3 + X1 ⋅ X 0 + X 2 ⋅ X 0

e

1

0

1

0

0

0

1

0

1

0

f

1

0

0

0

1

1

1

0

1

1

g

0

0

1

1

1

1

1

0

1

1

LATCH

LATCH SR

Q

Q

TABELLA DELLA VERITA’

S R Q

Q

0 0 Q0

MEMORIA

0 1

0

RESET

1 0

1

SET

1 1 N.V. NON VALIDO

LATCH SR CON ENABLE

Q

Q

EN

0

1

1

1

1

TABELLA DELLA VERITA’

S R Q

Q

X X Q0

MEMORIA

0 0 Q0

MEMORIA

0 1

0

RESET

1 0

1

SET

1 1 N.V. NON VALIDO

LATCH D

Q

Q

TABELLA DELLA VERITA’

Q

EN D Q

0 X Q0 MEMORIA

1 0 0

1 1 1

FLIP FLOP

SR

CK

S

TABELLA DELLA VERITA’

R CLR PRE Q

↑↓

0

0

0

0

Q0

MEMORIA

↑↓

0

1

0

0

0

RESET

↑↓

1

0

0

0

1

SET

↑↓

1

1

0

0

↑↓

X

X

1

0

0

RESET

↑↓

X

X

0

1

1

PRESET

↑↓

X

X

1

1

FF - D

Q

N.V. NON VALIDO

N.V. NON VALIDO

TABELLA DELLA VERITA’

CK

↑↓

↑↓

↑↓

↑↓

↑↓

FF - JK

CK

J

D CLR PRE

0

1

X

X

X

0

0

1

0

1

0

0

0

1

1

Q

0

1

0

1

N.V.

TABELLA DELLA VERITA’

K CLR PRE Q

Q

↑↓ 0 0

↑↓ 0 1

↑↓ 1 0

0

0

0

0

0

0

Q0

0

1

MEMORIA

RESET

SET

↑↓ 1 1

0

0

Q0

TOGGLE

↑↓ X X

↑↓ X X

↑↓ X X

1

0

1

0

1

1

0

RESET

1

PRESET

N.V. NON VALIDO

TABELLA DELLA VERITA’

CK T CLR PRE Q

↑↓ 0 0

0

Qo

↑↓ 1

0

0

↑↓ X

↑↓ X

↑↓ X

1

0

1

0

1

1

Qo

0

1

N.V.

ESERCIZI

Convertire in decimale i seguenti numeri binari: 11101,01; 10110,101; 110,0101; 1101010,0101.

Convertire in decimale i seguenti numeri ottali: 134,2; 102,51; 574,3; 253,4.

Convertire in ottale i seguenti numeri binari: 111101,01011; 10101,10101; 101,01010; 110011; 10110,000111.

Convertire in decimale i seguenti numeri esadecimali: 1,A; B2,1; 1E,8; F2,D8.

Convertire in esadecimale i seguenti numeri binari: 10001,00111; 101001,1010; 101,010101; 11001111; 1010,00101.

Effettuare le seguenti conversioni tra sistemi di numerazione:

1) (325,67)8

(

)10 ; (615,45)8

(

2) (694,75)10

3) (5734,25)10

(

)10 ; (572,42)8

)8 ; (347,03125)10

(

4) (54C,D2)16

(

(

)16; (145,1875)10

(

)10 ; (243,1)8

)8 ; (749,4375)10

(

)8; (ABC,DE)16

(

(

(

(

)10;

)8;

)16; (1986,15625)10

)8; (FED,CB)16

(

)16;

)8; (1A6,2B)16

(

)8;

5) (524,67)8

(

)16; (342,72)8

(

)16; (461,32)8

(

)16; (2460,06)8

(

)16;

6) (424,05)8

(

)2; (30C,04)16

(

)2; (502,426)8

(

)2; (DFF,0A)16

(

)2;

7) (426,35)8

(

(

)10 ; (223,46)8

)10 ; (173,42)8

(

8) (874,25)10

9) (3457,03125)10

)8 ; (985,03125)10

(

(

10) (CA4,B6)16

(

)16; (532,375)10

(

)16; (642,14)8

(

)16; (200,47)8

12) (407,02)8

(

)2; (CED,42)16

(

)2; (236,421)8

13) (426,35)8

(

(

)10 ; (223,46)8

(

15) (2027,03125)10

)8 ; (345,03125)10

(

16) (AA4,B6)16

(

(

)16; (532,375)10

(

(

(

(

)8; (A65,FB)16

(

)8;

)16; (603,047)8

(

)16;

)10 ; (567,7)8

(

)16; (5422,625)10

(

(

)2

(

)10;

)8;

(

)8; (A25,4A)16

)10;

)16;

)2; (FAF,BC)16

)8 ; (561,09375)10

(

)8; (CB5,DB)16

(

(

)8;

(

)8; (A52,4B)16

(

14) (704,25)10

(

)16; (8632,625)10

11) (754,34)8

)10 ; (173,42)8

)10 ; (567,7)8

)8 ; (481,09375)10

(

)8; (CE4,DF)16

(

)16;

)8; (A5B,FB)16

(

)8;

17) (254,24)8

(

)16; (632,54)8

(

)16; (100,47)8

(

)16; (305,047)8

(

)16;

18) (306,04)8

(

)2; (CCB,31)16

(

)2; (637,531)8

(

)2; (FAD,A5)16

(

)2;

19) Determinare gli equivalenti decimali dei seguenti numeri binari dotati di segno a 8 bit:

a) (10101001)2=(

)10 ; b) (10000010)2=(

)10 ; c) (11100010)2=(

)10; d)(01100010)2=(

)10;

20) Convertire in binario con parole di 8 bit i seguenti numeri decimali negativi:

a) (-38)10 =(

)2 ; b) (-10)10=(

)2;

c) (-17)10=(

)2;

d) (-107)10=(

)2;

21) Eseguire le seguenti somme di numeri binari

a) (1010101)2 + (10011)2 = (

b) (10101001)2 + (100010)2 = (

)2 ;

)2 ;

22) Eseguire le seguenti moltiplicazioni tra numeri binari

a) (10010101)2 x (11)2 = (

)2 ;

)2 ;

b) (11100001)2 x (101)2 = (

23) Eseguire le seguenti somme di numeri binari dotati di segno a 8 bit

a) (-38)10 + (-67)10 = (

)2 + (

)2 ;

)2 + (

)2 ;

b) (-17)10 - (-67)10 = (

24) Determinare gli equivalenti decimali dei seguenti numeri binari dotati di segno a 8 bit:

a) (10101001)2=(

)10 ; b) (10000010)2=(

)10 ; c) (11100010)2=(

)10; d)(01100010)2=(

)10;

25) Convertire in binario con parole di 8 bit i seguenti numeri decimali negativi:

a) (-38)10 =(

)2 ; b) (-10)10=(

)2;

26) Eseguire le seguenti somme di numeri binari

a) (1010101)2 + (10011)2 = (

b) (10101001)2 + (100010)2 = (

c) (-17)10=(

)2;

d) (-107)10=(

)2;

)2 ;

)2 ;

27) Eseguire le seguenti moltiplicazioni tra numeri binari

a) (10010101)2 x (11)2 = (

)2 ;

b) (11100001)2 x (101)2 = (

)2 ;

28) Eseguire le seguenti somme di numeri binari dotati di segno a 8 bit

a) (-38)10 + (-67)10 = (

)2 + (

)2 ;

b) (-17)10 - (-67)10 = (

)2 + (

)2 ;

29) Determinare gli equivalenti decimali dei seguenti numeri binari dotati di segno a 8 bit:

a) (10101001)2=(

)10 ; b) (10000010)2=(

)10 ; c) (11100010)2=(

)10; d)(01100010)2=(

)10;

30) Convertire in binario con parole di 8 bit i seguenti numeri decimali negativi:

a) (-38)10 =(

)2 ; b) (-10)10=(

31) Eseguire le seguenti somme di numeri binari

a) (1010101)2 + (10011)2 = (

b) (10101001)2 + (100010)2 = (

)2;

c) (-17)10=(

)2 ;

)2 ;

32) Eseguire le seguenti moltiplicazioni tra numeri binari

a) (10010101)2 x (11)2 = (

)2 ;

b) (11100001)2 x (101)2 = (

)2 ;

33) Eseguire le seguenti somme di numeri binari dotati di segno a 8 bit

a) (-38)10 + (-67)10 = (

)2 + (

)2 ;

b) (-17)10 - (-67)10 = (

)2 + (

)2 ;

)2;

d) (-107)10=(

)2;

Effettuare le seguenti conversioni tra sistemi di numerazione:

34) (256,45)8

35) (654,25)10

36) (2477,03125)10

(

)10 ; (172,05)8

(

(

)10 ; (457,25)8

)8 ; (1234,03125)10

(

(

)16; (1502,375)10

(

)10 ; (371,6)8

)8 ; (3481,09375)10

(

(

)16; (49812,625)10

(

)10;

)8;

(

)16;

37) Determinare gli equivalenti decimali dei seguenti numeri binari dotati di segno a 8 bit:

a) (10011100)2=(

)10 ; b) (00001001)2=(

)10 ; c) (10100101)2=(

)10; d)(01101110)2=(

)10;

38) Convertire in binario con parole di 8 bit i seguenti numeri decimali negativi:

a) (-28)10 =(

)2 ; b) (-16)10=(

)2;

39) Eseguire le seguenti somme di numeri binari

a) (101010101)2 + (100101)2 = (

b) (1010111001)2 + (111010)2 = (

c) (-105)10=(

)2;

d) (-93)10=(

)2;

)2 ;

)2 ;

40) Eseguire le seguenti moltiplicazioni tra numeri binari

a) (11110101)2 x (11)2 = (

)2 ;

)2 ;

b) (11100101)2 x (101)2 = (

41) Eseguire le seguenti somme di numeri binari dotati di segno a 8 bit

a) (-28)10 - (-104)10 = (

)2 + (

)2 ;

b) (-107)10 - (-47)10 = (

)2 + (

)2 ;

42) Disegnare lo schema del circuito combinatorio corrispondente alla seguente funzione

Y = ( A + C ) ⋅ ( B + C ) utilizzando il sistema di porte logiche universali AOI (AND,OR e INVERTER)

43) Disegnare lo schema del circuito combinatorio corrispondente alla funzione

Y = ( A + C ) ⋅ ( B + C ) + D utilizzando il sistema di porte logiche universali AOI (AND,OR e INVERTER)

44) Disegnare lo schema del circuito combinatorio corrispondente alla seguente funzione

Y = ( A ⋅ B + C ⋅ D ) ⋅ E utilizzando il sistema di porte logiche universali AOI (AND,OR e INVERTER)

45) Determinare Y1 e Y per il circuito di figura:

A

Y1 =

B

Y

C

46) Determinare Y1, Y2 e Y per il circuito di figura:

47) Determinare Y1, Y2 e Y3 per il circuito di figura:

48) Per la funzione Y dell’esercizio 46 e dell’esercizio 47 determinare le tabelle della verità.

49) Disegnare lo schema del circuito combinatorio corrispondente alla seguente funzione

= + ∙ ∙ utilizzando il sistema di porte logiche universali AOI (AND,OR e INVERTER)

50) Disegnare lo schema del circuito combinatorio corrispondente alla seguente funzione

= ̅ ∙ + + utilizzando il sistema di porte logiche universali AOI (AND,OR e INVERTER)

51) Disegnare lo schema del circuito combinatorio corrispondente alla seguente funzione

Y = A + ( B + C ) ⋅ D utilizzando il sistema di porte logiche universali AOI (AND,OR e INVERTER)

52) Disegnare lo schema del circuito combinatorio corrispondente alla funzione

(

)

Y = A ⋅ B + C ⋅ D utilizzando il sistema di porte logiche universali AOI (AND,OR e INVERTER)

53) Disegnare lo schema del circuito combinatorio corrispondente alla seguente funzione

Y = A ⋅ B + C ⋅ D utilizzando il sistema di porte logiche universali AOI (AND,OR e INVERTER)

54) Determinare Y per il circuito di figura:

55) Determinare Y1, Y2 e Y per il circuito di figura:

56) Determinare Y1, Y2 e Y3 per il circuito di figura:

57) Disegnare lo schema del circuito combinatorio corrispondente alla seguente funzione

Y = ( A + B + C ) ⋅ ( A + B + C ) utilizzando il sistema di porte logiche universali AOI (AND,OR e INVERTER)

58) Per la funzione Y dell’esercizio 54 e dell’esercizio 56 determinare le tabelle della verità.

59) Disegnare lo schema del circuito combinatorio corrispondente alla seguente funzione

Y = A+ B +C

utilizzando il sistema di porte logiche universali AOI (AND,OR e INVERTER)

60) Data la seguente funzione logica:

F = A⋅ B ⋅ C ⋅ D + A⋅ B ⋅C ⋅ D + A⋅ B ⋅C ⋅ D

a) Scrivere la tabella della verità

b) Esprimere la funzione F in forma canonica come somma di prodotti

61) Data la funzione Y espressa dalla seguente tabella della verità:

A B C D Y

0 0 0 0 1

0 0 0 1 1

0 0 1 0 0

0 0 1 1 1

0 1 0 0 1

0 1 0 1 1

0 1 1 0 0

0 1 1 1 1

1 0 0 0 1

1 0 0 1 1

1 0 1 0 0

1 0 1 1 1

1 1 0 0 1

1 1 0 1 1

1 1 1 0 0

1 1 1 1 1

a) Determina la funzione Y con la seconda forma canonica.

b) Disegna il circuito logico

62) Data la seguente funzione logica:

F = A⋅ B ⋅ C ⋅ D + A⋅ B ⋅C ⋅ D + A⋅ B ⋅C ⋅ D

a) Scrivere la tabella della verità

b) Disegnare il circuito logico combinatorio della 2a forma canonica

63) Data la seguente tabella della verità:

A

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C D Y F

0 0 1 0

0 1 1 1

1 0 0 0

1 1 1 0

0 0 1 1

0 1 1 0

1 0 0 0

1 1 1 1

0 0 1 0

0 1 1 0

1 0 0 0

1 1 1 1

0 0 1 0

0 1 1 0

1 0 0 0

1 1 1 0

a) Determinare la funzione Y con la seconda forma canonica.

b) Determinare la funzione F con la prima forma canonica.

c) Disegnare il circuito logico combinatorio per i due casi precedenti a) e

b).

64) Data la seguente tabella della verità:

A

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C D F Y

0 0 0 1

0 1 0 1

1 0 0 1

1 1 1 1

0 0 1 1

0 1 0 0

1 0 0 1

1 1 0 1

0 0 1 0

0 1 0 1

1 0 0 1

1 1 0 1

0 0 0 0

0 1 1 1

1 0 0 1

1 1 0 0

a) Determinare la funzione F con la prima forma canonica.

b) Determinare la funzione Y con la seconda forma canonica.

c) Disegnare il circuito logico combinatorio per i due casi precedenti a) e b).

65) Disegnare lo schema del circuito combinatorio corrispondente alla funzione:

Y = A⋅ B + D + C ⋅ D ⋅ B ⋅C + D

66) Disegnare lo schema del circuito combinatorio corrispondente alla funzione:

Y = ( A + C ⋅ D) ⋅ B + C + D

67) Applicare il teorema di De Morgan alle seguenti funzioni:

Y1 = A ⋅ B ⋅ C + D ⋅ E ⋅ A + B ⋅ C

Y2 = A + B + C ⋅ D + B ⋅ E ⋅ (C + A ⋅ D )

Y3 = A + ( B ⋅ C + C ⋅ D) ⋅ E

Y4 = B + C ⋅ D + A + B ⋅ (C ⋅ D + B )

68) Applicare il teorema di De Morgan alla seguente funzione

F = ( A + BC ) ⋅ D

69) Applicare il teorema di De Morgan alla seguente funzione almeno 2 volte

F = ( AC + BC )

70) Applicare il teorema di De Morgan alla seguente funzione almeno 2 volte

F = ( A + C )( B + D)

71) Applicare il teorema di De Morgan alla seguente espressione:

F = A⋅ B + A⋅ B ⋅C + A + C

si richiedono almeno 2 passaggi

72) Applicare il teorema di De Morgan alla seguente espressione:

F = A ⋅ B + A ⋅ B ⋅ C + ( A + B) ⋅ C

si richiedono almeno 3 passaggi

73) Realizzare lo schema del circuito combinatorio corrispondente alla seguente funzione:

F = ( A + B) ⋅ (C + D )

utilizzando solo porte NOR

74) Realizzare lo schema del circuito combinatorio corrispondente alla seguente funzione:

F = A⋅ B + A⋅C ⋅ D

utilizzando solo porte NAND

75) Determinare Y1, Y2, Y3 e Y per il circuito di figura:

76) Determinare Y1, Y2, Y3 e Y per il circuito di figura:

77) Data la seguente funzione logica:

F = A⋅C + A⋅ B ⋅C ⋅ D + A⋅ B ⋅C ⋅ D + A⋅C ⋅ D + A⋅ B ⋅ D

a. esprimere la funzione F in forma canonica

b. determinare la tabella della verità di F

c. disegnare il circuito logico combinatorio di F solo con porte NAND.

78) Determinare Y per il circuito di figura:

A

B

C

D

Y1

Y2

Y3

Y

79) Data la seguente tabella della verità:

A B C Y1 Y2

0

0

0

0

1

0

0

1

1

0

0

1

0

0

1

0

1

1

1

0

1

0

0

0

1

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

a) Determinare Y1 con la 1° forma canonica e Y2 con la 2° forma canonica.

b) Realizzare lo schema di Y1 usando solo porte NOR e solo porte NAND (devi fare 2

Circuiti Logici).

c) Realizzare lo schema di Y2 usando solo porte NOR e solo porte NAND (devi fare 2

Circuiti Logici).

d) Determinare Y1min e Y2mincon il metodo delle mappe di Karnaugh

80) Data la seguente funzione logica:

F = (A + B + C ) ⋅ ( A + B + C + D ) ⋅ ( A+ B +C + D ) ⋅ (A+C +D ) ⋅ ( B + D )

a. esprimere la funzione F in forma canonica

b. determinare la tabella della verità di F

c. disegnare il circuito logico combinatorio di F solo con porte NOR.

81) Data la seguente funzione logica:

F = (A + C ) ⋅ ( A + B + C + D ) ⋅ ( A + B + C + D ) ⋅ (A + C + D ) ⋅ ( A + B + C + D ) ⋅ ( A + B + C )

a. esprimere la funzione F in forma canonica.

b. determinare la tabella della verità di F.

c. disegnare il circuito logico combinatorio di F solo con porte logiche NOR.

82) Disegna una mappa di Karnough 2x2, posizionare gli 1 nelle caselle (0,4,5,10,14,15), minimizzare la funzione.

R. Y = A ⋅ C ⋅ D + A ⋅ B ⋅ C + A ⋅ B ⋅ C + A ⋅ C ⋅ D

83) Disegna una mappa di Karnough 2x2, posiziona gli 1 nelle caselle (0,1,5,6,7,8,10), determina la tabella della verità

della funzione, esprimere la funzione con la 1° e la 2° forma canonica, minimizzare la funzione, realizzare il circuito

combinatorio che realizza la funzione.

R. Y = A ⋅ B ⋅ C + A ⋅ C ⋅ D + A ⋅ B ⋅ C + A ⋅ B ⋅ D

84) Disegna una mappa di Karnough 2x2, posiziona gli 1 nelle caselle (0,2,3,7,8,10,13), determina la tabella della verità

della funzione, esprimere la funzione con la 1° e la 2° forma canonica, minimizzare la funzione, realizzare il circuito

combinatorio che realizza la funzione.

R. Y = B ⋅ D + A ⋅ C ⋅ D + A ⋅ B ⋅ C ⋅ D

85) Disegna una mappa di Karnough 2x2, posiziona gli 1 nelle caselle (0,4,5,6,7,8,12,13,15), determina la tabella della

verità della funzione, esprimere la funzione con la 1° e la 2° forma canonica, minimizzare la funzione, realizzare il

circuito combinatorio che realizza la funzione.

R. Y = C ⋅ D + B ⋅ D + ⋅ A ⋅ B

86) Disegna una mappa di Karnough 2x2, posiziona gli 1 nelle caselle (1,3,4,6,7,9,11,12,13,14), determina la tabella

della verità della funzione, esprimere la funzione con la 1° e la 2° forma canonica, minimizzare la funzione,

realizzare il circuito combinatorio che realizza la funzione.

R. Y = B ⋅ D + B ⋅ D + A ⋅ C ⋅ D + A ⋅ C ⋅ D

87) Disegna una mappa di Karnough 2x1, posiziona gli 1 nelle caselle (0,1,3,5,6), determina la tabella della verità della

funzione, esprimere la funzione con la 1° e la 2° forma canonica, minimizzare la funzione, realizzare il circuito

combinatorio che realizza la funzione.

R. Y = A ⋅ B + A ⋅ C + B ⋅ C + A ⋅ B ⋅ C

88) Disegnare una mappa di Karnough 2x2, posizionare gli 1 nelle caselle (0,1,8,10,12,14,15), minimizzare la funzione.

R. Y = A ⋅ B ⋅ C + A ⋅ B ⋅ C + A ⋅ D

89) Disegnare una mappa di Karnough 2x2, posizionare gli 1 nelle caselle (0,2,3,4,8,11,13,15), determinare la tabella

della verità della funzione, esprimere la funzione con la 1° e la 2° forma canonica, minimizzare la funzione,

realizzare il circuito combinatorio che realizza la funzione minima.

R. Y = A ⋅ C ⋅ D + B ⋅ C ⋅ D + A ⋅ B ⋅ D + A ⋅ C ⋅ D + A ⋅ B ⋅ C

90) Disegnare una mappa di Karnough 2x2, posizionare gli 1 nelle caselle (0,1,2,3,6,8,10,14,15), determinare la tabella

della verità della funzione, esprimere la funzione con la 1° e la 2° forma canonica, minimizzare la funzione,

realizzare il circuito combinatorio che realizza la funzione.

R. Y = A ⋅ B + C ⋅ D + A ⋅ B ⋅ C

91) Disegnare una mappa di Karnough 2x2, posizionare gli 1 nelle caselle (1,2,3,4,6,9,10,11,12,14) determinare la

tabella della verità della funzione, esprimere la funzione con la 1° e la 2° forma canonica, minimizzare la funzione,

realizzare il circuito combinatorio che realizza la funzione minima con sole porte NAND.

R. Y = B ⋅ D + B ⋅ D + C ⋅ D

92) Disegnare una mappa di Karnough 2x1, posizionare gli 1 nelle caselle (0,2,5,7), determinare la tabella della verità

della funzione, esprimere la funzione con la 1° e la 2° forma canonica, minimizzare la funzione, realizzare il circuito

combinatorio che realizza la funzione minima con sole porte NOR.

R. Y = A ⋅ C + A ⋅ C

93) Disegnare una mappa di Karnough 2x2, posizionare gli 1 nelle caselle (1,4,5,6,7,9,12,13,14,15), minimizzare la

funzione.

R. Y = B + C ⋅ D

94) Disegnare una mappa di Karnough 2x2, posizionare gli 1 nelle caselle (0,2,5,6,7,8,10,12,13,15), determinare la

tabella della verità della funzione, esprimere la funzione con la 1° e la 2° forma canonica, minimizzare la funzione,

realizzare il circuito combinatorio che realizza la funzione minima.

R. Y = B ⋅ D + B ⋅ D + A ⋅ B ⋅ C + A ⋅ B ⋅ C

95) Disegnare una mappa di Karnough 2x2, posizionare gli 1 nelle caselle (1,2,3,7,9,11,12,13), determinare la tabella

della verità della funzione, esprimere la funzione con la 1° e la 2° forma canonica, minimizzare la funzione,

realizzare il circuito combinatorio che realizza la funzione.

R. Y = B ⋅ C + A ⋅ B ⋅ C + A ⋅ C ⋅ D + A ⋅ B ⋅ C

96) Disegnare una mappa di Karnough 2x2, posizionare gli 1 nelle caselle (1,2,5,9,10,12,13,14,15) determinare la

tabella della verità della funzione, esprimere la funzione con la 1° e la 2° forma canonica, minimizzare la funzione,

realizzare il circuito combinatorio che realizza la funzione minima con sole porte NAND.

R. Y = A ⋅ B + C ⋅ D + B ⋅ C ⋅ D

97) Disegnare una mappa di Karnough 2x2, posizionare gli 1 nelle caselle (2,3,4,5,6,7,10,11,12,13,14,15), determinare

la tabella della verità della funzione, esprimere la funzione con la 1° e la 2° forma canonica, minimizzare la funzione,

realizzare il circuito combinatorio.

R. Y = C + B + A ⋅ D

98) Data la seguente funzione logica:

a)

b)

c)

d)

F = (A + B + C ) ⋅ ( B + C + D ) ⋅ ( A +B + C +D ) ⋅ ( A +B+C + D ) ⋅ ( A + B + C + D )

esprimere la funzione F in forma canonica come prodotti di somme

disegnare la mappa di Karnaugh corrispondente alla funzione F

determinare la funzione F nella sua forma minima Fmin

realizzare lo schema di Fmin con sole porte NAND

Risultato: Fmin = B ⋅ C + A ⋅ D + A ⋅ C + B ⋅ C

99) Data la seguente funzione logica:

F = A⋅ B ⋅C ⋅ D + B ⋅C ⋅ D + A ⋅ B ⋅C ⋅ D + A⋅C ⋅ D + A⋅ B ⋅ D

a)

b)

c)

d)

esprimere la funzione F in forma canonica come somma di prodotti

disegnare la mappa di Karnaugh corrispondente alla funzione F

determinare la funzione nella sua forma minima Fmin

realizzare lo schema di Fmin con sole porte NOR

Risultato: Fmin = A ⋅ D + A ⋅ B ⋅ C + B ⋅ C ⋅ D + A ⋅ B ⋅ C

100)

a)

b)

c)

d)

Data la seguente funzione logica:

F = (A + B + D ) ⋅ ( A + C + D ) ⋅ ( A + B + C )

esprimere la funzione F in forma canonica come prodotti di somme

disegnare la mappa di Karnaugh corrispondente alla funzione F

determinare la funzione nella sua forma minima Fmin

realizzare lo schema di Fmin con sole porte NAND

Risultato: Fmin = A ⋅ D + B ⋅ D + A ⋅ C

101)

Data la seguente funzione logica:

F = A⋅C + B ⋅C ⋅ D + A⋅ B ⋅C + A⋅ B ⋅C ⋅ D + A⋅ B ⋅C ⋅ D

a)

b)

c)

d)

esprimere la funzione F in forma canonica come somma di prodotti

disegnare la mappa di Karnaugh corrispondente alla funzione F

determinare la funzione nella sua forma minima Fmin

realizzare lo schema di Fmin con sole porte NOR

Risultato: Fmin = C ⋅ D + B ⋅ C + A ⋅ C + A ⋅ B ⋅ D

102)

Realizzare la seguente funzione utilizzando un multiplexer :

Y = A⋅ B ⋅C + A⋅ B ⋅C + A⋅ B ⋅C

103)

Realizzare la seguente funzione utilizzando un multiplexer :

(

Y = ( A + B + C) ⋅ A + B + C

104)

)

Realizzare la seguente funzione utilizzando un decoder :

Y = A ⋅ (B + C)

105)

Realizzare la seguente funzione utilizzando un multiplexer:

Y = A⋅ B + A⋅C

106)

Realizzare la seguente funzione utilizzando un multiplexer:

Y = A+ B +C

107)

Realizzare la seguente funzione utilizzando un decoder:

Y = ( A + B + C) ⋅ ( A + B + C)

108)

Realizzare il circuito che implementi la funzione f di uscita di un Decoder Driver BCD-7 Segmenti

109)

Realizzare il circuito che implementi la funzione c di uscita di un Decoder Driver BCD-7 Segmenti

110)

Realizzare lo schema logico del circuito di un multiplexer 4-a-1

111)

Progettare un circuito di codifica da decimale a BCD

112)

Realizzare lo schema logico del circuito di un HALF – ADDER

113)

Realizzare la seguente funzione utilizzando un decoder :

Y = A⋅ B ⋅C + A⋅ B ⋅C + A⋅ B ⋅C

114)

Realizzare la seguente funzione utilizzando un decoder :

115)

Y = ( A + B + C )( A + B + C )

Realizzare la seguente funzione utilizzando un multiplexer:

Y = A⋅ B + A⋅C

116)

Realizzare la seguente funzione utilizzando un multiplexer:

Y = A + B ⋅C

117)

Realizzare il circuito che implementi la funzione f di uscita di un Decoder Driver BCD-7 Segmenti

118)

Realizzare lo schema logico del circuito che realizzi un multiplexer 4-a-1

119)

Progettare un circuito di codifica da decimale a BCD

120)

Realizzare la seguente funzione utilizzando un multiplexer:

Y = A⋅ B ⋅C + C

121)

Realizzare la seguente funzione utilizzando un decoder :

Y = A⋅ B ⋅ C + A⋅ B ⋅C + B ⋅C

122)

Realizzare la seguente funzione utilizzando un multiplexer:

Y = A⋅ B + B

123)

Realizzare la seguente funzione utilizzando un decoder :

Y = ( B + C )( A + C )

124)

Realizzare lo schema logico del circuito che implementi un decoder binario - decimale a 2 ingressi e 4 uscite

125)

Realizzare la seguente funzione utilizzando un decoder e un multiplexer:

Y = A⋅ B ⋅C + A⋅ B ⋅C + A⋅ B ⋅C

126)

Realizzare la seguente funzione utilizzando un decoder e un multiplexer:

Y = A⋅ B ⋅C + A⋅ B ⋅C + A⋅ B ⋅C

127)

Realizzare la seguente funzione indicata dalla seguente tabella della verità con un decoder :

A B C Y

0

0

0

0

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

0

1

0

1

1

1

1

0

1

1

1

1

1

128)

Realizzare la seguente funzione utilizzando un decoder :

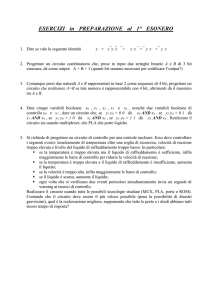

Y = (A + B + C) ⋅(A + B + C)

129) Determinare l’evoluzione temporale dell’uscita Q sapendo che essa parte bassa e che entrano dei segnali fatti

come riportato di seguito:

130) Determinare l’evoluzione temporale dell’uscita Q sapendo che essa parte alta e che entrano dei segnali fatti

come riportato di seguito:

131) Sia dato un Latch SR con ingresso di abilitazione. Determinare l’evoluzione temporale dell’uscita Q sapendo

che essa parte bassa e che entrano dei segnali fatti come riportato di seguito:

132) Sia dato un Latch di tipo D. Determinare l’evoluzione temporale dell’ uscita Q sapendo che Q parte alta e che

entrano dei segnali fatti come riportato di seguito:

133) Sia dato un Latch SR con ingresso di abilitazione. Determinare l’evoluzione temporale dell’ uscita Q sapendo

che Q parte bassa e che entrano dei segnali fatti come riportato di seguito:

134) Sia dato un Latch di tipo D. Determinare l’evoluzione temporale dell’ uscita Q sapendo che Q parte alta e che

entrano dei segnali fatti come riportato di seguito:

135) Sia dato un Latch SR con ingresso di abilitazione. Determinare l’evoluzione temporale dell’ uscita Q sapendo

che Q parte bassa e che entrano dei segnali fatti come riportato di seguito:

EN

S

R

Q

136) Sia dato un Latch SR. Determinare l’evoluzione temporale dell’uscita Q sapendo che essa parte bassa e che

entrano dei segnali fatti come riportato di seguito:

137) Sia dato un Latch SR. Determinare l’evoluzione temporale dell’uscita Q sapendo che essa parte alta e che

entrano dei segnali fatti come riportato di seguito:

138) Sia dato un Latch SR. Determinare l’evoluzione temporale dell’uscita Q sapendo che essa parte alta e che

entrano dei segnali fatti come riportato di seguito:

139) Sia dato un Latch SR. Determinare l’evoluzione temporale dell’uscita Q sapendo che Q parte bassa e che

entrano dei segnali fatti come riportato di seguito:

140) Sia dato un Latch SR con ingresso di abilitazione. Determinare l’evoluzione temporale dell’uscita Q sapendo

che Q parte bassa e che entrano dei segnali fatti come riportato di seguito:

141) Sia dato un Latch di tipo D. Determinare l’evoluzione temporale dell’uscita Q sapendo che Q parte bassa e che

entrano dei segnali fatti come riportato di seguito:

142) Sia dato un Latch SR con ingresso di abilitazione. Determinare l’evoluzione temporale dell’uscita Q sapendo

che Q parte alta e che entrano dei segnali fatti come riportato di seguito:

143) Sia dato un Latch di tipo D. Determinare l’evoluzione temporale dell’uscita Q sapendo che Q parte alta e che

entrano dei segnali fatti come riportato di seguito:

144) Sia dato un Latch SR. Determinare l’evoluzione temporale dell’uscita Q sapendo che essa parte bassa e che

entrano dei segnali fatti come riportato di seguito:

145) Sia dato un Latch SR. Determinare l’evoluzione temporale dell’uscita Q sapendo che essa parte alta e che

entrano dei segnali fatti come riportato di seguito:

146)

Sia dato un FF- SR negative edge triggered. Determinare l’evoluzione temporale dell’uscita Q:

147)

Sia dato un Latch D con ingresso di abilitazione. Determinare l’evoluzione temporale dell’uscita Q:

148)

Sia dato un FF- JK negative edge triggered. Determinare l’evoluzione temporale dell’uscita Q:

149)

Sia dato un FF- D negative edge triggered . Determinare l’evoluzione temporale dell’uscita Q:

150)

Sia dato un FF SR positive edge triggered. Determinare l’evoluzione temporale dell’uscita Q:

151)

Sia dato un FF- T positive edge triggered. Determinare l’evoluzione temporale dell’uscita Q:

152)

Sia dato un Latch SR con ingresso di abilitazione. Determinare l’evoluzione temporale dell’uscita Q:

153)

Sia dato un FF- JK positive edge triggered. Determinare l’evoluzione temporale dell’uscita Q:

154)

Sia dato un Latch SR con ingresso di abilitazione. Determinare l’evoluzione temporale dell’uscita Q:

155)

Determinare l’evoluzione temporale di Q nel caso di FF - T positive edge triggered:

CK

CLR

t

PRE

t

T

t

Q

t

t

156)

Determinare il Q per un FF-SR P.E.T.:

157)

Determinare il Q per un FF-D N.E.T.:

158)

Determinare il Q per un FF-JK N.E.T.:

159)

Determinare il Q per un FF-JK P.E.T.:

160)

Determinare il Q per un FF-SR P.E.T.:

161)

Determinare il Q per un FF-T N.E.T.:

162)

Determinare il Q per un FF – D N.E.T.::

163)

Determinare il Q per un FF – SR P.E.T.: