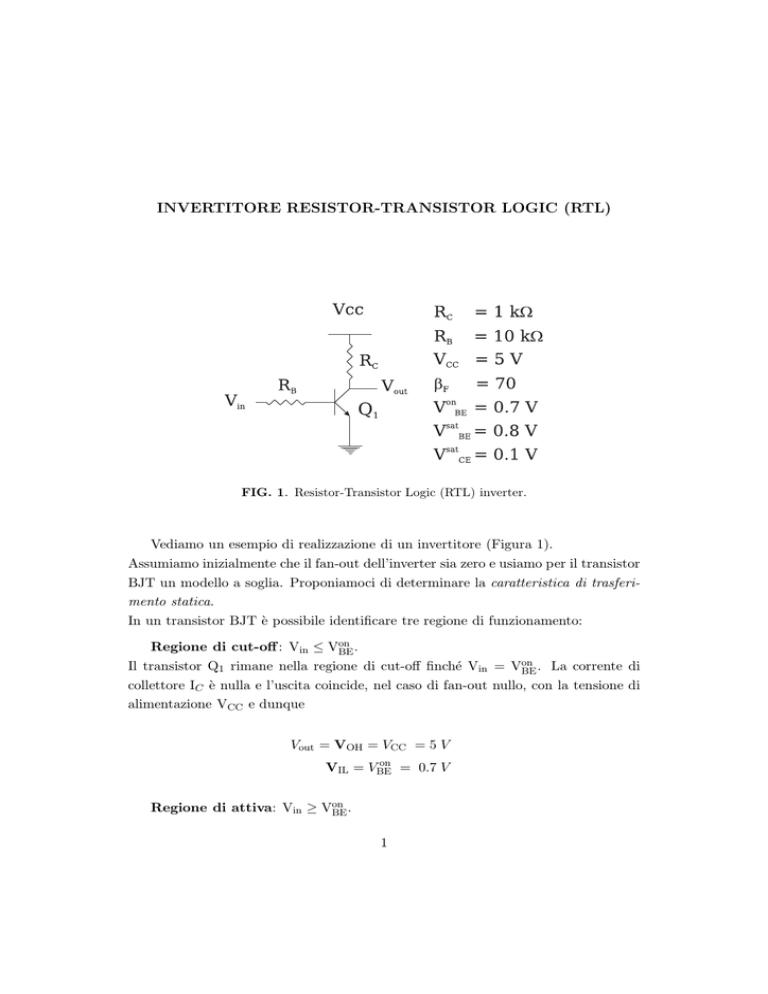

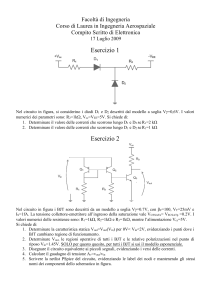

INVERTITORE RESISTOR-TRANSISTOR LOGIC (RTL)

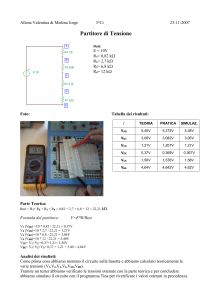

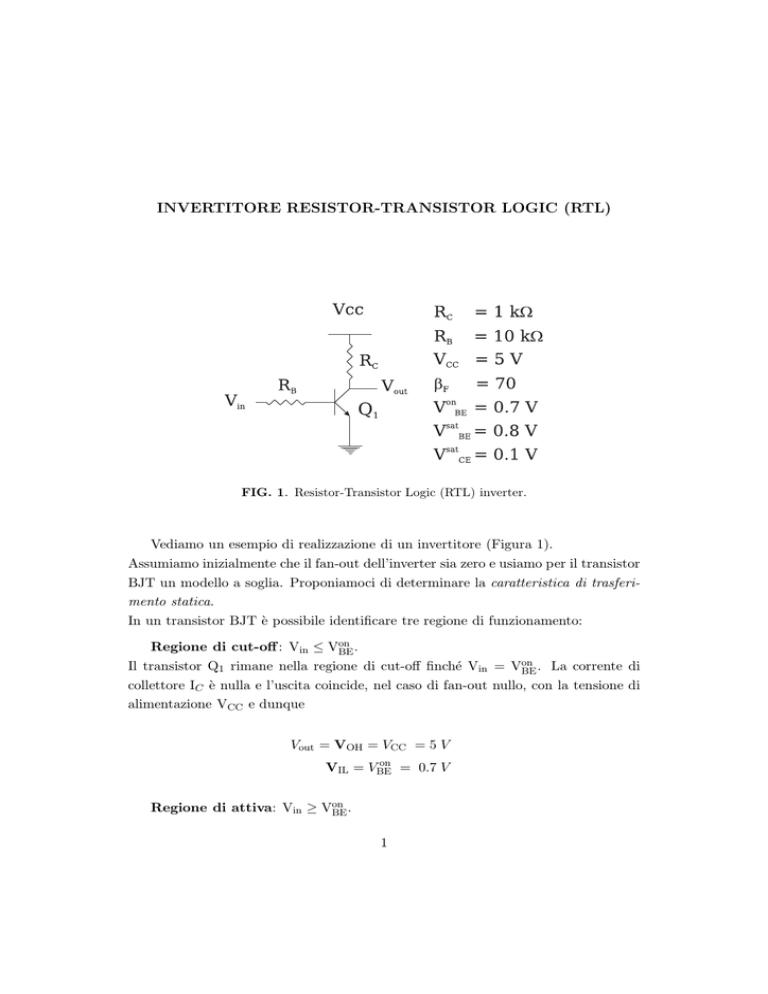

FIG. 1. Resistor-Transistor Logic (RTL) inverter.

Vediamo un esempio di realizzazione di un invertitore (Figura 1).

Assumiamo inizialmente che il fan-out dell’inverter sia zero e usiamo per il transistor

BJT un modello a soglia. Proponiamoci di determinare la caratteristica di trasferimento statica.

In un transistor BJT è possibile identificare tre regione di funzionamento:

Regione di cut-off : Vin ≤ Von

BE .

Il transistor Q1 rimane nella regione di cut-off finché Vin = Von

BE . La corrente di

collettore IC è nulla e l’uscita coincide, nel caso di fan-out nullo, con la tensione di

alimentazione VCC e dunque

Vout = VOH = VCC = 5 V

on

VIL = VBE

= 0.7 V

Regione di attiva: Vin ≥ Von

BE .

1

Corso di Circuiti Elettronici Digitali LA

2

on

Vin − VBE

,

RB

= βF IB ,

IB =

IC

Vout = VCC − βF IB RC = VCC − βF

RC

on

(Vin − VBE

)

RB

La tensione di uscita Vout decresce linearmente all’aumentare di Vin finché il transistor rimane nella regione attiva. Aumentando ulteriormente la corrente di base IB ,

il transistor raggiunge la

Regione di saturazione:VCE = Vsat

CE

La tensione che è neccessario applicare all’ingresso per mandare il transistor in

saturazione la si può calcolare nel modo seguente. Quando Q1 è sul bordo della

saturazione

sat

VCC − VCE

IC =

RC

ma è anche sul bordo della regione attiva diretta

IB =

sat

Vinsat − VBE

RB

segue che

sat

RB VCC − VCE

sat

sat

Vinsat = RB IB + VBE

+ VBE

=

=

RC

βF

10KΩ 5 − 0.1

=

+ 0.8 = 1.5 V

1KΩ

70

sat

Vout = VOH = VCE

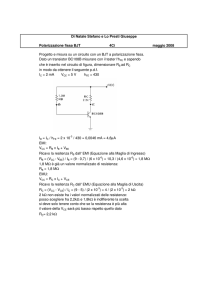

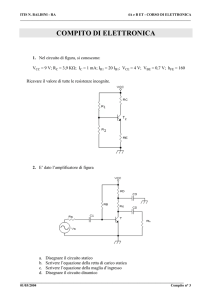

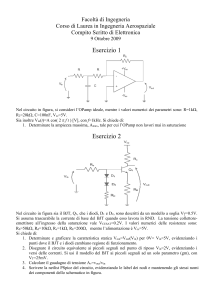

Riassumendo In Figura 2 è rappresentata la caratteristica dell’invertitore RTL.

A.A. 2006/2007

VIL

VIH

VOL

VOH

Von

BE

Vsat

in

Vsat

CE

VCC

0.7 V

1.5 V

0.1 V

5V

Corso di Circuiti Elettronici Digitali LA

3

NMH =VOH -VIH

3.5 V

NML =VOL -VIL

0.6 V

SW = VOH -VOL

4.9 V

Vout

VOH = VCC

Vin

soglia logica

Regione

Attiva

sat

VOL=VCE

on

VIL = VBE

Cutoff

sat

VIH = Vin

Vin

Saturazione

FIG. 2. Caratteristica di uscita statica dell’invertitore RTL.

POTENZA STATICA DISSIPATA

La potenza statica dissipata Pd si calcola mediante l’espressione

Pd = VIN IB + VDD IC

Dato che la corrente di base è tipicamente piccola rispetto a quella di collettore, la

dissipazione di potenza dovuta a IB può essere trascurabile.

Nel caso di uscita a livello logico alto, essendo nulla la corrente di collettore, nel

resistore RC non passa corrente e dunque la potenza statica è nulla

PdH = 0

Nel caso di uscita bassa, ovvero Vout = Vce = 0.1 V, la corrente richiesta al generatore

VCC è pari a

sat

VDD − VCE

5V − 0.1V

IC =

=

= 4.9 mA

RC

1KΩ

per cui la potenza statica dissipata è pari a:

PdL = VDD · IC = 24.5 mW

A.A. 2006/2007

Corso di Circuiti Elettronici Digitali LA

4

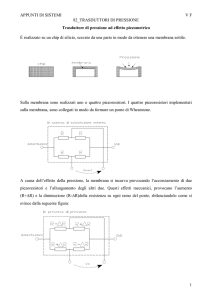

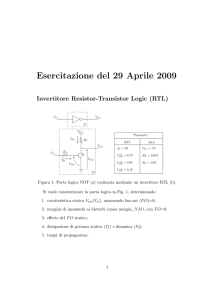

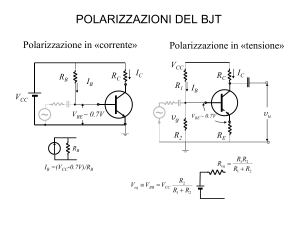

EFFETTO DEL FAN-OUT SULL’INVERTITORE RTL

FIG. 3. Rete logica con FA = 1

Il Fan-Out indica il numero massimo di circuiti di carico del medesimo tipo che

è possibile collegare all’uscita di porta logica.

Per un fan-out nullo si è ottenuto che

VOH = 5V

N MH

= 3.5V

Vediamo ora qual è l’effetto del fan-out su VOH . Il transistor Q2 lavora nella regione

di saturazione, per cui VBE (Q2 )=Vsat

BE , e dunque

RB

sat

(VCC − VBE

)=

RB + RC

10KΩ

= 0.8 +

(5 − 0.8) = 4.6 V

1KΩ + 10KΩ

L’applicazione di un gate all’uscita ha provocato una riduzione della tensione di

uscita da 5 V a 4.6 V e quindi

sat

VOH = VBE

+

N MH = VOH − VIH = 4.6 V − 1.5 V = 3.1 V

Supponiamo ora di collegare due porte logiche in uscita. In questo caso l’espressione

della corrente di base IB (si veda la Figura 4) è

sat

IB = VDD − VBE

RC + RB /2

mentre l’espressione della tensione di uscita del primo inverter è data da:

sat

VOH = VBE

+

RB

sat

(VCC − VBE

) = 4.3 V

RB /2 + RC

In questo caso il Margine di Immunità ai disturbi alto (NMH) si è ridotto a

A.A. 2006/2007

Corso di Circuiti Elettronici Digitali LA

5

FIG. 4. Rete logica con FA = 2

N MH = VOH − VIH = 4.3 V − 1.5 V = 2.8 V

Riassumendo:

FA=0

FA=1

FA=2

VOH

5V

4.6 V

4.3 V

MHH

3.5 V

3.1 V

2.8 V

Il numero massimo N di porte logiche che è possibile collegare in uscita si ha

quando il margine di immunità NMH = 0 e quindi

VOH = VIH

Quando Q1 è spento e sono presenti N gate in uscita, si ha il parallelo delle resistenze

di base RB (si veda la figura 5 e quindi si ha

sat

VBE

+ RB /N

sat

sat

VCC − VBE

RB VCC − VCE

=

RB /N + RC

RC

βF

Risolvendo in N si trova

N

N

sat

VCC − VBE

RB

sat − R

VCC − VCE

C

5.0 − 0.8 10

≤ 70

−

= 50

5.0 − 0.1

1

≤ βF

A.A. 2006/2007

Corso di Circuiti Elettronici Digitali LA

6

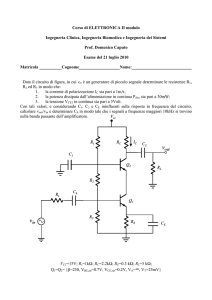

FIG. 5. Rete logica con FA = N

N = 0

N = 1

5

N = 2

3

V

OUT

(V)

4

2

1

0

0

1

2

3

V

IN

4

5

(V)

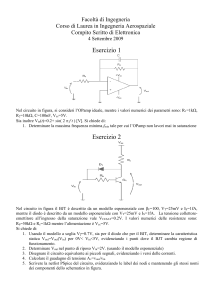

FIG. 6. Caratteristica statica con Fan Out non nullo.

La figura 6 mostra l’andamento della caratteristica statica in funzione del Fan-out.

A.A. 2006/2007

Corso di Circuiti Elettronici Digitali LA

7

ESERCIZIO

Che funzione realizza il circuito in figura 7?

FIG. 7.

Vi1

Vi2

Vout

L

L

H

L

H

L

H

L

L

H

K

L

A.A. 2006/2007