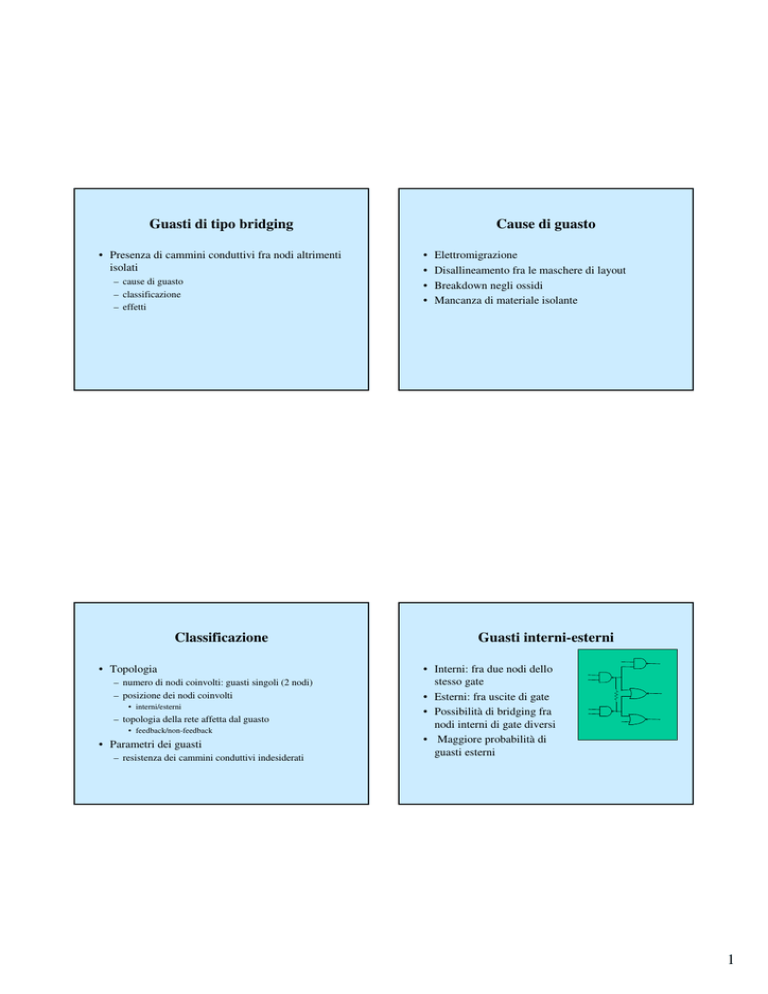

Guasti di tipo bridging

• Presenza di cammini conduttivi fra nodi altrimenti

isolati

– cause di guasto

– classificazione

– effetti

Classificazione

• Topologia

– numero di nodi coinvolti: guasti singoli (2 nodi)

– posizione dei nodi coinvolti

• interni/esterni

– topologia della rete affetta dal guasto

• feedback/non-feedback

• Parametri dei guasti

– resistenza dei cammini conduttivi indesiderati

Cause di guasto

•

•

•

•

Elettromigrazione

Disallineamento fra le maschere di layout

Breakdown negli ossidi

Mancanza di materiale isolante

Guasti interni-esterni

• Interni: fra due nodi dello

stesso gate

• Esterni: fra uscite di gate

• Possibilità di bridging fra

nodi interni di gate diversi

• Maggiore probabilità di

guasti esterni

1

Retroazione

• La presenza di retroazione può dare luogo a

comportamenti di tipo oscillatorio

fbf (non osc.)

Effetti dei bridging

•

•

•

•

Comportamento statico del circuito: errori logici

Assorbimento di corrente statica (CMOS)

Cambiamento delle prestazioni dinamiche

A ognuno di questi effetti corrisponde una tecnica

di testing per rivelarne la presenza

nfbf

fbf (osc.)

Condizioni di attivazione

Parametri

• Topologia della rete coinvolta

• Parametri elettrici di tale rete (dimensionamento

dei transistori)

• Tensione di alimentazione

• Temporizzazioni del circuito (frequenza di clock)

• Resistenza del bridging

(collaudo funzionale statico)

• I due nodi devono essere controllati a valori logici

diversi

• Effetto sulle tensioni di uscita dei gate

• Dipendono dal tipo di logica

– wired-and/or (nMOS, TTL)

– nei CMOS il comportamento è decisamente più

complesso:

•

•

•

•

tensione di alimentazione

resistenza del bridging

tipo di gate coinvolti

vettore applicato ai due gate

2

Valori di tensione intermedi nei

CMOS

Propagazione degli effetti del guasto

• Andamento in funzione della resistenza (R) del

bridging e dei vettori di attivazione

1

1

• Condizioni logiche: almeno uno dei due segnali

deve essere osservabile in uscita

• Condizioni elettriche: il segnale osservabile deve

dare luogo a un errore logico

V

a

11-00

Vdd

– i gate attraverso cui si propaga devono interpretare il

suo valore di tensione intermedio come un errore logico

(diverso da quello fault-free)

V(b)

Vtl

11-01

0

1/0

V(a)

R

b

Propagazione degli effetti dei guasti

• Dipende dal rapporto fra la soglia logica dei gate

nel fan-out e i valori di tensione intermedi

V

Vdd

a=0 b=0

V(b)

Vtl

a=0 b=1

V(a)

R

Propagazione degli effetti dei guasti

• Gli effetti del guasto

vanno propagati dal

1

segnale che assume un

1

valore diverso da

quello fault-free

• In alcuni casi i valori

di tensione intermedi 1

possono essere presenti 0

a più ingressi

1

a

1

0/0

prevale il valore

basso

?

1/0

0/1

b

0

errore logico

3

Propagazione degli errori

• Dopo un paio di livelli logici i valori intermedi

vengono normalizzati a valori logici normali

• A questo punto la propagazione degli effetti del

guasto è del tutto simile a quella di guasti di tipo

stuck-at

• Nelle reti sequenziali il problema può essere più

complesso

Generazione di vettori di collaudo

• Massimizzare lo sbilanciamento di conduttanze fra

le 2 reti cortocircuitate

• Propagare gli effetti del guasto dal gate con la

minore conduttanza di uscita

• Problema di quali gate nel fan-out utilizzare per la

propagazione

Problema della soglia logica

• La soglia logica dei vari gate è diversa da Vdd/2

ed è soggetta a forti fluttuazioni statistiche

• La soglia dipende sia dall’ingresso specifico di un

gate che dal vettore applicato al gate considerato

(AOI, OAI)

• Gate diversi possono interpretare valori di

tensione intermedi in modo diverso: byzantine

hardware fault model

• Questo avviene in maniera incognita

Problema della soglia logica

•

•

•

•

•

Si suppone di propagare gli

effetti del guasto a partire

dal gate a

Poiché il valore logico nel

circuito fault-free è 0,

bisogna che sia V(a)>VTL

Attraverso quale gate

propagare gli effetti del

guasto?

Chiaramente attraverso

quello con la soglia più

piccola

Tutti e due => problema

della riconvergenza

1

g

1

a

V(a)

1

h

0

1

V(b)

0

b

4

Effetti dinamici

• I bridging anche se non danno luogo a errori logici

possono dare luogo a rilevanti effetti dinamici

(ritardi addizionali)

• Un collaudo a bassa frequenza può non rivelare

tali guasti

• Alla frequenza operativa del circuito tali guasti

possono dare luogo a errori logici

• Gli effetti dinamici di un bridging possono

renderlo non rivelabile anche se lo sarebbe in

condizioni statiche

Effetti dinamici

V

Vdd

Il ritardo addizionale con cui

viene raggiunto il valore

intermedio può annullare la

rivelazione del guasto

faulty

Vtl

fault-free

t

V

Vdd

fault-free

Vtl

faulty

t

Indipendentemente dal

ritardo addizionale, il guasto

rivelabile staticamente

rimane rivelabile, il guasto

può essere rivelabile

dinamicamente anche se

non lo e’ staticamente

5