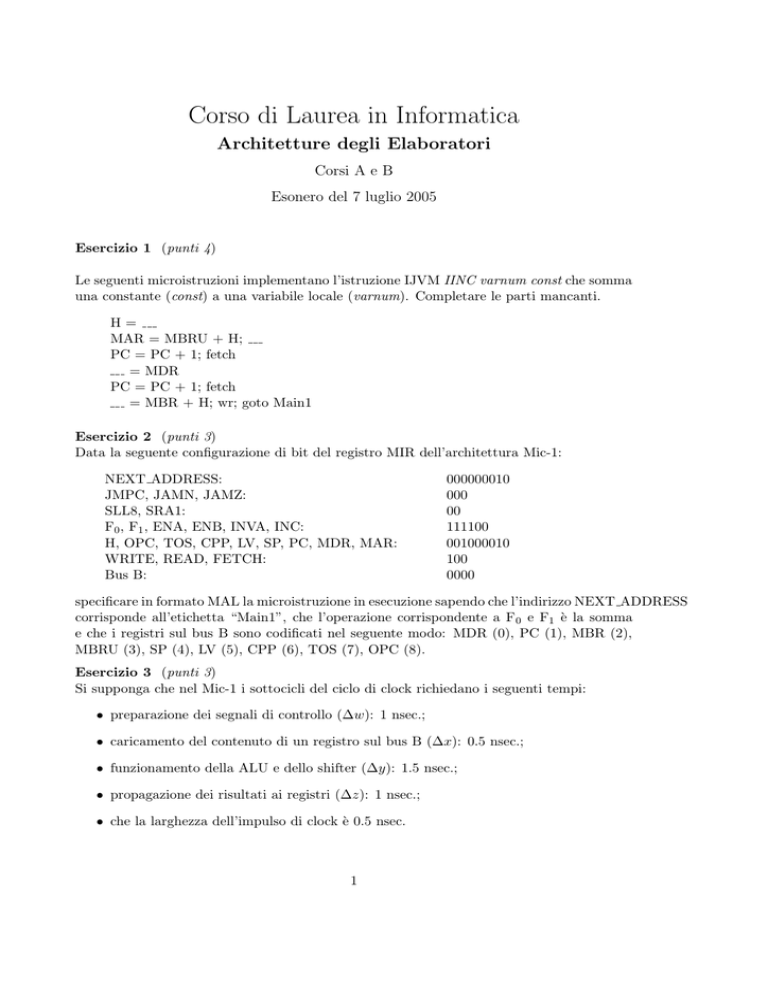

Corso di Laurea in Informatica

Architetture degli Elaboratori

Corsi A e B

Esonero del 7 luglio 2005

Esercizio 1 (punti 4)

Le seguenti microistruzioni implementano l’istruzione IJVM IINC varnum const che somma

una constante (const) a una variabile locale (varnum). Completare le parti mancanti.

H=

MAR = MBRU + H;

PC = PC + 1; fetch

= MDR

PC = PC + 1; fetch

= MBR + H; wr; goto Main1

Esercizio 2 (punti 3)

Data la seguente configurazione di bit del registro MIR dell’architettura Mic-1:

NEXT ADDRESS:

JMPC, JAMN, JAMZ:

SLL8, SRA1:

F0 , F1 , ENA, ENB, INVA, INC:

H, OPC, TOS, CPP, LV, SP, PC, MDR, MAR:

WRITE, READ, FETCH:

Bus B:

000000010

000

00

111100

001000010

100

0000

specificare in formato MAL la microistruzione in esecuzione sapendo che l’indirizzo NEXT ADDRESS

corrisponde all’etichetta “Main1”, che l’operazione corrispondente a F 0 e F1 è la somma

e che i registri sul bus B sono codificati nel seguente modo: MDR (0), PC (1), MBR (2),

MBRU (3), SP (4), LV (5), CPP (6), TOS (7), OPC (8).

Esercizio 3 (punti 3)

Si supponga che nel Mic-1 i sottocicli del ciclo di clock richiedano i seguenti tempi:

• preparazione dei segnali di controllo (∆w): 1 nsec.;

• caricamento del contenuto di un registro sul bus B (∆x): 0.5 nsec.;

• funzionamento della ALU e dello shifter (∆y): 1.5 nsec.;

• propagazione dei risultati ai registri (∆z): 1 nsec.;

• che la larghezza dell’impulso di clock è 0.5 nsec.

1

Questa macchina può funzionare a 100 MHz? 200 MHz? 300 MHz?

Esercizio 4 (punti 3+1)

Scrivere la sequenza di istruzioni IJVM tale che sia la traduzione corretta del frammento di

codice Java seguente e sapendo che le variabili x e y sono memorizzate nelle posizioni 1 e 2

nel frame di allocazione delle variabili locali :

x = x

if (x

x

y = y

<

=

-

y;

0)

0;

1;

Dire quanti byte occupa tale frammento di codice IJVM.

Esercizio 5 (punti 3)

Si consideri l’istruzione IJVM ISTORE varnum che effettua il pop di una parola dallo

stack e la memorizza in una variabile locale. Riordinare le seguenti microistruzioni affinché

implementino correttamente l’istruzione suddetta per l’architettura Mic-1.

1. MAR = MBRU + H

2. TOS = MDR; goto Main1

3. H = LV

4. PC = PC + 1; fetch

5. MDR = TOS; wr

6. SP = MAR = SP - 1; rd

Esercizio 6 (punti -1, 4)

Si considerino le varie modalità di indirizzamento.

a) Un esempio di indirizzamento di tipo immediato è quella dell’istruzione IJVM “BIPUSH 1”.

b) Un esempio di indirizzamento di tipo a stack (o zero indirizzi) è quella dell’istruzione

IJVM “GOTO L0”.

c) Nell’indirizzamento di tipo diretto l’indirizzo in memoria a cui reperire l’informazione

si determina sommando due valori di cui uno solitamente contenuto in un registro

mentre l’altro fornito nell’istruzione stessa.

d) Nell’indirizzamento di tipo indiretto l’indirizzo in memoria a cui reperire l’informazione

è contenuto nell’istruzione stessa.

e) Nell’indirizzamento di tipo indicizzato l’indirizzo in memoria a cui reperire l’informazione

si determina sommando due valori di cui uno solitamente contenuto in un registro

mentre l’altro fornito nell’istruzione stessa.

f) Un esempio di indirizzamento di tipo indicizzato è quella dell’istruzione IJVM “BIPUSH 1”.

2

Esercizio 7 (punti -1, 4)

Si consideri l’architettura denominata Mic-2.

a) Il control store contiene un numero di microistruzioni superiore rispetto all’architettura

Mic-1 ma inferiore in termini di lunghezza della singola microistruzione.

b) Il control store contiene un numero di microistruzioni inferiore rispetto all’architettura

Mic-1 ma superiore in termini di lunghezza della singola microistruzione.

c) Dispone di una unità per l’esecuzione in parallelo del caricamento delle istruzioni

(prefetch).

d) L’operando di sinistra dell’ALU (bus A) è implicito, in quanto fornito sempre dal

registro H.

e) L’ALU effettua l’incremento del registro PC per reperire l’istruzione successiva.

f) In generale, i tempi di preparazione dei segnali di controllo (∆w), di caricamento del

contenuto di un registro sul bus B (∆x), di funzionamento della ALU e dello shifter

(∆y), di propagazione dei risultati ai registri (∆z) e la larghezza dell’impulso di clock

sono assunti più brevi rispetto a quelli dell’architettura Mic-1.

Esercizio 8 (punti -1, 4)

Si considerino i calcolatori che implementano un instruction set di tipo CISC rispetto a

quello di tipo RISC.

a) In generale, i primi riescono a mettere in esecuzione un numero maggiore di istruzione

rispetto ai secondi a parità di tecnologia utilizzata.

b) In generale, i primi richiedono che gli operanti (sorgenti e destinazione) di gran parte

delle istruzioni siano forniti esclusivamente dai registtri.

c) In generale, nei secondi l’esecuzione delle istruzioni è divisa in molte fasi, ognuna

delle quali viene gestita da un pezzo di hardware dedicato in modo che tutto possa

funzionare in parallelo.

d) In generale, nei primi viene adottata la tecnica del pipeline per avviare un numero

maggiore di istruzioni in esecuzione rispetto ai secondi a parità di tecnologia utilizzata.

e) In generale, i secondi affidano al compilatore il lavoro di riorganizzare le istruzioni

affiché sia possibile sfruttare l’esecuzione parallela delle istruzioni (risoluzione delle

dipendenze tra istruzioni).

f) I calcolatori che implementano un instruction set di tipo RISC sono nati negli anni

’90.

Esercizio 9 (punti -1, 4)

Si consideri il processo di assemblaggio a due passi e il linguaggio assembler (o assembly).

a) Nel primo passo il processo di assemblaggio colleziona le informazioni riguardanti i

simboli di variabili e le etichette di salto presenti per programma assembler.

3

b) Ogni istruzione assembly ha una corrispondenza uno ad uno con le istruzioni a livello

ISA.

c) In generale, ogni istruzione assembly ha una corrispondenza uno a molti con le

istruzioni a livello ISA.

d) Compito del processo di assemblaggio è quello di sostituire ogni nome simbolico di

istruzione con il suo codice binario e di sostituire i riferimenti simbolici con riferimenti

binari.

e) Nel secondo passo il processo di assemblaggio colleziona le informazioni riguardanti i

simboli di variabili e le etichette di salto presenti per programma assembler.

f) Il processo di assemblaggio a due passi ha lo scopo di risolvere il problema del riferimento in avanti, ossia il riferimento ad un simboli la cui definizione avviene in un

secondo tempo.

4

Esonero di Architetture degli Elaboratori del 27/5/2005

MODULO RISPOSTE

Cognome:

Nome:

Matricola:

Corso:

1. (Punti 4)

H=

MAR = MBRU + H;

PC = PC + 1; fetch

= MDR

PC = PC + 1; fetch

= MBR + H; wr; goto Main1

2. (Punti 3)

Istruzione MAL:

3. (Punti 3)

100 MHz

200 MHz

300 Mhz

4. (Punti 3+1)

Codice:

Numero byte:

5. (Punti 3)

Sequenza corretta:

5

6. (Punti -1, 4)

a

b

c

d

e

f

c

d

e

f

c

d

e

f

c

d

e

f

7. (Punti -1, 4)

a

b

8. (Punti -1, 3)

a

b

9. (Punti -1, 4)

a

b

6

Esonero di Architetture degli Elaboratori del 7/7/2005

SOLUZIONI

Cognome:

Nome:

Matricola:

Corso:

1. (Punti 4)

H = LV

MAR = MBRU + H; rd

PC = PC + 1; fetch

H = MDR

PC = PC + 1; fetch

MDR = MBR + H; wr; goto Main1

2. (Punti 3)

Istruzione MAL: TOS = MDR = MDR + H; wr; goto Main1

3. (Punti 3)

100 MHz

200 MHz

4. (Punti 3+1)

Codice:

ILOAD 1

ILOAD 2

ISUB

ISTORE 1

ILOAD 1

IFLT L0

GOTO L1

L0: BIPUSH 0

ISTORE 1

L1: ILOAD 2

BIPUSH 1

ISUB

ISTORE 2

Numero byte: 26

5. (Punti 2)

Sequenza corretta: 3, 1, 5, 6, 4, 2

7

6. (Punti -1, 4)

a

e

7. (Punti -1, 4)

b

c

8. (Punti -1, 4)

c

e

9. (Punti -1, 4)

a

b

d

f

8