Istituto Professionale di Stato per l'Industria e l'Artigianato

MORETTO

Via Luigi Apollonio, 21 BRESCIA

Interfaccia tra PC e DAC

con scheda LX833

aspetti Hardware e Software

Realizzato da :

CREMASCHINI MICHELE

SCALVINI ALESSANDRO

classe 5BI TIEE

corso per Tecnici delle Industrie Elettriche ed Elettroniche

Docenti :

prof. Cleto Azzani

prof. Vitonofrio de Trizio

anno scolastico 1994-95

INTERFACCIA .............................................................................................................................................................. 3

SCHEMA ELETTRICO............................................................................................................................................... 3

GENERATORE DI FORME D'ONDA CON DAC0808. .......................................................................................... 5

CENNI SUL CIRCUITO ............................................................................................................................................... 5

CENNI SUI COMPONENTI UTILIZZATI.............................................................................................................................. 5

TRI-STATE O THREE-STATE ................................................................................................................................... 6

IL DAC0808................................................................................................................................................................. 6

CONVERTITORE DAC A 8 BIT R-2R ..................................................................................................................... 7

I PARAMETRI DI QUALITÀ DEI CONVERTITORI D-A. ........................................................................................................... 9

a) Risoluzione:.......................................................................................................................................................... 9

b) Tempo di assestamento (settling time): ................................................................................................................ 9

c) Glitch:............................................................................................................................................................... 9

GLI ERRORI NEI DAC. ............................................................................................................................................. 10

Errore di guadagno:............................................................................................................................................... 11

CONVERTITORE CORRENTE-TENSIONE.......................................................................................................... 11

SOFTWARE ................................................................................................................................................................. 11

FORME D'ONDA GENERATE ................................................................................................................................ 16

2

INTERFACCIA

Questo è un circuito che permette di svolgere azioni di controllo, pilotaggio e molte altre funzioni

comodamente seduti al proprio computer. L'interfaccia è una scheda che applicata ad un comune

PC, e corredata di un apposito software, ci dà la possibilità di :eccitare dei relè, accendere delle

lampade, pilotare l'accensione e lo spegnimento di caldaie, tener sotto controllo degli impianti di

antifurto e moltissime altre applicazioni.

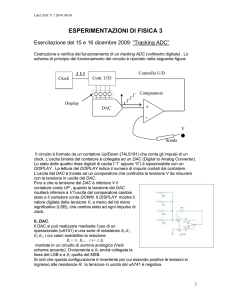

SCHEMA ELETTRICO

LOGICA DI

BUS PC/XT

CONTROLLO

A30

B14

A1

IOR

B13

A29

A31

IOW

A2

A0

U1

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

I1

I3

I2

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

EA1

ERD

U1

U3

U2

EWR

EA2

EA0

1G

2G

ECS

VCC

74LS244

LOGICA DI

R1

10K

SELEZIONE

A28

A27

A26

A25

A24

A23

A22

A11

U3

I0

I1

I2

I3

I4

I5

I6

I7

I8

I9

A3

A4

A5

A6

A7

A8

A9

AEN

F0

F1

F2

F3

F4

F5

F6

F7

R2

10K

R3

10K

R4

10K

CAMPO DI SELEZIONE

JP1-ON $300-$307

JP1

JP2

JP3

JP4

JP2-ON $308-$30F

JP3-ON $310-$317

PAL 16V8

JP4-ON $318-$31F

EP.833/1

BUFFER DATI

BIDIREZIONALE

A9

A8

A7

A6

A5

A4

A3

A2

U2

A1

A2

A3

A4

A5

A6

A7

A8

D0

D1

D2

D3

D4

D5

D6

D7

B1

B2

B3

B4

B5

B6

B7

B8

ED0

ED1

ED2

ED3

ED4

ED5

ED6

ED7

G

DIR

74LS245

+5V

B1

B31

C1

B7

-12V

B9

+12V

B3

B29

10uF

C2

C3

C4

100nF 100nF 100nF

C1, C2, C3 vanno connessi sui

GND pin di alimentazione di U1, U2, U3

+5V

fig. 1 Circuito scheda LX833 Nuova Elettronica

3

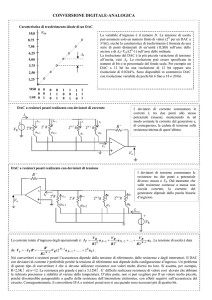

In figura 1 è riportato lo schema base dell'interfaccia sperimentale LX833. Esso é principalmente

costituito da tre integrati:

IC1=SN74LS244 buffer per amplificazione di indirizzi e segnali di controllo linea.

IC2=EP.833 PAL di transcodifica.

IC3=SN74LS245 buffer bidirezionale per dati.

Sull'area wrap (parte a bollini della scheda) è stato poi realizzato il nostro circuito sperimentale ,

"Generatore di forme d'onda " pilotato dal computer. Il circuito base preleva direttamente dal Bus

del Pc i segnali presenti sul Data-Bus (D0-D7) e sull'address bus(A0-A9).I segnali di controllo

sono : IOR , IOW , AEN . Sono presenti le tensioni di alimentazione ( + 5V , ± 12 V) utilizzate per

l'alimentazione del circuito. Analizzando il circuito in figura 1, abbiamo:

I segnali provenienti dal Bus del Pc

A0-A1-A2: rappresentano i primi tre bit del Bus degli indirizzi.

IOR : (Input Output Read),significa "lettura da un dispositivo Ingresso-Uscita".Ossia il computer

"leggerà" il dato sulla scheda solo quando IOR è a livello logico basso.

IOW : (Input Output Write),significa "scrittura verso un dispositivo Ingresso -Uscita". Il computer

scriverà sulla scheda un dato solo quando su questo terminale avremo un livello logico

basso.

AEN : (Address Enable),significa "Abilitazione dell'indirizzo".Quando su questo terminale è

presente un livello logico basso , significa che l'indirizzo presente in quell'istante sul BUS

è valido.

Segnale di selezione della scheda di espansione :

ECS: (Expansion Chip Select),significa "selezione della scheda di espansione". Questo segnale

fornisce l'abilitazione agli elementi circuitali presenti sulla scheda. Ciò avviene quando sul

bus degli indirizzi è presente uno degli indirizzi contenuti entro il gruppo selezionato dal

jumper chiuso. Il segnale ECS è attivo a livello basso.

Segnali presenti sulla scheda :

EDO-ED7 , rappresenta il data bus D0-D7 bufferizzato dall' integrato SN74LS245.

EA0-EA2 , indirizzi A0-A2 bufferizzati dall' integrato SN74LS244.

EWR , IOW bufferizzato dall' integrato SN74LS244

ERD , IOR bufferizzato dall' integrato SN74LS244

Cenni su alcuni integrati presenti sull'interfaccia

Descrizione delle funzioni svolte dai tre integrati:

SN74LS244: Questo integrato IC1 serve da Buffer per i segnali provenienti dal BUS degli

indirizzi,per i segnali di lettura e di scrittura dei dati,in modo da separare le linee del Bus principale

dai segnali portati all'esterno sulla scheda sperimentale.

4

EP388: Questo integrato IC2, è una PAL programmata, utile per decodificare gli indirizzi. E' un

integrato che è già stato programmato da Nuova Elettronica.In ingresso giungono tutti gli indirizzi

tranne i tre meno significativi (A0,A1,A2), ne deriva che l'abilitazione si attiverà su 8 indirizzi di

I/O contigui come riportato in figura 2.

fig.2

Jumper

Jp1

Jp2

Jp3

Jp4

CAMPO

$300-$307

$308-$30F

$310-$317

$318-$31F

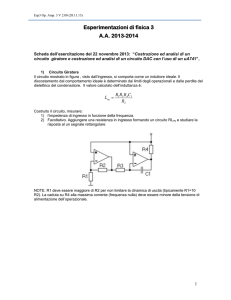

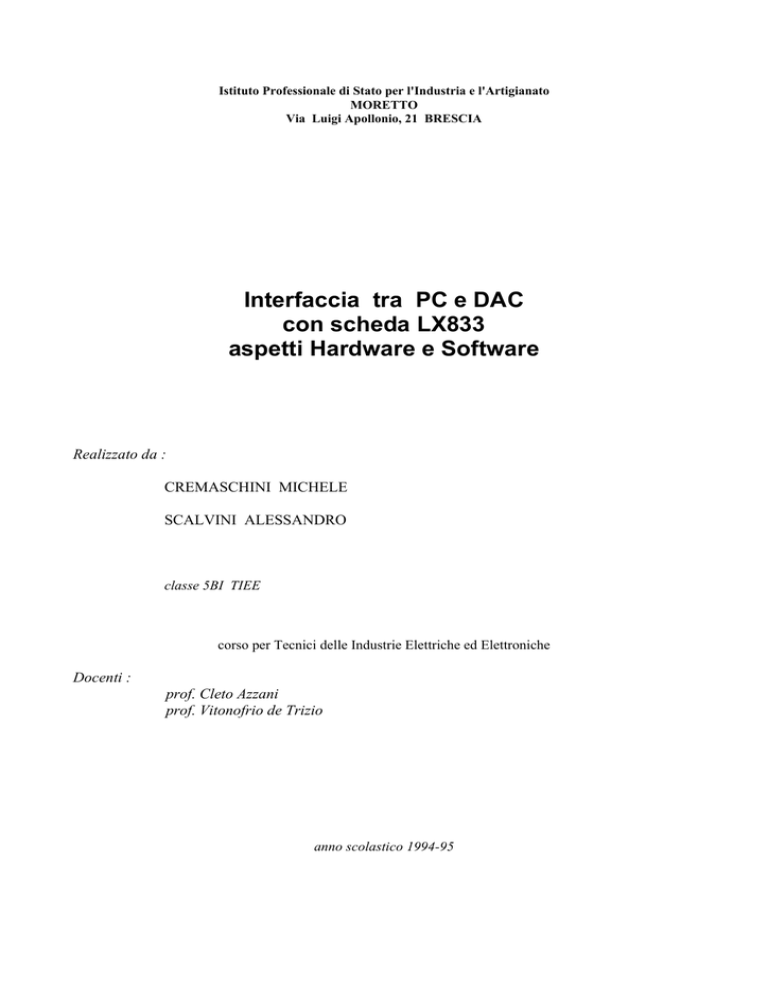

GENERATORE DI FORME D'ONDA con DAC0808.

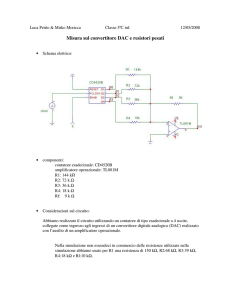

Il circuito realizzato sulla wrap(area a disposizione dell'utente) è formato principalmente dal

DAC0808, da un operazionale LM741 (in connessione convertitore I/V),da un 74LS374 (costituito

da 8 latch tri-state) e da un porta OR 74LS32.

VCC

VCC

A8

A7

A6

A5

A4

A3

A2

A1

VCC

VEE

GND

VOUT

IoW

EWR

JP1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

U2

D0

D1

D2

D3

D4

D5

D6

D7

U1

A8

A7

A6

A5

A4

A3

A2

A1

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

OC

CLK

VCC

OUT

IOUT

741

COMP

VR-

R3

IoR

U2

IOUT

VR+

74LS374

U3A

Rv

C4

100nF

C3

100nF

DAC0808

5,6K

R4

5,6K

C2

100nF

EWR

7432

fig. 3 Schema della interfaccia DAC

CENNI SUL CIRCUITO

Questo è un circuito che genera forme d'onda mediante la conversione, a mezzo DAC, di parole

digitali di n bit, che vengono generate dal microprocessore , mediante l'apposito software. IL DAC

dà in uscita una corrente che è proporzionale alla parola digitale in ingresso. Dato che a noi serve

una tensione d'uscita dobbiamo convertire la corrente in tensione; questa è realizzata mediante l'uso

di un apposito circuito utilizzante un operazionale.

L'utilizzo dell'integrato 74LS374 tri-state è dovuto al fatto che il DAC0808 non è direttamente

interfacciabile con il microprocessore . Questo circuito integrato provvede a memorizzare il dato

che proviene dal Data Bus del PC. Il segnale di clock di questo integrato viene ricavato con una

porta OR(74LS32) che combina i segnali EWR e ECS, entrambi attivi bassi.

Cenni sui componenti utilizzati.

IL 74LS374 è un registro parallelo a 8 bit e viene utilizzato come porta di collegamento. E' un

dispositivo tri-state ed è quindi direttamente interfacciabile con il microprocessore. In tal modo il

5

dato, che è presente solo per tempi inferiori al microsecondo, viene memorizzato dai flip-flop e

rimane disponibile per i dispositivi periferici.

TRI-STATE o THREE-STATE

La caratteristica Tri-State è utilizzata in generale per trasmettere informazioni (livelli logici)

provenienti da diverse sorgenti su un unico bus evitando conflitti. Introdotta nel 1970 dalla

National, questa può assumere 3 stati:

-due stati logici convenzionali (0 e 1)

-uno stato di alta impedenza (Hi-Z)

Il DAC0808

Questo è un convertitore digitale-analogico, (DAC è l'acronimo di Digital Analogic Converter),

Converte l'informazione binaria applicata in ingresso in una grandezza di tipo analogico (corrente

nel nostro caso). Il segnale analogico in uscita è proporzionale al valore numerico della parola

binaria applicata in ingresso.

Un convertitore D-A è formato dalle seguenti unità funzionali : un generatore di tensione o corrente

di riferimento(voltage reference), una rete resistiva (ladder) e un convertitore corrente tensione. La

tensione di riferimento ottenuta dal generatore di tensione ha un'influenza diretta sul valore della

tensione di uscita per cui deve essere estremamente precisa e stabile. Il convertitore correntetensione trasforma i livelli di corrente generati dalla rete resistiva in un segnale di tensione. Questo

elemento , in genere , non è presente nel microcircuito in quanto il segnale di uscita tipico dai DAC

è una corrente e quindi l'eventuale conversione corrente-tensione, viene effettuata da un circuito

esterno. Nel nostro caso il circuito di conversione è costituito da un operazionale che analizzerò poi.

L'equazione fondamentale di un convertitore digitale analogico è:

bn bn −1

b

+ 2 +... + 1n )

2

2

2

dove: Vu è la tensione d'uscita, Vref è la tensione di riferimento e bn-b1è la parola binaria

d'ingresso .Come si può dedurre dall'equazione 1 la tensione d'uscita del convertitore non ha un

valore continuo; infatti al variare del codice binario applicato in ingresso si ha, nella rete resistiva ,

una variazione di corrente discreta. Il nostro circuito si basa su questo principio per realizzare delle

forme. Il gradiente di tensione misurabile in uscita è pari a:

Vref

Vu = Vref (

2n

La risoluzione della conversione del numero digitale dipende dal numero di bit che compongono la

parola binaria in ingresso. Infatti dall'equazione 1 si deduce che il gradiente di tensione in uscita si

riduce in modo proporzionale all'aumento del numero di cifre binarie utilizzate in ingresso. La

precisione della conversione in questi convertitori dipende essenzialmente dalla precisione e dalla

stabilità del valore delle resistenze che compongono la rete resistiva. I convertitori digitaleanalogico vengono classificati in funzione della configurazione circuitale della rete resistiva

(ladder) utilizzata per convertire il segnale digitale. Le configurazioni piu' comuni sono:

-rete resistiva a resistenze pesate

-rete resistiva di tipo R-2R

Noi usiamo il DAC0808 che al suo interno contiene una rete resistiva R-2R.

6

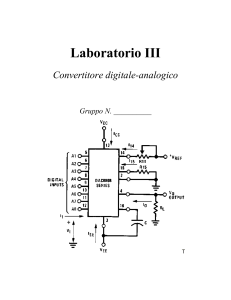

CONVERTITORE DAC A 8 BIT R-2R

In fig. 4 è riportato lo schema di un convertitore R-2R, con parola a 4 bit; esso è costituito da un

ladder di resistenze di valore R e 2R e da un amplificatore operazionale. Quattro switch elettronici

pilotati dai corispondenti bit della parola digitale di ingresso danno la possibilità di connettere i

quattro ingressi a Vref oppure a GND.

Per chiarire il funzionamento del circuito si fa riferimento ad un esempio.

Si determini il valore di tensione ottenibile in uscita del convertitore di fig. 4, quando all’ingresso

sia applicata la parola binaria:

C3

C2

0

1

C1

C0

0

1

si desidera una tensione di fondo scala in uscita Vr = Vfs = 10V.

Vref

1

0

1

0

1

0

1

0

2R

2R

N0

C0

R

2R

N1

C1

R

2R

N2

C1

3R

R

Is

2R

C3

2R

Vu

N3

fig. 4 RETE R-2R

E' semplice pervenire alla soluzione utilizzando il principio di sovrapposizione degli effetti, ovvero

ricavando la corrente Is prodotta da un solo deviatore alla volta allorché viene posto a “1” mentre

tutti gli altri sono posti a zero. Successivamente si ricaverà il risultato finale corrispondente ad una

parola binaria la sommando gli effetti prodotti dai suoi bit a “1”. In fig. 5 è riportata la

configurazione circuitale ottenuta con Co ad “1”, mentre tutti gli altri ingressi sono a “0”; per

semplicità sono stati eliminati i deviatori, sostituendoli con collegamenti. Si osservi che da ciascun

dei nodi esce, verso il convertitore corrente tensione, una corrente pari alla metà di quella entrante;

indicando con INI la corrente entrante nel nodo generico, si ha pertanto:

I Ni =

I N i−1

2

ovvero, nel caso di fig. 4:

IN3

I

I

I

IN 3 = N 2 IN 2 = N1 IN1 = N 0

2

2

2

2

In genere, il contributo dato alla corrente Is dal nodo ennesimo vale:

IS =

Is =

IN0

2n

(3)

si osservi che n esprime la posizione del nodo, valutata a partire dal convertitore, ovvero:

7

nodo

n

N3

1

N2

2

N1

3

N0

4

Nello schema in fig. 5, ogni nodo vede (verso il convertitore), il parallelo di due resistenze di valore

2R, ovvero una resistenza R; se ne conclude che:

IN0 =

Vref

3⋅ R

Applicando la (3), si ricava che, con il solo commutatore Co a 1 e gli altri a zero, la corrente Is

risulta:

IS =

In generale :

Is =

Vr

Vref

1

3R 24

⋅

Vref ⎛ 1

1

1⎞

⎜C0 n + C1 n−1 +...+Cn−1 1 ⎟

3R ⎝ 2

2

2⎠

2R

2R

N0

R

2R

N1

R

2R

3R

N2

R

2R

2R

N3

Is

-

Vo

+

Fig. 5 Convertitori di tipo R-2R

Nel caso della parola binaria data:

Is =

Vref ⎛ 1

1

1

1 ⎞ Vref

⎜1 ⋅ 4 + 0⋅ 3 + 1⋅ 2 + 0 ⋅ 1 ⎟ =

⋅ 0,3125

3R ⎝ 2

2

2

2 ⎠ 3⋅ R

Ricordando che nel convertitore corrente-tensione risulta:

Vu = − I s ⋅ 3R → Vu = 10⋅ 0,3125 = 3125

, V

8

I parametri di qualità dei convertitori D-A.

a) Risoluzione:

costituisce l’unico parametro dei DAC analizzato fino ad ora; rappresenta il livello di tensione

d’uscita, corrispondente al bit meno significativo (LSB) della parola da convertire. E’ legato alla

tensione di riferimento, dalla relazione:

1

1

ovvero

Vref n [V ]

R(% ) = n ⋅ 100

2

2

L’espressione della risoluzione, formulata come sopra, è riferita al valore di Vr che, come si è visto,

può può essere modificato per esigenza d’impiego del DAC. I costruttori preferiscono pertanto

definire la risoluzione come numero n di bit, fornendo cioè una grandezza che di fatto è legata al

valore relativo della risoluzione dalla relazione:

n = lg 2

100

R( % )

Secondo tale modalità, si riportano in tabella i valori di risoluzione di alcuni componenti

commerciali:

DAC 0800

n

8 bits

DAC 0808

DAC 0830

DAC 1000

DAC 1230

8 bits

8 bits

10 bits

12 bits

b) Tempo di assestamento (settling time):

è il tempo che intercorre tra l’applicazione di una parola binaria all’ingresso e la disponibilità,

all’uscita, della tensione ad essa corrispondente, con il minimo errore possibile. Il minimo errore

possibile ha in genere valori pari a metà del peso del bit meno significativo. Per comprendere

appieno il significato della definizione, si osservi che un DAC si comporta come un qualsiasi

sistema ai cui ingressi vengono applicati dei gradini, corrispondenti ai bit di parola che cambiano

di stato nel passaggio dal codice attuale al precedente. La presenza di componenti reattivi

all’interno di un DAC, determina un comportamento dinamico nella presenza ai gradini, che può

esaurirsi in modo aperiodico smorzato (esponenziale), oppure periodico smorzato (sinusoide a

smorzamento esponenziale d’ampiezza), in funzione dello stato dei poli della funzione di

trasferimento. In tale condizione, il tempo di assestamento, rappresenta l’intervallo di tempo tra

l’istante in cui vengono applicati i gradini corrispondenti alla parola d’ingresso e quello in cui

l’uscita rimane all’interno della fascia ε = 1 / 2 LSB, che rappresenta il valore accettabile per il

sistema. Nella maggior parte dei convertitori commerciali, gli elementi reattivi hanno valori tali da

dar luogo a risposte periodiche smorzate. Questo significa che le costanti di tempo sono tali da

determinare poli complessi coniugati a parte reale negativa della f di t del sistema. E’ immediato

comprendere che il tempo di assestamento, a parità di DAC, dipende dal numero di bit della parola.

Si riportano in tabella i tempi di assestamento di alcuni componenti commerciali:

Ta

DAC 0800

DAC 0808

DAC 0830

DAC 1000

DAC 1230

100 nsec

150 nsec

1microsec

500 nsec

1 microsec

c) Glitch:

9

è l’insieme delle sovratensioni transitorie che si sovrappongono ai livelli di tensione dei singoli bit

della parola da convertire.

Il glitch dipende da due cause:

-i diversi tempi di commutazione delle porte di trasmissione;

·-le costanti di tempo del circuito.

E’ evidente che ogni bit di parola che cambia stato rispetto alla parola precedentemente convertita,

contribuisce alla formazione del glitch complessivo, in modo dipendente dalla porta di trasmissione

che lo gestisce e dalle parti circuitali che attraversa.

L’unico accorgimento che consente di ridurre l’effetto del glitch, è l’impiego di un circuito di

sample-hold all’uscita del convertitore; l’effetto del sample-hold è infatti quello di mantenere

stabile per un certo tempo il livello di segnale decodificato. Poiché il glitch costituisce un

transitorio di breve durata, si può ritenere che sia contenuto entro il tempo di assestamento, pertanto

è sufficiente che il sample-hold prelevi la tensione allorché è assestata, per ridurre notevolmente gli

effetti del glitch.

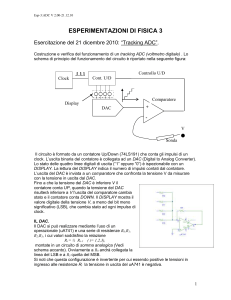

Gli errori nei DAC.

Si esamina l’effetto degli errori nei DAC, unendo la definizione alla rappresentazione grafica sulla

caratteristica di trasferimento. La linearità di un DAC è la conservazione della proporzionalità tra

entità della variazione del codice digitale d’ingresso e corrispondente variazione della grandezza di

uscita in ogni punto nel campo di conversione. La linearità ideale di un DAC corrisponde ad un

insieme di punti, dato che il codice digitale d’ingresso (Ni) assume valori discreti, giacenti su una

stessa retta: in fig. 7a è riportato il caso relativo ad un DAC a 3 bit, nell’ipotesi che la grandezza di

uscita sia una tensione Vu. In pratica, tale parametro, nei dispositivi disponibili sul mercato, viene

specificato come inferiore a ½ LSB. La linearità di un DAC dipende principalmente dalla

precisione e dal grado di variazione con la temperatura dei valori di resistenza della sua rete

resistiva. Il fatto che il valore di linearità non ecceda il valore 1/2 LSB è importante per la

conservazione della monotonicità del DAC: questa caratteristica indica che al crescere del valore

del segnale digitale d’ingresso (Ni), si ha un aumento della grandezza di uscita, mentre al

decrescere del valore Ni deve aversi una diminuzione del segnale d’uscita. Supponiamo d’ora in

avanti, ed è il caso più comune, che la grandezza d’uscita sia una tensione Vu: se l’errore di

linearità fosse superiore a 1/2 LSB potrebbe accadere che, detta Vu1 la tensione convertita relativa

al numero digitale N1, al numero N2 = N1 +1 (incremento di un LSB) corrisponde una tensione

Vu2 < Vu1 , nel caso gli errori fossero di segno opposto, positivo per Vu1 e negativo per Vu2, e di

valore assoluto superiore a 1/2 LSB , si ottiene una conseguente perdita della monotonicità.

L’accuratezza è il grado in cui la tensione d’uscita del convertitore si avvicina alla Vu di un DAC

ideale. La risposta di un DAC ideale (tensione a gradino di fig. 7a) incontra la retta congiungente lo

zero con il valore di fondo scala nel punto mediano di ogni gradino di bit. I principali fattori che

influenzano tale parametro sono: l’errore di linearità, le oscillazioni della tensione di riferimento e

le variazioni di guadagno dell’amplificatore operazionale presenti nel convertitore. La sensibilità

termica è il grado in cui la Vu del DAC varia per effetto solo della variazione di temperatura, cioè a

parità di segnale digitale (N1) d’ingresso. Il tempo di stabilizzazione è l’intervallo di tempo

intercorrente tra la variazione del segnale digitale d’ingresso e il corrispondente raggiungimento da

parte della Vu del valore finale Vuf, a meno di un prefissato piccolo errore percentuale: p.es 0,5%

dal valore di fondo scala. In fig. 7b, to è l’istante di tempo a partire dal quale Vu rientra nella

tolleranza stabilita: risulta quindi che il tempo di stabilizzazione sia uguale a: 0 L’oscillazione della

Vu è causata da vari fattori, tra cui la configurazioni spurie momentaneamente presenti agli ingressi

del DAC p.es nel passaggio da 0111 a 1000 per un convertitore a quattro bit.

10

Vu

Vu

7

6

5

4

3

2

1

Vuf

Vui

Ni

000

001

010

011

(a) linearita'

100

101

110

t di stabilizzazione

to

111

t^1

t

(b) stabilizzazione

F1g. 7a-b

Errore di guadagno:

è una tensione d’uscita pari al fondo scala e l’effettivo codice che produce il fondo scala. la

differenza (nominalmente espressa in LSB) tra il codice d’ingresso che dovrebbe dar luogo ad una

tensione d'uscita pari al fondo scala e l'effettivo codice che produce il fondo scala.

CONVERTITORE CORRENTE-TENSIONE

Con gli amplificatori operazionali si possono realizzare i convertitori corrente-tensione

(current-voltage conversion).Il convertitore I-V presenta in uscita una tensione che è

linearmente dipendente dalla corrente in ingresso Ie. La relazione che lega la tensione di uscita

Vo e la corrente di ingresso vale:

V0 = − Rv ⋅ I

SOFTWARE

Il software di gestione dell'interfaccia è stato redatto in ambiente Turbo Pascal 5.5. Con questo

programma sono state create le forme d'onda riportate in fondo alla relazione:onda QUADRA,

TRIANGOLARE, SINUSOIDALE e RAMPA. Con semplici comandi si possono creare forme d'onda

di qualsiasi tipo lasciando libero sfogo alla propria immaginazione. Quelle da noi create sono le piu'

basilari : onda quadra , triangolare, a rampa e sinusoidale.

Prima di utilizzare l'interfaccia nelle sue complete funzioni , abbiamo testato la basetta nei punti

più' importanti , quali il pin di ECS, EWR, ERD ed il clock del 74LS374.

Si è iniziato con un semplice programma, che doveva fare eseguire ripetutamente al processore

operazioni di scrittura sulla scheda di interfaccia; attraverso un oscilloscopio abbiamo controllato

l'andamento nel tempo del segnale EWR .

11

Procedure WRITEDAC; { Programma di test scheda in modo WRITE }

Begin

REPEAT

port[DAC]:=$00; { Scrittura dalla scheda DAC }

UNTIL FALSE;

End;

L'operazione svolta dal programma è di semplice comprensione. Concettualmente il computer non

fa altro che scrivere 0 sul port di scrittura . Il loop serve per ottenere un segnale continuo e quindi

visualizzabile sull'oscilloscopio. La forma d'onda in uscita è riportata in figura.

Come si nota dal grafico, il segnale EWR è attivo basso. Lo stesso principio è stato usato per il

programma di lettura qui riportato:

Procedure READ; { Programma di test scheda in modo READ }

var

H:byte;

Begin

REPEAT

H:=port[DAC]; { Lettura dalla scheda DAC }

UNTIL FALSE;

End;

12

In figura si nota il segnale ERD , di durata maggiore dell' EWR , anch'esso attivo basso.Prendiamo

in esame ora la creazione di un onda triangolare.

Procedure TRIANGOLARE;

Begin

REPEAT

DATO:=0;

REPEAT

{ fase crescente: 255 campioni}

port[DAC]:=Dato;

Dato:=Dato+1;

UNTIL DATO=255;

REPEAT

{ fase decrescente: 255 campioni}

port[DAC]:=Dato;

Dato:=Dato-1;

UNTIL DATO=0;

Until FALSE;

END;

In questa procedura viene creata l'onda triangolare semplicemente facendo incrementare una

variabile (Dato) che poi viene portata in uscita. Questo incremento si ripete fino a che non si

raggiunge il numero 255; poi si ha il passaggio al loop successivo che svolge la funzione di

decremento fino a che non raggiunge lo 0. Dopo di che ricomincerà da capo realizzando così

l'onda in figura .

13

PROGRAM INTERFACCIA (INPUT,OUTPUT);

USES CRT;

VAR

K : INTEGER;

ADDR,DAC : WORD;

Dato : byte;

Dato1 : real;

X : array[0..255] of byte;

Procedure READ; { Programma di test scheda in modo READ }

var

H:byte;

Begin

REPEAT

H:=port[DAC]; { Lettura dalla scheda DAC }

UNTIL FALSE;

End;

Procedure WRITEDAC; { Programma di test scheda in modo WRITE }

Begin

REPEAT

port[DAC]:=$00; { Scrittura dalla scheda DAC }

UNTIL FALSE;

End;

Procedure CALIBDAC;

Begin

Gotoxy(10,15); Write(' Numero per DAC (0-255) ');

Readln(Dato);

port[Dac]:=Dato;

End;

14

Procedure RAMPA;

BEGIN

Repeat

DATO:=0;

REPEAT

port[DAC]:=Dato;

Dato:=Dato+1;

UNTIL DATO=255;

Until FALSE;

END;

Procedure TRIANGOLARE;

Begin

REPEAT

DATO:=0;

REPEAT

port[DAC]:=Dato;

Dato:=Dato+1;

UNTIL DATO=255;

REPEAT

port[DAC]:=Dato;

Dato:=Dato-1;

UNTIL DATO=0;

Until FALSE;

END;

Procedure QUADRA;

Begin

REPEAT

DATO:=0;

port[DAC]:=DATO;

Delay(1);

DATO:=255;

port[DAC]:=dato;

Delay(1);

UNTIL FALSE;

END;

Procedure SINE;

var k,n:integer;

Begin

k:=0;

n:=255;

repeat

DATO1:=128+127*sin(2*Pi/n*k);

x[k]:=round(DATO1);

k:=k+1;

UNTIL k=256;

REPEAT

k:=0;

15

repeat

port[DAC]:=x[k];

k:=k+1;

UNTIL k=256;

UNTIL FALSE;

END;

BEGIN { PROGRAMMA PRINCIPALE }

ClrScr;

ADDR:=$300; { $300-$307 campo di indirizzamento della scheda }

DAC := ADDR;

Repeat

ClrScr;

Gotoxy(10,1); write('INTERFACCIA LX-833 ');

Gotoxy(10,3); WRITE('1- TEST DAC READ MODE ');

Gotoxy(10,5); WRITE('2- TEST DAC WRITE MODE ');

Gotoxy(10,7); WRITE('3- Calibrazione DAC ');

Gotoxy(10,9); write('4- RAMPA ');

Gotoxy(10,11); write('5- TRIANGOLARE ');

Gotoxy(10,13); write('6- QUADRA ');

Gotoxy(10,15); write('7- SINUSOIDALE ');

Gotoxy(10,20); WRITE('0-FINE');

Gotoxy(11,22); Readln(k);

Case K of

1: READ;

2: WRITEDAC;

3: Calibdac;

4: RAMPA;

5: TRIANGOLARE;

6: QUADRA;

7: SINE;

End;

until K=0;

END.

(segue)

FORME D'ONDA GENERATE

Con il programma sopra indicato abbiamo generato anche le seguenti forme d'onda;. mediante

'interfacciamento con un oscilloscopio HP54600B tra il circuito e il computer è stato possibile

riportare nella relazione le forme d'onda seguenti.

16

FIG.1 forma d'onda rilevata su ECS

FIG.2 forma d'onda rilevata su ll'uscita della OR, clock del 74LS374.

17

FIG.3 forma d'onda d'uscita con programma RAMPA.

FIG.4 forma d'onda d'uscita con programma QUADRA.

18

FIG.5 forma d'onda d'uscita con programma SINUSOIDE.

19