TESTI DI ESERCIZI PER LA PRIMA PROVA IN ITINERE - ANNO 20010-11

CONVERTITORI A/D

1Un segnale analogico compreso tra 0 e 10 V deve essere digitalizzato con un errore

di quantizzazione minore di 0.5 mV.

a) Determinare quanti bit deve avere il convertitore analogico digitale.

b) Si supponga di utilizzare per il convertitore analogico digitale in questione un

convertitore a doppia rampa: se ne disegni lo schema e se ne spieghi il funzionamento.

c) Specificare quale legge di quantizzazione utilizza il convertitore del punto precedente e,

supponendo di poter trattare l’errore di quantizzazione come una variabile aleatoria

uniformemente distribuita nell’intervallo di quantizzazione, se ne determini il valor medio

ed il valore quadratico medio.

2Disegnare lo schema di principio di un convertitore analogico digitale di tipo flash ad

8 bit che consenta la conversione di segnali con dinamica tra 0 e VFS e che utilizzi la

strategia di quantizzazione per arrotondamento.

a) Spiegarne il funzionamento

b) Calcolare il massimo rapporto segnale rumore ottenibile con questo dispositivo in caso

di ingresso sinusoidale e considerando il solo rumore di quantizzazione.

3Si progetti un convertitore AD a doppia rampa con 16 bit di risoluzione, per segnali

negativi con fondo scala di -10 V. Si progetti il sistema in modo da reiettare il rumore in

ingresso a 50 Hz, ed in modo cha la tensione di picco in uscita all'integratore sia pari a

15V quando in ingresso si ha la tensione di fondo scala. In dettaglio:

a) disegnare lo schema del circuito da realizzare e spiegarne sinteticamente il

funzionamento

b) determinare la frequenza massima del segnale di clock con cui può funzionare il

convertitore ed il corrispondente valore della costante di tempo dell’integratore,

compatibilmente con le specifiche.

c) Discutere quali sono la potenza ed il valor medio del rumore di quantizzazione in uscita

dal convertitore; discutere inoltre quale attenuazione ci si può aspettare per un rumore

additivo in ingresso alla frequenza di 1 kHz.

d) Indicare quale è la frequenza massima dei segnali che è possibile convertire con il

dispositivo progettato.

4Si disegni lo schema di un convertitore A/D doppia rampa a 12 bit per la

conversione di segnali con banda massima di 100 Hz e valori compresi

nell’intervallo (0 V, -10 V), spiegandone il funzionamento. Indicare anche quali

sono la frequenza minima del segnale di clock del circuito, il valore minimo della

costante di tempo dell’integratore utilizzabile se si utilizzano amplificatori

operazionali rail to rail alimentati con ±10 V, ed il massimo valore dell’errore di

quantizzazione ottenuto.

5Un segnale analogico compreso tra 0 e 10 V deve essere digitalizzato con un errore

di quantizzazione minore del 1% del fondo scala. a) Quanti bit sono necessari?

b) Si supponga di utilizzare per il convertitore analogico digitale in questione una

configurazione a distribuzione di carica: se ne disegni lo schema e se spieghi il

funzionamento.

c) Specificare quale legge di quantizzazione utilizza il convertitore del punto precedente e,

supponendo di poter trattare l’errore di quantizzazione come una variabile aleatoria

uniformemente distribuita nell’intervallo di quantizzazione, se ne determini il valor medio

ed il valore quadratico medio.

CIRCUITI NON LINEARI CON A.O.

1Disegnare lo schema di un raddrizzatore a doppia semionda con amplificatori

operazionali

(AO) e diodi e spiegarne il funzionamento nell’ipotesi di AO ideali. Spiegare inoltre quali

vantaggi comporta l’utilizzo di questo circuito rispetto ad un normale ponte a diodi. A

questo scopo si consideri che gli AO abbiano guadagno finito reale A0 e che i diodi

abbiano tensione di soglia Vγ.

2Disegnare lo schema di un raddrizzatore di precisione a singola semionda senza

saturazione con diodo ed amplificatore operazionale, e ricavare la relazione tra

tensione di uscita e tensione di ingresso nell’ipotesi che il diodo si comporti come

un circuito aperto per VD < Vγ = 0.6 V, e come un cortocircuito per VD ≥ Vγ.

Discutere i vantaggi di questa configurazione rispetto ad un raddrizzatore a

semplice semionda senza operazionale.

CIRCUITI ASTABILI E MONOSTABILI, COMPARATORE CON ISTERESI

1Si disegni il circuito di un multivibratore monostabile basato amplificatore

operazionale

(AO) e diodi, in grado di generare impulsi negativi, e se ne discuta il funzionamento

supponendo ideali sia l’AO che i diodi (Vγ=0V).

Dimensionare il circuito affinchè la durata degli impulsi sia 5 ms e la minima tensione

sul morsetto invertente dell’operazionale sia Vmin = -10 V. A questo scopo si

suppongano ancora ideali i diodi e l’AO. Si supponga inoltre che l’AO sia rail to rail e

sia alimentato con ±15 V.

2Si supponga di avere a disposizione amplificatori operazionali rail to rail ideali con

tensioni di alimentazione ± 15 V. Disegnare lo schema di un circuito che utilizzi due dei

suddetti

amplificatori operazionali, e che sia in grado di generare onde triangolari alla frequenza di

10 kHz, valor medio di 5 V, ampiezza picco-picco di 10 V, duty cycle del 50%, e discuterne

il funzionamento.

3Disegnare lo schema di un generatore di onda triangolare che utilizzi come

componenti attivi due amplificatori operazionali, discutendone analiticamente il

funzionamento

b) Dimensionare il circuito, supponendo di utilizzare amplificatori operazionali ‘rail to rail’

alimentati a ±15 V, perché le forme d’onda generate abbiano valor medio nullo, periodo

di 2 kHz e duty cycle del 50%.

c) Modificare il circuito e ripetere il dimensionamento affinché le forme d’onda generate

abbiano periodo di 2 kHz e duty cycle del 75%.

4Disegnare lo schema di un multivibratore monostabile basato su amplificatore

operazionale e spiegarne analiticamente il funzionamento. Fornire inoltre un

dimensionamento del circuito perchè questo sia in grado di fornire impulsi positivi della

durata di 100 ms.

5Progettare un generatore di onda triangolare con valor medio nullo, ampiezza

picco-picco

di 10 V, duty cycle del 50%, frequenza di 20 kHz, utilizzando solo componenti passivi e

amplificatori operazionali ‘rail to rail’ alimentati tra ±15V. Nel rispondere a questa domanda

riportare lo schema del circuito progettato e l’andamento temporale delle tensioni di tutti i

nodi che presentino una tensione non costante. Ricavare inoltre tutte le relazioni che si

utilizzano nel dimensionamento del generatore.

b) Modificare il circuito progettato al punto a) affinchè l’onda triangolare presenti un valor

medio di 5 V.

c) Modificare il circuito progettato al punto a) per avere un duty cycle del 75%.

6Si progetti un trigger di Schmitt invertente utilizzando un amplificatore operazionale

rail to rail alimentato tra +12 V e -12V, in modo che presenti un ciclo di isteresi di 8 V con

valor medio di 4 V. (riportare lo schema circuitale e la caratteristica tensione di uscita –

tensione di ingresso del trigger)

b) Modificare il circuito progettato aggiungendo una resistenza di 10kΩ ed una capacità di

10 nF in modo da ottenere un multivibratore astabile. Quale è il duty cycle della forma

d’onda generata da questo circuito? (riportare gli andamenti temporali delle tensioni dei

nodi del circuito variabili nel tempo)

7Disegnare lo schema di un oscillatore generatore di onda triangolare, discutendone

analiticamente il funzionamento.

Dimensionare il circuito, supponendo di utilizzare amplificatori operazionali ‘rail to rail’

alimentati a ±10 V, perché le forme d’onda generate abbiano valor medio nullo e periodo

di 1 kHz.

Ripetere il dimensionamento affinché le forme d’onda generate abbiano valor medio di 1

V.

8Si progetti un trigger di Schmitt con ciclo di isteresi simmetrico di 10V utilizzando un

amplificatore operazionale ‘rail to rail’ alimentato tra ±15V.

Modificare il circuito per avere soglie di scatto L+=10V ed L-=0V.

AMPLIFICATORI LINEARI CON A.O.

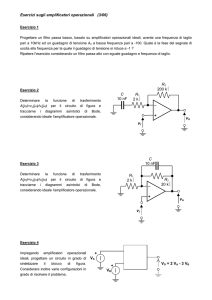

1Si consideri un amplificatore operazionale (AO) in configurazione non invertente

con guadagno in DC uguale a 16 dB (a meno dell’errore introdotto dal guadagno finito

dell’AO), realizzato con un amplificatore operazionale rail to rail alimentato tra ± 10 V con

le seguenti caratteristiche: guadagno a singolo polo, GBW=1MHz, fH=10 Hz, Rid= 10 7 Ω,

Ro=50 Ω,

Bpp = 10 Hz.

a) Disegnare lo schema del circuito dimensionando le resistenze affinchè la rete di

retroazione assorba una corrente inferiore a 100 μA.

b) Tracciare i diagrammi di Bode del modulo e della fase del guadagno di anello βA

c) Calcolare le resistenze Rif ed Rof.

d) Se con il circuito in questione si amplifica un segnale sinusoidale con frequenza di

500 kHz, quale è la massima ampiezza del segnale di ingresso all’amplificatore

perchè il segnale di uscita non presenti distorsione non lineare?

2Si supponga di avere a disposizione amplificatori operazionali rail to rail alimentati

tra ± 15 V che abbiano le seguenti caratteristiche: Rid = 1 MΩ, fT = 2 MHz, Av0 =100 dB.

a) Progettare un amplificatore, realizzato con uno o più stadi identici, che abbiano:

guadagno in continua │Av0f │= 40 dB, fHf > 100 kHz, Rinf <15 kΩ.

b) Quale deve essere lo SR minimo degli operazionali se si vuole un banda a piena

potenza di 100 kHz?

c) Supponendo per gli operazionali una tensione di offset di ingresso V IO = 1 mV, quale è

la tensione massima in uscita dall’amplificatore in assenza di segnale di ingresso?

3Progettare un amplificatore che presenti │Av0f│= 24, fHf ≥ 35 kHz, Rinf ≤ 2 kΩ, Rof ≤

0.5Ω, avendo a disposizione amplificatori operazionali con le seguenti caratteristiche: R id =

1GΩ, Ro = 25 Ω, fT = 1 MHz, Av0 =100 dB. Nel rispondere a questa domanda riportare lo

schema del circuito progettato e verificare il soddisfacimento di tutte le specifiche.

b) Calcolare il prodotto guadagno-larghezza di banda dell’amplificatore progettato.

c) Si supponga di inviare in ingresso all’amplificatore progettato al punto a) tre segnali

sinusoidali di ampiezza 0.5 V e frequenza rispettivamente 10 kHz, 40 kHz e 100 kHz: che

ampiezza presentano i tre segnali all’uscita dell’amplificatore? (si supponga che gli

amplificatori operazionali utilizzati siano rail to rail con alimentazione ±15V)

d) Si supponga che gli amplificatori operazionali utilizzati abbiano correnti di

polarizzazione I+=I-=I di valore non nullo. Modificare il circuito progettato al punto a)

perchè dette correnti di polarizzazione non abbiano effetto sull’uscita dell’amplificatore

(giustificare il risultato analiticamente).

e) Valutare la massima ampiezza di un segnale sinusoidale con frequenza di 100 kHz

applicato in ingresso all’amplificatore per avere in uscita un segnale sinusoidale non

distorto. Si ipotizzi che gli amplificatori operazionali utilizzati abbiano slew rate = 1V/μs.

4A quale frequenza un amplificatore non invertente con guadagno in DC pari a 10

compie un errore del 5% se l’amplificatore operazionale con cui è realizzato presenta un

comportamento a singolo polo, un GBW = 1 MHz ed un guadagno in continua di 80 dB?

(riportare lo schema del circuito ed il diagramma di Bode dell’ampiezza per l’operazionale

ad anello aperto e per l’amplificatore retroazionato).

5Progettare un circuito che, mediante un amplificatore operazionale, realizzi la

seguente funzione:

Vo(t)=3V1(t) + 5V2(t)

Supponendo che l’amplificatore operazionale utilizzato sia ‘rail to rail’, sia alimentato tra

±15V ed abbia uno ‘slew rate’ di 1V/μs, determinare la banda a piena potenza del

dispositivo.

Siano V1(t)=0 e V2(t)=Asin(2π104t). Quale è la massima ampiezza A per non avere

distorsione non lineare in uscita?