Applicazioni Industriali

delle sorgenti di Radiazioni Ionizzanti

(Charge Collection in MOSFETs

and SEU in SRAM)

Andrea Candelori

Istituto Nazionale di Fisica Nucleare and Dipartimento di Fisica, Padova

1

Ion Induced Charge Collection in MOSFET

(Raccolta di carica dovuta all’impatto di uno ione in

un MOSFET)

2

Ion-triggered channeling (ITC) in MOSFET

Uno ione incidente su un MOSFET in condizione OFF, può perturbare il campo elettrico interno al

dispositivo ed indurre un canale conduttivo (stato di conduzione) tra source e drain:

tale fenomeno viene chiamato Ion-triggered channeling ITC.

Layout del dispositivo

(MOSFET a canale n in condizione OFF:

VG<VT=0.9V)

per le simulazioni 3D

Layout del dispositivo

(singola giunzione p-n)

per le simulazioni 3D

Referenza: S. Velacheri, L. W. Massengill and S. E. Kerns, "Single-Event-Induced Charge Collection and Direct Channel

3

Conduction in Submicron MOSFETS“, IEEE TNS, vol. 41, n. 6, December 1994, pp. 2103-2111.

Ion-triggered channeling (ITC) in MOSFET

Layout del dispositivo (MOSFET a canale n in condizione OFF: VGS<VT=0.9V) per le simulazioni 3D

e sue curve caratteristiche (IDS-VGS e IDS-VDS al variare di VGS)

4

Ion-triggered channeling (ITC) in MOSFET

Q =q·n·L·r2

n=1019 e/h cm-3

r=0.15 m

Linear charge density

q n r 2 1.602 10 19 C 1019

L=0.5 m

e/h

pC

2

3

.

14

0

.

15

m

0

.

11

cm3

m

Carica generata: Q=q·n·L·r2=55 fC

MOSFET nella condizione OFF: VGS<VT

Risultato delle simulazioni: I.

Carica raccolta al drain: QD =59 fC>Q:

1) aumento della carica raccolta al drain (elettroni) rispetto alla giunzione

p-n (drain-bulk) e quindi dovuto alla presenza del source. Questa corrente

tenderebbe a scaricare un nodo floating carico positivamente connesso al

drain.

2) la corrente di substrato è negativa: la carica raccolta (lacune) dal

contatto di bulk è minore della carica raccolta dal contatto di drain;

3) la corrente al source è negativa (elettroni) ovvero si ha una corrente (di

5

drift di elettroni) uscente dal source che viene raccolta al drain.

Ion-triggered channeling (ITC) in MOSFET

Q =q·n·L·r2

n=1019 e/h cm-3

r=0.15 m

Linear charge density

q n r 2 1.602 10 19 C 1019

L=0.5 m

e/h

pC

2

3

.

14

0

.

15

m

0

.

11

cm3

m

Carica generata: Q=q·n·L·r2=55 fC:

MOSFET nella condizione OFF: VGS<VT

Risultato delle simulazioni: II.

N+

P

N+

Potenziale nel canale alla profondità di 0.1 m:

1) Gli elettroni si muovono verso punti a potenziale crescente.

2) Le lacune si muovono verso punti a potenziale decrescente.

3) Dopo 1 ps dall’impatto dello ione la barriera di potenziale per gli

elettroni tra Source (O V) e Drain (3.3 V) è annullata (collasso del campo

elettrico per funneling nel MOSFET con conseguente corto circuito tra

source e drain), per cui si ha una corrente di drift di elettroni nel canale tra

source e drain: il MOSFET si viene a trovare in condizione ON. La

barriera di potenziale tra Source e Drain inizia a riformarsi dopo 19 ps

dall’impatto dello ione.

4) Il fenomeno è diverso da quello dell’attivazione del BJT parassita

source-emettitore (n), bulk-base (p), drain-collettore (n) con iniezione di

elettroni dall’emettitore (source) alla base (bulk) per diffusione e raccolta

6

al drain (collettore).

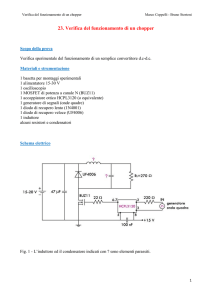

Ion-triggered channeling (ITC) in MOSFET

Confronto della simulazioni tra MOSFET e giunzione p-n (bulk-drain)

Layout del dispositivo

(MOSFET a canale n in condizione OFF:

VG<VT=0.9V)

per le simulazioni 3D

Layout del dispositivo

(singola giunzione p-n)

per le simulazioni 3D

Carica generata dalo ione incidente Q= 55 fC

Carica raccolta all’impianto n+ (drain)

del MOSFET: Q= 59 fC

Carica raccolta all’impiato n+:

della giunzione p-n: Q= 49 fC

7

Ion-triggered channeling (ITC) in MOSFET

Carica generata Q= 55 fC

Carica raccolta Q= 59 fC

All’aumentare del drogaggio del source, la carica raccolta

al drain del MOSFET aumenta rispetto ala carica raccolta

alla giunzione pn (dal 10% al 49%)

Carica raccolta Q= 49 fC

All’aumentare della lunghezza della traccia dello ione, e quindi della

carica generata dallo ione incidente, aumenta la carica raccolta al

drain del MOSFET rispetto alla carica raccolta dalla giunzione pn (dal

23 al 351%)

8

Ion-triggered channeling (ITC) in MOSFET

MOSFET a canale corto

MOSFET a canale lungo

L’effetto della formazione del canale conduttivo tra source e drain vale solo per i MOSFET a canale corto

N+

P

N+

N+

P

N+

9

Ion-triggered channeling (ITC) in MOSFET

MOSFET a canale corto

Carica generata Q= 55 fC

All’aumentare del drogaggio del source, la carica raccolta

al drain del MOSFET aumenta rispetto alla carica raccolta

all’impianto n+ della giunzione pn

(dal 10% al 49%)

MOSFET a canale lungo

Tale effetto non è rilevabile

nel caso di un MOSFET a canale lungo

10

Ion-triggered channeling (ITC) in MOSFET

Effetto dell’inclinazione dello ione

Caratteristiche della simulazione

-Source doping: 5·1020 cm-3

-VS=0V VD=3 V VG=0V VB=0V

-Ion track length: 0.5 m

-Charge generated by the ion: Q=55 fC

N+

Carica raccolta al drain al variare

dell’angolo di incidenza dello ione

(la carica generata dallo ione è 55 fC)

P

N+

Potenziale nel canale alla profonsità di 11

1 m

per un angolo di incidenza dello ione di 45º

Ion-triggered channeling (ITC) in MOSFET

Effetto dell’inclinazione dello ione

Caratteristiche della simulazione

-Source doping: 5·1020 cm-3

-VS=0V VD=3 V VG=0V VB=0V

-Ion track length: 0.5 m

-Charge generated by the ion: Q=55 fC

Carica raccolta al drain al variare

dell’angolo di incidenza dello ione

(la carica generata dallo ione è 55 fC)

Corrente ai contatti di Drain, Source e Substrato

12

per un angolo di incidenza dello ione di 45º

Ion-triggered channeling (ITC) in MOSFET

MOSFET a canale corto

Carica generata Q= 55 fC

All’aumentare dell’angolo di incidenza, la carica raccolta

al drain del MOSFET aumenta rispetto alla carica raccolta

all’impianto n+ della giunzione pn

(dal 46% al 470%)

MOSFET a canale lungo

Tale effetto non è rilevabile

nel caso di un MOSFET a canale lungo

13

Ion-triggered channeling (ITC) in MOSFET

Uno ione incidente su un MOSFET in condizione OFF, può perturbare il campo elettrico interno al

dispositivo ed indurre un canale conduttivo (stato di conduzione) tra source e drain:

tale fenomeno viene chiamato Ion-triggered channeling ITC.

L’ITC avviene non solo se lo ione colpisce il drain del dispositivo ma anche se lo ione impatta sul

dispositivo al centro del canale.

Corrente ai contatti di Drain, Source e Substrato per uno ione che colpisce il dispositivo tra Source e

Drain. Drogaggio del Source 5·1020 cm-3. Carica raccolta dal drain 56 fC. Carica raccolta

dall’impianto p+ della giunzione p-n: 46 fC. Aumento della carica raccolta per il MOSFET rispetto 14

alla

giunzione p-n del 33%

Ion-triggered channeling (ITC) in MOSFET

Conclusioni

-l’ITC (Ion-triggered channeling) è un processo che causa un aumento della carica raccolta al Drain del

MOSFET, rispetto alla carica generata dallo ione incidente o alla carica raccolta all’impianto p+ di una

giunzione p-n nelle medesime condizioni operative;

-l’ITC avviene nei MOSFET a canale corto sub-micrometrici, mentre non è osservabile nei MOSFET

con lunghezza del canale superiore al micrometro;

-a causa dell’impatto dello ione il campo elettrico all’interno del dispositivo viene perturbato: la barriera

di potenziale tra Source e Drain per un MOSFET in condizione OFF viene annullata, si presenta un

gradiente di potenziale tra Source e Drain che causa una corrente di drift di elettroni (per un MOSFET a

canale n) tra Source e Drain. Si viene quindi a creare un corto-circuito tra Source e Drain ed è come se il

MOSFET venisse a trovarsi nella condizione ON;

-all’aumentare dell’angolo di incidenza il fenomeno viene rafforzato;

-il fenomeno si verifica non solo se lo ione incide sul MOSFET al Drain, ma anche se lo ione incide sul

MOSFET al centro del canale.

15

Ion-triggered channeling (ITC) in MOSFET: approfondimento

1) Fase di Funneling (1-10 ps): dopo 1 ps dall’impatto dello ione su un MOSFET a canale n in

condizione OFF (VS=VG=VB=0 e VD>0), la barriera di potenziale per gli elettroni tra Source e Drain si

annulla ed è presente un campo elettrico tra Source e Drain: il MOSFET viene a trovarsi in una

condizione di conduzione tra Source e Drain ovvero in condizione ON. Dopo 10 ps la barriera di

potenziale tra Source e Drain viene a riformarsi anche se la sua altezza è inferiore alle condizioni

stazionarie.

2) Fase Bipolare (10-50 ps): la corrente di elettroni tra Source e Drain continua a fluire anche dopo il

riformarsi della barriera di potenziale tra Source e Drain: gli elettroni infatti passano sulla barriera di

potenziale della giunzione p-n che si è riformata ma che è minore rispetto alle condizioni stazionarie. Il

meccanismo è analogo a quello della conduzione sottosoglia di un MOSFET, in cui gli elettroni

fluiscono (portatori minoritari) fluiscono tra source e drain superando la barriera di potenziale della

giunzione p-n del canale ovvero source- substrato (conduzione bipolare).

3) Fase di Diffusione (>50 ps). In questa fase è predominante la corrente di elettroni tra Source e Drain

dovuta alla diffusione dei portatori: tale corrente decresce nel tempo fino ad annullarsi con il reinstaurarsi delle condizioni di equilibrio.

Referenze: E. Takeda et al., “A Cross Section of -Particle-Induced Soft-Errors Phenomena in VLSI’s“, IEEE TNS, vol.

36, n. 11, November 1989, pp. 2567-2579, Section VIII; G. Gasiot, D. Giot and P. Roche, “Alpha-Induced Multiple Cell

166,

Upsets in Standard and Radiation Hardened SRAMs Manufactured in a 65 CMOS Technology“, IEEE TNS, vol. 53, n.

December 2006, pp. 3479-3486, Fig.12.

Ion-triggered channeling (ITC) in MOSFET: approfondimento

1) Fase di Funneling (1-10 ps): dopo 1 ps dall’impatto dello ione su un MOSFET a canale n

in condizione OFF (VS=VG=VB=0 e VD>0), la barriera di potenziale per gli elettroni tra

Source e Drain si annulla ed è presente un campo elettrico tra Source e Drain: il MOSFET

viene a trovarsi in una condizione di conduzione tra Source e Drain ovvero in condizione

ON. Dopo 10 ps la barriera di potenziale tra Source e Drain viene a riformarsi anche se la

sua altezza è inferiore alle condizioni stazionarie.

17

Ion-triggered channeling (ITC) in MOSFET: approfondimento

2) Fase Bipolare (10-50 ps): la corrente di

elettroni tra Source e Drain continua a fluire

anche dopo il riformarsi della barriera di

potenziale tra Source e Drain: gli elettroni

infatti passano sulla barriera di potenziale

della giunzione p-n che si è riformata ma che

è minore rispetto alle condizioni stazionarie.

Il meccanismo è analogo a quello della

conduzione sottosoglia di un MOSFET, in cui

gli elettroni (portatori minoritari) fluiscono

tra source e drain superando la barriera di

potenziale della giunzione p-n sourcesubstrato (conduzione bipolare).

18

Giunzione p-n

Polarizzazione

diretta

Polarizzazione

inversa

19

BJT (Transistor bipolare a giunzione)

n

p

n

All’equilibrio termico

ni

2.25 10 20 cm 6

p

2.25 10 4 cm 3

16

3

n

10 cm

2

n

2.25 10 20 cm 6

p i

2.25 1014 cm 3

6

3

n

10 cm

2

20

BJT (Transistor bipolare a giunzione)

n

p

n

+

+

-

-

Entrambe le giunzioni polarizzate inversamente

ni

2.25 10 20 cm 6

p

2.25 10 4 cm 3

16

3

n

10 cm

2

pn ni

2

21

BJT (Transistor bipolare a giunzione)

n

p

n

Entrambe le giunzioni polarizzate direttamente

ni

2.25 10 20 cm 6

p

2.25 10 4 cm 3

16

3

n

10 cm

2

pn ni

2

22

BJT (Transistor bipolare a giunzione)

n

p

n

+

-

Giunzione BE polarizzata direttamente e giunzione BC polarizzata inversamente

ni

2.25 10 20 cm 6

p

2.25 10 4 cm 3

16

3

n

10 cm

2

pn ni

2

pn ni

2

23

BJT (Transistor bipolare a giunzione)

Diffusione

E: Emettitore

B: base

C: Collettore

Giunzione BE polarizzata direttamente:

i portatori minoritari (per la base) ovvero gli

elettroni (e) per diffusione attraversano la

regione di svuotamento emettitore-base e la

base fino a giungere alla regione di

svuotamento della giunzione base-collettore.

Drift

p

n

n

e

+

-

Giunzione BC polarizzata inversamente: tali

elettroni se raggiungono la regione di

svuotamento della giunzione BC per drift

possono raggiungere il collettore.

Referenza: R. Muller e T. I. Kamins, Dispositivi Elettronici nei circuiti intergrati, Bollati Boringhieri

24

Single Event Upset (SEU) in SRAM

25

MOSFET a canale p ed n con VG=VCC>0

VG,P-MOSFET=VCC>0 => OFF

S

VG,N-MOSFET=VCC>0 => ON

D

http://tams-www.informatik.uni-hamburg.de/applets/cmos/cmosdemo.html

26

MOSFET a canale p ed n con VG=VCC>0

VG,P-MOSFET=GND=0 => ON

S

VG,N-MOSFET=GND=0 => OFF

D

27

http://tams-www.informatik.uni-hamburg.de/applets/cmos/cmosdemo.html

CMOS Inverter

VG,P-MOSFET=VCC>0 => OFF

Da "1" a "0"

VG,N-MOSFET=VCC>0 => ON

VG,P-MOSFET= GND=0 => ON

Da "0" a "1"

VG,N-MOSFET = GND=0 => OFF

28

CMOS Inverter

S

VG,P-MOSFET=VCC>0 => OFF

Da "1" a "0"

D

VG,N-MOSFET=VCC>0 => ON

29

http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/05-switched/40-cmos/inverter.html

CMOS Inverter

S

VG,P-MOSFET= GND=0 => ON

Da "0" a "1"

D

VG,N-MOSFET = GND=0 => OFF

30

http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/05-switched/40-cmos/inverter.html

Memoria SRAM: operazione di scrittura "1"

Data line: write value "1" if high or "0" if low

Data line: Enable writing if low

Word line address selection if high

S

P-ON

S

P-OFF

Writing operation "1"

D

D

N-ON

N-OFF

Bit line

(written or

stored value "1")

Bit line

(written or

stored value "0")

31

http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/05-switched/40-cmos/sramcell.html

Memoria SRAM: valore immagazzinato "1"

Data line: Write value "1" if high or "0" if low

Data line: enable writing if low

Word line address selection if high

S

P-ON

S

P-OFF

Stored value "1"

D

D

N-OFF

Bit line

(floating)

N-ON

Bit line

(floating)

32

http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/05-switched/40-cmos/sramcell.html

Memoria SRAM: valore immagazzinato "1": SEE (Parte 1a)

Data line: Write value "1" if high or "0" if low

Data line: enable writing if low

Word line address selection if high

S

P-ON

S

SEE: the p-MOSFET

status changes from OFF to

ON: what happens?

P-OFF

Store value "1"

D

D

N-ON

N-OFF

Bit line

(floating)

Bit line

(floating)

33

Memoria SRAM: valore immagazzinato "1": SEE (Parte 2a)

Data line: Write value "1" if high or "0" if low

Data line: enable writing if low

Word line address selection if high

S

3a) P-OFF

SEE: the p-MOSFET

status changes from OFF to

ON: what happens?

S

1) P-ON

Stored value from "1" to "0"

2) "H"

4) L

D

D

5) N-OFF

3b) N-ON

Bit line

(floating)

Bit line

(floating)

34

Memoria SRAM: valore immagazzinato "1": SEE (Parte 3a)

Data line: Write value "1" if high or "0" if low

Data line: enable writing if low

Word line address selection if high

S

SEE: the p-MOSFET

status changes from OFF to

ON: what happens?

S

3) P-OFF

1) P-ON

Stored value from "1" to "0"

2) "H"

5) L

D

D

6) N-OFF

4) N-ON

Bit line

(floating)

Bit line

(floating)

35

Memoria SRAM: valore immagazzinato "1": SEE (Parte 4a)

Data line: Write value "1" if high or "0" if low

Data line: enable writing if low

Word line address selection if high

S

3) P-OFF

SEE: the p-MOSFET

status changes from OFF to

ON: what happens?

S

1) P-ON

Stored value from "1" to "0"

2) "H"

5) L

D

D

6) N-OFF

4) N-ON

Bit line

(written or

stored value "0")

Bit line

(written or

stored value "1")

36

Memoria SRAM: operazione di scrittura "0"

Data line (Write value "1" if high or "0" if low)

Data line (Enable writing if low)

Word line address selection if high

S

S

P-OFF

P-ON

Writing operation "0"

D

Bit line

(written or

stored value "0")

D

N-ON

N-OFF

Bit line

(written or

stored value "1")

37

http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/05-switched/40-cmos/sramcell.html

Memoria SRAM: valore immagazzinato "0"

Data line: Write value "1" if high or "0" if low

Data line: enable writing if low

Word line address selection if high

S

P-OFF

S

P-ON

Stored value "0"

D

D

N-ON

Bit line

(floating)

N-OFF

Bit line

(floating)

38

http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/05-switched/40-cmos/sramcell.html

Memoria SRAM: valore immagazzinato "0": SEE (Parte 1b)

Data line: Write value "1" if high or "0" if low

Data line: enable writing if low

Word line address selection if high

SEE: the n-MOSFET

status changes from OFF to

ON: what happens?

S

P-OFF

S

P-ON

Stored value from "0" to "1"

D

D

N-ON

Bit line

(floating)

N-OFF

Bit line

(floating)

39

Memoria SRAM: valore immagazzinato "0": SEE (Parte 2b)

Data line: Write value "1" if high or "0" if low

Data line: enable writing if low

Word line address selection if high

SEE: the n-MOSFET

status changes from OFF to

ON: what happens?

S

3a) P-ON

S

5) P-OFF

4) H

Stored value from "0" to "1"

D

2) “L"

D

1) N-ON

Bit line

(floating)

3a) N-OFF

Bit line

(floating)

40

Memoria SRAM: valore immagazzinato "0": SEE (Parte 3b)

Data line: Write value "1" if high or "0" if low

Data line: enable writing if low

Word line address selection if high

SEE: the n-MOSFET

status changes from OFF to

ON: what happens?

S

3a) P-ON

S

5) P-OFF

4) H

Stored value from "0" to "1"

D

2) “L"

D

1) N-ON

Bit line

(floating)

3a) N-OFF

Bit line

(floating)

41

Memoria SRAM: valore immagazzinato "0": SEE (Parte 4b)

Data line: Write value "1" if high or "0" if low

Data line: enable writing if low

Word line address selection if high

SEE: the n-MOSFET

status changes from OFF to

ON: what happens?

S

3a) P-ON

S

5) P-OFF

4) H

Stored value from "0" to "1"

D

2) “L"

D

1) N-ON

Bit line

(written or

stored value "1")

3a) N-OFF

Bit line

(written or

stored value "0")

42

Memoria SRAM: valore immagazzinato "0": SEE (Parte 4b)

Esempio dell’andamento della tensione al drain per l’ n-MOSFET con il canale in condizione OFF a

seguito dell’impatto con uno ione: LET 40.5 MeV·cm2/mg sottosoglia.

43

Memoria SRAM: ricapitolazione I

La parte sensibile del dispositivo sono i MOSFET nello stato OFF: se un transistor

nello stato OFF a causa di un SEE va a portarsi anche temporaneamente nello stato ON si

può avere un SEU nella cella di memoria.

La sensibilità è maggiore per gli n-MOSFET.

44

Memoria SRAM: ricapitolazione II

La parte sensibile del dispositivo sono i MOSFET nello stato OFF: se un transistor

nello stato OFF a causa di un SEE va a portarsi anche temporaneamente nello stato ON si

può avere un SEU nella cella di memoria.

La sensibilità è maggiore per gli n-MOSFET.

45

Memoria SRAM: dallo Schematico al Layout

Schematico

NMOS access transistor

PMOS

Layout

NMOS

Inverter #1

Inverter #2

PMOS

NMOS

NMOS access transistor

46

Memoria SRAM: dal Layout alla simulazione 3D

Layout

NMOS access transistor

Simulazione 3D

NMOS access transistor

IEEE TNS, vol. 48, n. 6, December 2001, pp.1893-1903, "SEU-Sensitive Volumes in Bulk and SOI SRAMs From FirstPrinciples Calculations and Experiments", P. E. Dodd, M. R. Shaneyfelt, K. M. Horn, D. S. Walsh, G. L. Hash, T. A. Hill, B. L.

47

Draper, J. R. Schwank, F. W. Sexton, and P. S. Winokur.

Memoria SRAM: area del dispositivo sensibile (sezione d’urto)

PMOS-ON

PMOS-OFF

S D

D S

S D

D S

NMOS-OFF

NMOS-ON

NMOS access transistor

Quali sono le parti sensibili al SEU della

cella di memoria SRAM, all’aumentare del

valore di LET dello ione incidente?

48

Memoria SRAM: curva -LET dalle simulazioni

ON

OFF

OFF

ON

Upset cross section of the

device: value from a cell

multiplied by the number

of cells (256k)

49

Memoria SRAM: curva -LET simulazioni e dati sperimentali

Upset cross section of the

device: value from a cell

multiplied by the number

of cells (8k)

50

Memoria SRAM: analisi con un microfascio

LET dello ione incidente:16 MeV·cm2/mg.

Le regioni sensibili al SEU sono solo i drain degli n-MOSFET in condizione OFF.

ON

OFF

OFF

ON

Simulazione 3D

Microfascio

51

Memoria SRAM: analisi con un microbeam

ON

OFF

NMOS

access

PMOS

NMOS

ON

OFF

NMOS

access

OFF

ON

OFF

ON

ON

OFF

ON

OFF

NMOS

access

PMOS

NMOS

NMOS

access

52

OFF

ON

OFF

ON

Memoria SRAM: analisi con un microbeam

OFF

ON

NMOS

PMOS

ON

OFF

Micromapping della SRAM "TDSRAM05" in condizione di saturazione della sezione d’urto

(sat=0.06 cm2) con ioni aventi LET 14.6 MeV·cm2/mg. Il valore di sat=0.06 cm2 riportato a livello di singola

cella corrisponde a 0.06 cm2/491520=12.2 m2. L’area di una singola cella, che ha dimensione 7.45 m·6.1

m=45.4 m2 è evidenziata dal rettangolo tratteggiato.

I cerchi evidenziano la superficie delle regioni sensibili:

-le regioni sensibili in prossimità dei drain dei transistor n-MOSFET nelle p-well in condizione off;

-le regioni sensibili in prossimità dei source dei transistor p-MOSFET nelle n-well in condizione off;

53

(Le regioni sensibili hanno un diametro raggio di 1.5 m e uno spessore di 1-2m)

Memoria SRAM: come aumentare la resistenza alle radiazioni?

Utilizzo di tecniche di dissipazione (vanno contro il trend della tecnologia):

1) aumentare il valore del LET di soglia della curva di Weibull, aumentando le dimensioni dei

transistor della cella, e aumentando di conseguenza:

-la capacità di fornire corrente e la conduttanza: i transistor sono così in grado di fornire una

corrente addizionale in modo tale da mantenere lo stato logico iniziale anche a seguito della

perturbazione indotta dall’impatto dello ione;

-la capacità del nodo, in modo da diminuire le variazioni di tensione;

2) inserire dei resistori tra gli invertitori accoppiati della SRAM, in modo da aumentare il tempo di

ritardo RC.

54

Test

55

Test: domande 1-2

1)

Descrivi il fenomeno dell’ITC (Ion-Triggered-Channeling) in un MOSFET facendo

riferimento alla fase di funneling, alla fase bipolare e alla fase di diffusione.

2)

Descrivi il fenomeno del SEU (Single-Event-Upset) in una cella di memoria SRAM

realizzata con 2 MOSFET a canale p e 2 MOSFET a canale n, indicando le parti dei

transistor sensibili agli Effetti da Evento Singolo nel caso della transizione 10 e 01.

56

Note

-Il materiale, la cui raccolta e organizzazione ha richiesto un notevole impegno, può

essere utilizzato liberamente per fini di studio e ricerca, se possibile citandone la

fonte e le referenze.

-Ringrazio tutti coloro che mi segnaleranno parti da correggere/migliorare.

57