Capitolo III

I circuiti logici.

3.1) Introduzione.

Si definisce circuito logico qualsiasi circuito in grado di elaborare un'informazione digitale, cioe'

un'informazione codificata con un segnale capace di assumere solamente due stati, ad uno dei quali

viene associata la costante logica 1, mentre all'altro viene associata la costante logica 0.

I piu' semplici circuiti logici sono quelli realizzati con diodi semiconduttori.

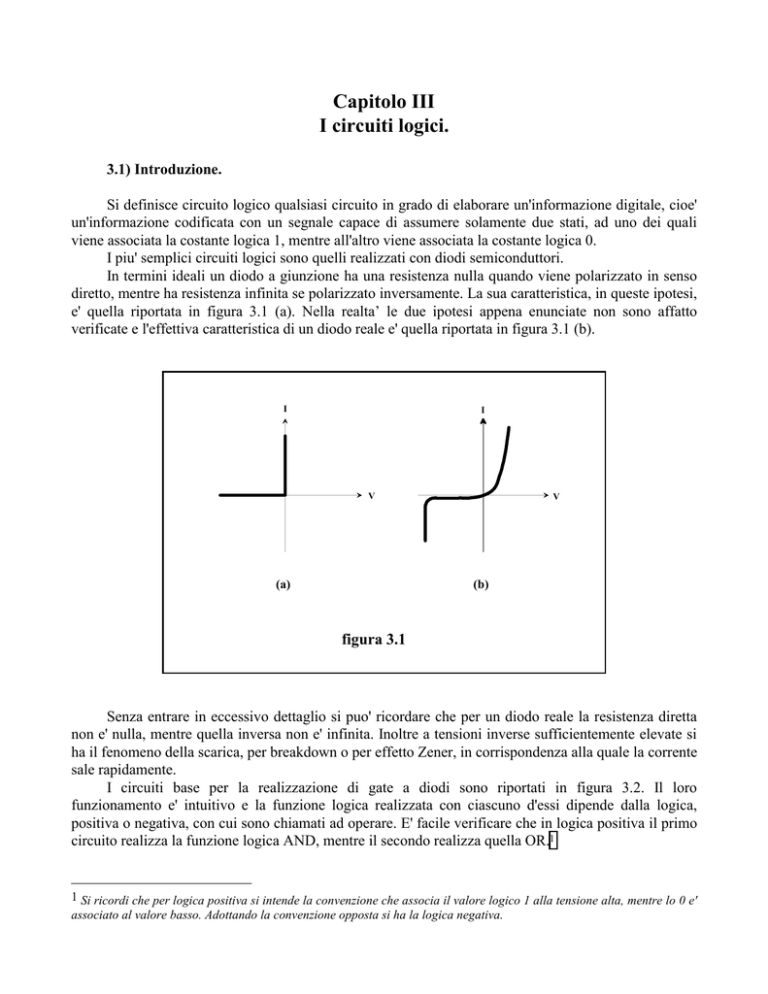

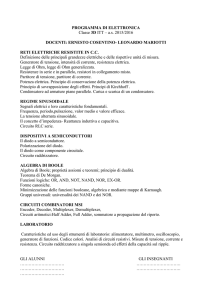

In termini ideali un diodo a giunzione ha una resistenza nulla quando viene polarizzato in senso

diretto, mentre ha resistenza infinita se polarizzato inversamente. La sua caratteristica, in queste ipotesi,

e' quella riportata in figura 3.1 (a). Nella realta’ le due ipotesi appena enunciate non sono affatto

verificate e l'effettiva caratteristica di un diodo reale e' quella riportata in figura 3.1 (b).

I

I

V

(a)

V

(b)

figura 3.1

Senza entrare in eccessivo dettaglio si puo' ricordare che per un diodo reale la resistenza diretta

non e' nulla, mentre quella inversa non e' infinita. Inoltre a tensioni inverse sufficientemente elevate si

ha il fenomeno della scarica, per breakdown o per effetto Zener, in corrispondenza alla quale la corrente

sale rapidamente.

I circuiti base per la realizzazione di gate a diodi sono riportati in figura 3.2. Il loro

funzionamento e' intuitivo e la funzione logica realizzata con ciascuno d'essi dipende dalla logica,

positiva o negativa, con cui sono chiamati ad operare. E' facile verificare che in logica positiva il primo

circuito realizza la funzione logica AND, mentre il secondo realizza quella OR.

Si ricordi che per logica positiva si intende la convenzione che associa il valore logico 1 alla tensione alta, mentre lo 0 e'

associato al valore basso. Adottando la convenzione opposta si ha la logica negativa.

Capitolo III

I circuiti logici.

Vh

Vl

e1

e1

e2

e2

(a)

(b)

figura 3.2

E' interessante notare che, se i diodi fossero ideali, non ci sarebbe alcun limite al numero di

ingressi di ciascun gate, ne' alcun limite al numero di altri circuiti analoghi che potrebbero essere

connessi all'uscita di un singolo gate. Con diodi reali al contrario le cadute ai capi dei diodi conduttori e

le correnti inverse dei diodi interdetti portano ad una continua degradazione dei livelli dei segnali via

via che la complessita' e il numero di stadi in cascata aumentano.

Questo inconveniente della logica a diodi puo' essere superato introducendo degli opportuni

amplificatori, realizzati di solito a transistori. Tali amplificatori, quando realizzati con BJT, lavorano

quasi sempre tra interdizione e saturazione, in modo da assicurare sia una notevole stabilita' dei livelli

di tensione associati a ciascun stato logico che una notevole escursione di tensione in corrispondenza

alla commutazione. Alle velocita' di commutazione piu' elevate tuttavia puo' essere necessario ricorrere

ad amplificatori non saturati in modo da rendere nullo il tempo di restituzione.

Il circuito base di un invertitore, nel caso di transistore a giunzione NPN, e' riportato in figura 3.3.

Molto spesso l'emettitore e' connesso a massa e quando le temperature cui il circuito e' destinato ad

operare non sono eccessive, la resistenza Rbb viene omessa.

V+

Rc

ei

e0

Rb

R bb

VL

V-

figura 3.3

91

Capitolo III

I circuiti logici.

L'invertitore puo' venir utilizzato per correggere le deficienze di carico dei gate a diodi, come

illustrato in figura 3.4, dove l'uscita di un gate a diodi pilota l'ingresso di un invertitore.

VH

V+

Rc

Rg

e1

e2

e0

Rb

Rbb

VL

V-

figura 3.4

Il funzionamento anche in questo caso e' intuitivo e in logica positiva realizza l'operatore NAND,

in logica negativa quello NOR

E' tuttavia interessante far osservare che l'aggiunta di un invertitore diminuisce sostanzialmente i

problemi di carico di un gate a diodi, ma non li elimina completamente.Si consideri infatti la situazione

illustrata in figura 3.5, in un gate NAND pilota un secondo gate dello stesso tipo.

IL

figura 3.5

Quando l'uscita del primo gate e' a livello basso, cioe' quando il relativo transistore e' saturato, in

esso fluisce anche la corrente IL proveniente all'ingresso pilotato. Se altri gate vengono connessi in

parallelo sull'uscita , la corrente totale IL aumenta e se essa supera il limite determinato dalla corrente

di base e da guadagno di corrente del transistore pilotante, quest'ultimo esce dalla saturazione e la

tensione di uscita sale, superando facilmente la tensione rappresentativa del livello logico basso.

92

Capitolo III

I circuiti logici.

Anche il numero di ingressi che ciascun gate puo' pilotare risulta aumentato con l'introduzione

dell'invertitore; non e' infatti piu' necessario assicurare che in uscita il livello di tensione non scenda al

di sotto della tensione rappresentativa del livello logico alto, ma e' sufficiente che alla base dei

transistori pilotati venga fornita una corrente sufficiente a mantenerli in saturazione. Pertanto la

resistenza non infinita dei diodi polarizzati inversamente pesa molto meno che non nel caso in cui

l'invertitore non e' presente, tuttavia pone ancore dei limiti al massimo numero di ingressi pilotabili.

C'e' infine da osservare che l'introduzione dell'amplificatore a transistori permette di eliminare in

modo pressocche' totale la degradazione del segnale che si ha nei circuiti a diodi man mano che

aumenta il numero degli stadi in cascata.

3.2) Caratteristica di trasferimento e valori garantiti per le tensioni.

La caratteristica di trasferimento di un elemento logico descrive il legame che intercorre tra la

grandezza di ingresso e quella di uscita e permette di definire alcune della sue caratteristiche elettriche.

Si consideri allora la caratteristica di trasferimento di un invertitore logico, il cui andamento sara'

in linea di massima simile a quello riportato in figura 3.6.

Vu

VH

V

L

V

VL

VH

i

figura 3.6

Quando all'ingresso vengono applicate tensioni basse in uscita si hanno tensioni alte e viceversa.

Pertanto la tabella che descrive in termini di tensioni il funzionamento e':

V

i

Vu

VL

VH

VH

VL

93

Capitolo III

I circuiti logici.

Sia in logica positiva che in quella negativa l'operatore logico associabile al circuito e' un NOT. E'

tuttavia necessario definire con maggior precisione cosa si intenda con tensione bassa VL e tensione

alta VH.Quando si fissi l'attenzione sulla tensione di uscita si dira' che essa si trova al livello alto

quando e' compresa in un intervallo indicato in figura 3.7 con VH, mentre si trova a livello basso

quando cade nell’intervallo VL.

V

u

VH

VL

figura 3.7

Fissando invece l'attenzione sulla tensione di ingresso si puo' ragionare nel modo seguente.

Fissata una tensione di soglia VT, confine tra gli stati alto e basso e compresa nell'intervallo tra VH e

VL, il circuito dovra' interpretare ogni tensione di ingresso Vi>VT come livello alto e ogni tensione

Vi<VT come livello basso. Con riferimento alla caratteristica di trasferimento la situazione e' allora

quella illustrata in figura 3.8.

V

Tensioni di uscita alte (1)

Tensioni di uscita basse (0)

VH

VL

VT

Tensioni di ingresso basse (0)

Tensioni di ingresso alte (1)

figura 3.8

94

Vi

Capitolo III

I circuiti logici.

Da questa rappresentazione e' ovvio che, affinche' due circuiti logici possano scambiarsi

correttamente informazioni, i due intervalli VH e VL relativi alle tensioni di uscita devono essere

contenuti negli intervalli delle tensioni di ingresso alta e bassa rispettivamente e che, come e' stato

detto, la tensione VT cada nell'intervallo compreso tra VL e VH.

Per un circuito reale e' tuttavia necessario tener conto di alcuni altri fenomeni. Ad esempio si sa

che in un circuito reale la tensione di uscita varia in funzione del carico e pertanto non e' possibile

garantire un valore preciso nei due stati alto e basso.

I costruttori pertanto assegnano per le tensioni di uscita due valori garantiti VOH e VOL,

intendendo che:

•

•

VOH e' la minima tensione di uscita di un dispositivo logico allo stato alto, quando le

condizioni operative sono le peggiori possibile entro il campo di impiego.

VOL e' la massima tensione di uscita allo stato basso per il medesimo dispositivo sempre

nelle peggiori condizioni di lavoro.

Il caso peggiore e' quello in cui tutto, ad esempio la tolleranza sui valori dei componenti, la

temperatura, le variazioni delle tensioni di alimentazione, il carico ecc. concorre a far salire la tensione

di uscita dello stato basso e a diminuire quella dello stato alto.

Anche per l'ingresso valgono considerazioni analoghe. C'e' inoltre da tener presente che la

caratteristica di trasferimento di un elemento reale presenta nella zona di transizione tra i due stati un

andamento che non e' mai verticale. Pertanto non e' possibile parlare come nel caso ideale di una

tensione VT ed e' necessario anche in questo caso far ricorso ai valori garantiti VIH e VIL, intendendo

che:

•

•

VIL e' la massima tensione di ingresso che, nelle peggiori condizioni di funzionamento sara'

sicuramente riconosciuta dal circuito come una tensione dello stato basso ( in logica positiva

uno 0 logico).

VIH e' la minima tensione di ingresso che nelle peggiori condizioni di funzionamento sara'

sicuramente riconosciuta dal circuito come una tensione dello stato alto (in logica positiva un

1 logico)

Poiche' normalmente VIL < VIH esiste un intervallo di tensioni VIL - VIH che determina una zona

di incertezza sul livello logico dell'ingresso.

I quattro valori VIL, VOL, VIH, VOH possono venir trovati nei fogli caratteristici forniti dai

costruttori.

La situazione teste' descritta e' rappresentata nel grafico di figura 3.9

Per un corretto scambio di informazioni tra due circuiti, per evitare cioe' di andare ad interessare

la zona di incertezza, e' necessario che:

VOH > VIH

VOL < VIL

95

Capitolo III

I circuiti logici.

Vi

Vu

V OH

V IH

zona di incertezza

V IL

V OL

figura 3.9

In un circuito reale vi sono poi ulteriori vincoli da rispettare. La tensione di uscita dovra'

ovviamente essere compresa tra quella del riferimento (massa) VGND e quella di alimentazione VAL

VGND < Vu <VAL

La tensione di ingresso a sua volta non dovra' superare i limiti imposti dalla possibilita’ che il

circuito venga danneggiato. In altre parole

Vmin < Vi < Vmax

Pertanto, tenendo conto di quanto detto, le reali condizioni di funzionamento di ingresso e di

uscita sono quelle riportate in figura 3.10.

USCITA

VAL

INGRESSO

Vmax

livello alto

VOH

VIH

Campo delle tensioni di

ingresso tali da non danneggiare il dispositivo

VOL

VIL

livello basso

VGND

Vmin

figura 3.10

96

Capitolo III

I circuiti logici.

I risultati raggiunti permettono ora di affrontare un nuovo argomento, cioe' quello dell'immunita’

al rumore.

3.3) Il margine di rumore.

Nella trasmissione dell'informazione dall'uscita di un elemento all'ingresso dell'elemento

successivo il segnale puo' venir alterato per la presenza di rumore. Tale rumore puo' venir generato per

le cause piu' diverse quali ad esempio per accoppiamento elettromagnetico o a causa della caduta di

tensione lungo le linee di collegamento, per la presenza di disturbi sulle alimentazioni o per altre cause

ancora.

La domanda che ci si deve porre e' pertanto qual'e' l'ampiezza massima del disturbo che non altera

l'informazione. In altre parole e' necessario valutare qual'e' il valore del disturbo che non permette di

discriminare qual'e' il valore logico associato al segnale.

Con riferimento alla figura 3.10 la risposta appare semplice; il rumore infatti non dev'essere tale

da par uscire il segnale prelevato all'uscita del primo elemento dagli intervalli ammessi per le tensioni

di ingresso del secondo elemento.

Si possono allora definire due quantita', VNH e VNL, dette rispettivamente margine di rumore allo

stato alto e allo stato basso, come differenza tra i rispettivi valori garantiti di uscita e di ingresso.

VNH = VOH - VIH

VNL = VIL - VOL

Se l'ampiezza del rumore non supera queste due quantita' il segnale che si presenta all'ingresso del

secondo elemento non andra' mai ad interessare la zona di incertezza e l'informazione logica non verra'

alterata.

I margini di rumore cosi' definiti prendono il nome di margini di rumore apparenti in quanto

sono calcolati con riferimento ai valori garantiti. Rispetto alla realta' tuttavia tali valori sono

pessimistici e i margini di rumore reali sono superiori.

Si consideri un semplice sistema reazionato (figura 3.11 a) costituito da due invertitori identici.

Sul grafico di fig. 3.11 (b) sono riportate sia la caratteristica del dispositivo 1 che quella del dispositivo

2, con l'avvertenza tuttavia che il segnale di ingresso X2 e' riportato sull'asse verticale, e il

corrispondente segnale di uscita su quello orizzontale, al contrario pertanto di quanto fatto per il

dispositivo 1.

Tale modo di operare appare tuttavia naturale quando si consideri che il segnale di uscita di un

gate coincide con il segnale di ingresso dell'altro gate. Le due caratteristiche si intersecano in tre punti,

A, B e C che rappresentano le sole tre condizioni in cui il circuito puo' trovarsi; infatti solo in questi

punti

X2 = Y1

e

X1 = Y2

Se il dispositivo 1 si trova nel punto A allora le condizioni operative dell'ingresso e dell'uscita del

dispositivo 2 sono ancora specificati dal punto A.

Il sistema, a rigore, potrebbe trovarsi in uno qualsiasi dei tre punti A, B o C; tuttavia la

condizione di funzionamento nel punto B e' instabile e qualsiasi perturbazione, per quanto piccola,

portera' il sistema in A o in C.

97

Capitolo III

I circuiti logici.

x1

y

x2

1

1

2

y

2

(a)

x 2 ,y 1

A

1

B

2

C

x 1 ,y 2

(b)

figura 3.11

Nella realta' i due dispositivi non saranno mai identici. La caratteristica di trasferimento non

potra' dunque essere rappresentata da un singola curva, ma sara' un inviluppo contenente tutte le

possibili caratteristiche. Le dimensioni dell'inviluppo sono determinate dai limiti fissati per l'uscita,

quando viene compiuto l'esame di accettazione in fase di produzione.

In fig. 3.12 sono riportati due di questi inviluppi per il semplice sistema reazionato che e' stato

preso in considerazione. Le tensioni rappresentative del punto di lavoro di ciascun dispositivo possono

in questo caso cadere in una delle tre aree tratteggiate A,B e C, intersezioni tra i due inviluppi. E'

evidente che anche in questo caso tutti i punti dell'area B rappresentano condizioni di equilibrio

instabile.

A

1

*

V IL

VOUT

0

B

V *IH

V*

OH

V NL

VIN

figura 3.12

98

V NH

C

*

V OL

Capitolo III

I circuiti logici.

L'ordinata del punto al vertice sinistro alto dell'area C rappresenta la massima tensione allo stato

basso che un dispositivo puo' avere quando viene pilotato da un altro dispositivo della stessa famiglia.

Tale tensione viene indicata con VOL*.

Un dispositivo pilotato con VOL* avra' come tensione di uscita VOH* cioe’ quella rappresentata

dall'ordinata del vertice destro basso dell'area A.

I due livelli cosi definiti sono le uscite dei due dispositivi interconnessi, nell'ipotesi che durante la

loro selezione si siano incontrati due dispositivi al limite estremo del campo di tollerabilità, in modo

tale che il sistema reazionato lavori nelle peggiori condizioni possibili.

Per un qualsiasi motivo tuttavia, ad esempio per la presenza di un disturbo, il segnale di ingresso

puo' spostarsi dalla regione A verso la regione B. Malgrado cio', purche' non si entri nella regione B

stessa, il segnale sara' ancora interpretato come segnale logico basso. In corrispondenza la tensione

d'uscita tendera' al vertice opposto della regione B, ma non dara' luogo ad un cambio di stato del

sistema. Al cessare della causa perturbante il sistema ritornera' nelle condizioni originarie.

I vertici opposti della regione B rappresentano pertanto i valori estremi della tensione di ingresso

che non danno luogo ad una commutazione del sistema; tali valori vengono indicati con VIL* e VIH* e

rappresentano rispettivamente il massimo valore di ingresso sicuramente riconosciuto come uno zero

logico e il minimo valore riconosciuto come un uno logico. Il margine di rumore del sistema e' la

distanza che intercorre tra le uscite dello stesso sistema supposto privo di rumore e le due tensioni

limite di ingresso VIL* e VIH*.

Queste differenze, indicate in fig. 3.12. con VNH e VNL sono dette rispettivamente margine di

rumore allo stato alto e margine di rumore allo stato basso e possono ovviamente essere differenti

nei due stati logici.

Si noti che gli inviluppi si ampliano assegnando specifiche di tolleranza meno pesanti; inoltre se

la pendenza della zona di transizione diminuisce, la regione B si estende verso A e C, diminuendo i

margini di rumore.

Sui dati caratteristici forniti dai costruttori sono assegnate le quantita' VOH, VOL , VIH e VIL che

non coincidono perfettamente con le quantita' asteriscate fin qui introdotte.

Le grandezze fornite dai costruttori sono cautelative rispetto a quelle asteriscate; piu'

precisamente si puo' dire che:

VIL = VIL*

VIH = VIH*

mentre VOH si trova sulla curva di trasferimento appena a destra e al di sotto della zona A e VOL appena

a sinistra e al di sopra della zona C.

I margini di rumore apparenti, calcolati come:

VNL = VIL - VOL

VNH = VOH - VIH

sono pertanto inferiori a quelli reali, sia per i valori piu' pessimistici di VOL e VOH, sia perche'

normalmente i dispositivi usati ben difficilmente lavoreranno nelle peggiori condizioni, identificate dai

vertici della regione B e da quello inferiore e superiore rispettivamente della regione A e C.

E’ interessante notare che esiste un vincolo sulla caratteristica di trasferimento di un elemento

logico. Si prenda infatti in considerazione la caratteristica di figura 3.13.

99

Capitolo III

I circuiti logici.

Vu

VH

∆Vu

V

L

V

VL

∆Vi

VH

i

figura 3.13

E’ necessario che nel tratto di transizione tra VH e VL il guadagno del dispositivo, definito come

rapporto tra ∆Vu e la corrispondente ∆Vi, sia maggiore dell’unita’ Si supponga infatti che il guadagno

sia inferiore all’unita’ e si considerai una cascata di dispositivi, come illustrato in figura 3.14.

figura 3.14

In questo caso ad ogni stadio il segnale viene attenuato e ad un certo momento esso potrebbe

andare ad interessare la zona di incertezza anche se i margini di rumore fossero rispettati,

contrariamente all’obiettivo che ci si era proposto. La presenza di un tratto di caratteristica con

guadagno superiore all’unita’ garantisce invece la ricostruzione dei livelli logici anche quando essi

siano alterati da rumore e disturbi.

Nelle considerazioni fatte si e' tuttavia implicitamente assunto che la caratteristica di

trasferimento di un gate dipenda unicamente dall'ampiezza del segnale di ingresso e non dalla

frequenza o dalla durata dell'impulso di ingresso.

Si ricordi tuttavia che un circuito digitale reale, come qualsiasi altro dispositivo fisico, non puo'

rispondere immediatamente ad una variazione del segnale di ingresso.

E’ necessario pertanto prendere in considerazione anche quello che viene chiamato margine di

rumore dinamico, detto anche margine di rumore in corrente alternata, di solito ben diverso da

quello in corrente continua.

In un circuito digitale correttamente progettato, che operi con impulsi di durata notevolmente

superiore ai tempi di commutazione dei vari gate e con una bassa frequenza di ripetizione, i margini di

rumore in corrente continua e in corrente alternata non differiscono in maniera apprezzabile. Non

appena pero' la larghezza dell'impulso diminuisce e diventa paragonabile con i tempi di commutazione,

100

Capitolo III

I circuiti logici.

il margine di rumore cambia in funzione di come sono realizzati circuitalmente i vari gate. Se

l'accoppiamento tra i vari stadi e' di tipo capacitivo, il margine di rumore puo' anche diminuire al

diminuire della durata dell'impulso; tuttavia nella maggior parte dei casi il margine di rumore va via via

aumentando, poiche' il circuito non e' in grado di rispondere istantaneamente. A frequenze molto alte e

con larghezze dell'impulso di ingresso molto piccole si puo' poi avere un effetto di polarizzazione del

dispositivo, che puo' diminuire nuovamente il margine di rumore.

In fig. 3.15 e' riportato a titolo di esempio l'andamento del margine di rumore in funzione della

larghezza dell'impulso per dispositivi della famiglia TTL standard.

8

7

margine 6

di

5

rumore

4

(volt)

3

2

1

0

low

hig

0

5

15

10

20

25

larghezza dell'impulso (nsec.)

figura 3.15

3.4) I valori garantiti per le correnti.

Tutte le considerazioni condotte fino a questo momento sono state fatte con riferimento ai soli

livelli di tensione dei segnali e senza preoccuparsi in alcun modo del carico connesso a ciascuna uscita

e quindi senza considerare la corrente che da tale uscita viene prelevata.

La connessione di due dispositivi elettronici, di qualsiasi tipo essi sino, puo’ sempre venir

rappresentata con il modello semplificato di figura 3.16

B

A

I

Ro

Ri

figura 3.16

101

Capitolo III

I circuiti logici.

dove Ro e’ la resistenza di uscita dell’elemento pilota (A) e Ri rappresenta la resistenza di ingresso del

dispositivo ricevente (B). Sulla linea di connessione di conseguenza circola una corrente I.

Da un esame, anche semplicemente qualitativo, di tale modello si deduce che l’elemento A e’ in

grado di fornire le corrette tensioni solo se il carico non e’ eccessivo, cioe’ solo se la corrente e’

inferiore a dei limiti prefissati.

In altre parole i valori garantiti di tensione VOH e VOL sono riferiti a determinati valori di

corrente e cioe’

per Vo ≥ VOH

dev’essere

Io < IOH

Vo ≤ VOL

dev’essere

Io < IOL

per

dove i valori di corrente sonno espressi in modulo. Se si eccedono tali limiti le tensioni di uscita non

sono piu’ garantite.

Anche per l’ingresso valgono analoghe considerazioni; indicando con Ii la corrente assorbita

dall’ingresso, il costruttore garantisce che se le tensioni applicate rientrano nel campo dei valori previsti

le relative correnti non supereranno determinati valori. Valgono le seguenti relazioni (ancora valide in

modulo):

per Vi ≥ VIH

Ii < IIH

Vi ≤ VIL

Ii < IIL

per

Per quanto riguarda i segni delle correnti si considerano di solito positive le correnti entranti nel

dispositivo e negative quelle uscenti.

3.5) Le famiglie logiche e i dispositivi logici integrati.

3.5.1) Considerazioni generali.

Si definisce famiglia logica qualsiasi insieme di circuiti logici con parametri elettrici omogenei.

Tutti i dispositivi di una famiglia logica sono tra loro compatibili, nel senso che i livelli logici sono gli

stessi, possono essere alimentati con la stessa tensione e l'uscita di un elemento e' in grado di pilotare

direttamente almeno un ingresso di qualsiasi altro elemento della stessa famiglia.

Al contrario, poiche' ogni famiglia logica usa un diverso circuito elementare, esse non sono di

solito compatibili tra loro, anche nel caso in cui alcune delle loro caratteristiche coincidano.

Ciascuna famiglia e' basata su un particolare tipo di circuito elementare usato in tutti i dispositivi

della famiglia per realizzare invertitori, gate di diverso tipo ed elementi di memoria quali i flip-flop.

I circuiti logici moderni sono realizzarti esclusivamente in tecnica integrata e ciascuna famiglia

include, oltre ai dispositivi logici elementari, anche elementi a media e molto spesso a larga scala di

integrazione

Ciascuna famiglia comprende, in aggiunta ai dispositivi base SSI, MSI e LSI, un certo numero di

circuiti ausiliari, quali ad esempio traslatori di livello (per scopi di interfacciamento con altre famiglie),

102

Capitolo III

I circuiti logici.

circuiti di condizionamento del segnale (trigger di Schmitt e multivibratori), circuiti di pilotaggio di

visualizzatori e vari altri circuiti per applicazioni speciali.

Nel discutere le famiglie logiche e' importante porre l'accento sul fatto che il loro sviluppo

avviene in un ambiente dallo sviluppo tecnologico estremamente veloce e di intensa competizione. Tale

fatto ha portato ad un rapido sviluppo dei componenti e, a causa della vitalita' del mercato, al nascere e

all'affermarsi di un notevole gruppo di produttori. Al giorno d'oggi, quando uno dei produttori ha

successo nell'introdurre e commercializzare una determinata famiglia logica, essa viene

immediatamente prodotta su licenza dalle altre compagnie, eventualmente completata con nuovi

dispositivi o migliorata nelle sue caratteristiche.

Ogni famiglia logica viene progettata per una differente applicazione ed ha in alcune sue

caratteristiche i suoi punti di forza, in altre i suoi inconvenienti.

Poiche' il circuito base di ciascuna famiglia e' differente, i relativi dispositivi hanno caratteristiche

diverse. Ad esempio i circuiti dei calcolatori di grosse dimensioni devono operare molto velocemente e

di conseguenza per la loro realizzazione si useranno componenti di famiglie logiche veloci; se al

contrario si prevedesse per il circuiti lunghi periodi di funzionamento con alimentazione fornita da

batterie, allora diventa molto piu' importante la caratteristica di un basso consumo.

Sebbene una valutazione corretta dei circuiti digitali integrati richieda un attento studio dei dati

forniti dal costruttore, si riportano qui di seguito le definizioni di quelle caratteristiche che si ritengono

maggiormente interessanti e significative.

FAN-IN. E' il numero di ingressi che controllano un operatore logico. Molto

spesso sono disponibili degli ingressi di espansione che permettono di

aumentare il fan-in. L'eccessivo uso di ingressi di espansione fa

tuttavia aumentare la capacita' di ingresso e di conseguenza il tempo

di propagazione.

FAN-OUT.E' la misura del carico che puo' essere connesso all'uscita di un gate

o di qualsiasi elemento logico della famiglia. Poiche' il carico e'

normalmente dato da uno o piu' ingressi di altri elementi logici della

stessa famiglia, il fan-out e' usualmente identificato dal numero di

ingressi che possono venir connessi all'uscita dell'elemento logico

considerato. Piu' esattamente ciascuna famiglia logica ha "un'unita' di

carico" espressa in milliampere che rappresenta la corrente necessaria

ad attivare un tipico circuito di quella famiglia logica. Il fan-out viene

ottenuto normalizzando tramite l'unita' di carico la massima corrente

di uscita. In sostanza quindi, quando ad esempio si parla di fan-out

pari a 10, cio' sta a significare che puo' venir pilotato un numero di

ingressi tale da costituire un fattore di carico normalizzato pari a 10.

LIVELLI LOGICI. L'uscita di un circuito digitale puo' assumere normalmente

due soli stati, detti rispettivamente alto e basso. I corrispondenti livelli

di tensione vengono indicati di solito con VH e VL e variano da

famiglia a famiglia logica. E' opportuno tuttavia far notare che alcuni

circuiti digitali vengono progettati per lavorare a tre stati e il terzo

stato corrisponde a un circuito aperto.

103

Capitolo III

I circuiti logici.

RITARDO DI PROPAGAZIONE E VELOCITA'. Il ritardo di propagazione

misura quanto rapidamente si propaghi la commutazione di un livello

logico di ingresso verso l'uscita.

La fig. 3.17 illustra un invertitore nella configurazione a emettitore

comune e la sua risposta ad un impulso positivo applicato alla base,

tale da portarlo da interdizione a saturazione e viceversa.

Per determinare questa risposta e' necessario considerare un certo

numero di fenomeni fisici complessi. Vale la pena di richiamare

brevemente alcuni di essi.

ei

V+

t

Rc

ei

e0

Rb

ic

R bb

VL

Vt

ts

td

tr

tf

figura 3.17

A partire dall'istante in cui inizia l'impulso di base, vi e' un tempo di

ritardo td prima che la corrente di collettore inizi a salire. Questo

ritardo e' determinato essenzialmente dalla capacita' totale baseemettitore del transistore, che deve venir caricata ad una tensione

lievemente positiva prima che il transistore possa iniziare a condurre.

Dopo l'inizio della conduzione si ha un tempo di salita finito tr

determinato principalmente dalla capacita' di collettore e dalle

caratteristiche intrinseche del transistore.

Sul fronte di discesa dell'impulso di ingresso si ha un primo tempo ts,

detto tempo di restituzione, dovuto sia alla capacita' base-emettitore

sia all'accumulo di cariche minoritarie nello spazio di base. Questo

tempo e' forse il piu' importante tra i tempi di commutazione ed e'

comunque notevolmente piu' grande che non td.

104

Capitolo III

I circuiti logici.

Infine vi e' un tempo di discesa finito tf dovuto anch'esso, come il

tempo di salita, alla capacita' di collettore e alle caratteristiche

intrinseche del transistore.

Allo scopo di specificare il ritardo cui il segnale e' sottoposto

nell'attraversare i gate i tempi tr e tf sono significativi solo se i

corrispondenti tempi del segnale presente all'ingresso sono

trascurabili. E' questo tuttavia un caso abbastanza raro, poiche' i

circuiti logici sono normalmente pilotati da circuiti analoghi e di

conseguenza i tempi di salita e di discesa sono dello stesso ordine di

grandezza sia all'ingresso che all'uscita. Essi tuttavia, pur non essendo

completamente significativi, influenzano il valore del tempo di ritardo

a seconda di come questo tempo di ritardo viene misurato. E'

necessario quindi specificare i punti delle forme d'onda di ingresso e

di uscita usati per definire i tempi di ritardo stessi.

In definitiva i tempi di ritardo di un gate vengono misurati, come e'

illustrato in fig. 3.18, pilotando l'ingresso con un impulso che abbia

tempo di salita e discesa dello stesso ordine di grandezza di quelli del

segnale di uscita ed eseguendo la misura con riferimento a punti ben

specificati, quali ad esempio possono essere i tempi all'emivalore.

ingresso

uscita

t pd1

t pd0

figura 3.18

Piu' esattamente si definiscono di solito due ritardi di propagazione

che tengono conto della dissimmetria di funzionamento nelle due

commutazioni: il ritardo di propagazione per l'uscita che commuta da

livello basso a livello alto e' indicata con tpLH o tpd+, quello relativo

alla commutazione opposta con tpHL o tpd-. Ambedue i tempi vengono

misurati tra i punti al 50% dei segnali di ingresso e di uscita. La

semisomma di tali tempi prende il nome di ritardo medio di

propagazione ed e' indicata normalmente con tav o tpd. Il tempo di

salita tr e di discesa tf sono invece misurati tra il 10% e il 90% del

fronte di salita e rispettivamente di discesa dell'uscita. I tempi di

105

Capitolo III

I circuiti logici.

propagazione variano con la temperatura, la tensione di alimentazione

e il carico.

Si indica invece con velocita’ la massima frequenza alla quale un flip

flop puo’ commutare senza errori. Ritardo di propagazione e velocita’

sono direttamente correlati, anche se non e’ possibile, a causa di tutta

una serie di fattori eccessivamente complessi per venir affrontati in

questa sede, illustrare il legame che intercorre tra loro.

DISSIPAZIONE DI POTENZA. Come in qualsiasi altro circuito elettronico

la potenza dissipata viene misurata in watt o in milliwatt. Essa

rappresenta la potenza che effettivamente si dissipa nel dispositivo e

non comprende quindi la potenza che viene eventualmente fornita ad

altri dispositivi. Di regola essa indica nei circuiti integrati la potenza

che si dissipa in un gate che lavora per meta' del tempo allo stato alto

e per l'altra meta' allo stato basso e permette di valutare la potenza

totale dissipata dal circuito ai fini del dimensionamento

dell'alimentatore.

IMMUNITA' AL RUMORE. Misura la quantita' di segnale disturbante che

puo' essere sovrapposto a un segnale logico senza causare un'errata

commutazione dell'uscita. E' necessario distinguere, come si e’ gia’

visto in precedenza, tra immunita' al rumore statica, relativa a segnali

che varino lentamente o ad impulsi sufficientemente lunghi e

immunita' al rumore dinamica. E' abbastanza evidente infatti che un

impulso di ingresso di durata comparabile con il ritardo di

propagazione potra' avere un'ampiezza anche notevole senza dar

luogo ad un'errata commutazione dell'uscita. La medesima ampiezza

sarebbe invece intollerabile se il segnale di disturbo fosse di durata

sufficientemente lunga.. L'immunita' al rumore e' anch'essa funzione

della temperatura, della tensione di alimentazione e dal carico.

CAMPO DI TEMPERATURE DI UTILIZZO. E' il campo di temperatura

entro il quale un circuito integrato puo' operare senza che alcuna delle

sue caratteristiche nominali sia compromessa.

ATTITUDINE AL PILOTAGGIO DI CARICHI CAPACITIVI.

L'attitudine a pilotare carichi capacitivi e' un'importante caratteristica

dei circuiti digitali integrati, soprattutto quando un'uscita deve

pilotare delle interconnessioni realizzate con cavi di una certa

lunghezza.

Questa attitudine dipende direttamente dall'impedenza d'uscita del

circuito e quanto minore e' questa impedenza, tanto meglio un carico

capacitivo viene pilotato. Quando infatti ad un circuito viene applicato un carico capacitivo i tempi di salita e di discesa vengono

largamente influenzati dal carico stesso. Il tempo di propagazione

viene aumentato in maniera proporzionale all'aumento della costante

106

Capitolo III

I circuiti logici.

di tempo del circuito causata dal carico capacitivo. In fig. 3.19 e'

riportato il tempo di propagazione in funzione della capacita' di carico

e della tensione di alimentazione per un tipico circuito appartenente

alla famiglia DTL.

nsec.

4 volt

60

50

5 volt

Ritardo di

propagazione

40

30

6 volt

20

10

20

40

60

80

100

Capacita' di carico

figura 3.19

PROTEZIONE DAL CORTO CIRCUITO. Impedisce che un circuito, la cui

uscita sia stata connessa direttamente a terra, venga danneggiato. Tale

proprieta' puo' essere riconosciuta semplicemente esaminando il

circuito e riconoscendo se nel circuito d'uscita vi sia o meno una

resistenza connessa tra alimentazione e terminale di uscita, destinata a

limitare la corrente nel caso di corto circuito.

TOLLERANZA SULLE TENSIONI DI ALIMENTAZIONE. Definisce il

campo di tensioni di alimentazione entro il quale le caratteristiche del

dispositivo sono garantite.

TIPO DI CIRCUITO LOGICO. Dipende dal numero di circuiti elementari

integrati su un unico substrato di silicio. Si possono distinguere le tre

principali categorie:

Circuiti SSI (small scale integration) con un numero di porte logiche

elementari che puo' raggiungere le 12 porte per involucro.

Circuiti MSI (Medium scale integration) con capacita' comprese tra

le 12 e le 100 porte logiche.

107

Capitolo III

I circuiti logici.

Circuiti LSI (Large scale integration) con capacita' superiore alle 100

porte logiche.

La realizzazione SSI copre il campo dei singoli elementi logici e delle

reti logiche piu' semplici, quelle MSI le reti logiche di dimensioni

medio - grandi, quali convertitori A/D, multiplexer, ecc. Infine le

realizzazioni LSI sono destinate a reti logiche di dimensioni molto

ampie, quali memorie, unita' aritmetico-logiche, ecc.

TIPO DI INVOLUCRO. Esistono numerosi tipi di involucro per i circuiti

integrati: I piu' comuni sono il TO-5, il flat pack, il dual in line e il

SOT. Il TO-5 e' un involucro metallico, in pratica uguale a quello

utilizzato per i transistori, con 8,10 o 12 piedini. Il flat pack e' un

involucro misto metallo ceramica di forma rettangolare appiattita. Il

flat pack viene prodotto in due dimensioni con 10, 12 o 14 piedini;

questi a loro volta possono essere terminali piatti flessibili e dorati o

collegamenti a sezione circolare in rame. L'involucro dual in line e'

forse il piu' diffuso, pur essendo di maggiori dimensioni che non gli

altri due. I piedini, di tipo rigido, sono in numero di 14, 16, 24 o piu',

ma proprio per la loro rigidita' sono particolarmente adatti ad un

montaggio automatico su circuito stampato. Infine il SOT e'

l'involucro utilizzato nelle tecnologie di montaggio superficiale.

Esistono ovviamente numerosi altri involucri e al giorno d'oggi non e'

raro trovare contenitori con un numero di piedini di collegamento che

supera abbondantemente il centinaio.

I parametri descritti presentano il difetto di un'eccessiva schematizzazione, con l'aggravante che

ciascun costruttore tende ad enfatizzare gli aspetti positivi dei suoi prodotti e a minimizzarne quelli

negativi.

Vi sono altri parametri oltre quelli descritti che potrebbero determinare la scelta di una famiglia

logica, ad esempio la varieta' dei componenti della famiglia o la loro reperibilita' presso diverse fonti, la

compatibilita' con i livelli di segnale o con le tensioni di alimentazione di altre famiglie o ancora la loro

resistenza ad ambienti particolarmente sfavorevoli e/o aggressivi.

Infine come parametro di notevole interesse si puo' citare il prodotto della potenza dissipata per il

tempo medio di propagazione. Anche se raramente riportato sulle caratteristiche, tale parametro misura

in un certo qual modo la "bonta'" di una famiglia logica, che si puo' ritenere inversamente proporzionale

al valore del prodotto stesso.

3.5.2) Caratteristiche di temporizzazione di flip-flop e registri.

Come e’ noto prende il nome di flip-flop, o multivibratore bistabile, un circuito in grado di

permanere per un tempo indefinitamente lungo in uno dei suoi due stati stabili. Tale circuito pertanto si

rivela adatto a memorizzare con i suoi due stati un’informazione binaria.

In termini generali viene invece indicato con il nome registro un qualsiasi insieme di flip-flop in

cui possa venir memorizzata un’informazione omogenea codificata su piu’ bit.

108

Capitolo III

I circuiti logici.

Il piu' semplice elemento di memoria puo' essere realizzato con due gate di tipo invertente

connessi con accoppiamento incrociato. Molto spesso esiste poi anche un ingresso di abilitazione

(enable) che impropriamente viene chiamato nella maggior parte dei casi clock.

Il collegamento incrociato di due gate da' luogo a un flip-flop che viene detto di tipo trasparente,

in quanto l'uscita risponde immediatamente alle variazioni degli ingressi. In tal caso, riportando le

uscite del dispositivo agli ingressi, si potrebbero addirittura generare condizioni di oscillazione.

Elementi non trasparenti sono viceversa i flip-flop master-slave, in cui la memorizzazione

dell'informazione si ha durante il periodo di clock, mentre la variazione dell'uscita si ha nell'intervallo

tra due successivi impulsi di clock, oppure i flip-flop azionati sui fronti.

A causa della non trasparenza l'uscita di questi dispositivi puo' essere riportata all'ingresso di un

circuito sequenziale senza particolari precauzioni e senza dar luogo a condizioni pericolose. Non sono

pertanto richiesti schemi di temporizzazione multifase e il progetto del sistema ne risulta notevolmente

semplificato.

Per il corretto uso di questi dispositivi il progettista deve conoscere tuttavia l'esatto significato dei

parametri di temporizzazione (tempo di ritardo e specifiche di temporizzazione dell'ingresso) e metterli

in relazione al fenomeno del "clock skew".

a) Tempo di propagazione.

L'uscita di qualsiasi flip-flop o registro cambia unicamente in corrispondenza ad una delle

transizioni del segnale di clock; nei circuiti piu' moderni tale transizione e' quella dallo stato basso allo

stato alto.

Il ritardo tra questo fronte e la variazione corrispondente dell'uscita e' il tempo di ritardo del

dispositivo e viene indicato con tpd. Molto spesso tuttavia i tempi sono due, quello tra il fronte attivo

del clock e la commutazione positiva dell'uscita, indicato con tpd+ o tpLH , e quello tra il fronte attivo del

clock e la commutazione negativa dell'uscita, indicato con tpd- o tpHL.

Sui dati caratteristici sono di solito indicati sia il valore tipico che il valore massimo di tali

parametri.

b) Specifiche di temporizzazione degli ingressi.

I flip-flop sensibili ai fronti sono normalmente condizionati dai valori che i segnali di ingresso

possiedono immediatamente prima del fronte attivo del clock. Per un corretto funzionamento i dati di

ingresso devono quindi essere presentati con un certo anticipo rispetto a questo fronte ed esiste pertanto

un intervallo di tempo critico immediatamente precedente il clock, durante il quale essi non devono

cambiare.

L'istante nel quale il valore degli ingressi assume importanza viene detto tempo di "set-up", e'

critico e viene di solito indicato con ts. Poiche' tutti i parametri circuitali variano con la temperatura, le

tensioni di alimentazione ed in funzione delle tolleranze di fabbricazione e del carico, anche il tempo di

set-up ha una certa dispersione.

E' importante assicurarsi che i livelli di ingresso rimangano stabili all'interno della finestra

compresa tra il piu' lungo tempo di set-up, che rappresenta il piu' lento dei dispositivi e il piu' breve, che

ne rappresenta il piu' veloce.

Purtroppo i costruttori hanno usato via via diverse nomenclature, talvolta in contrasto, per

indicare i due bordi della finestra di temporizzazione appena definita.

109

Capitolo III

I circuiti logici.

Il piu' lungo tempo di set-up viene spesso chiamato ts(max), ma spesso anche ts(min) in quanto

rappresenta la durata minima dell'intervallo di tempo durante il quale gli ingressi devono rimanere

costanti prima dell'impulso di clock.

Il piu' breve tempo di set-up viene detto ts(min), ma spesso senza alcuna logica ts(max).

La Fairchild usa il termine "tempo di disimpegno" (release time tr), altri fabbricanti lo chiamano

- thold (tempo negativo di tenuta). Quest'ultimo nome prende origine dal fatto che nei circuiti piu'

anziani il ritardo di propagazione del clock era superiore a quello degli ingressi e di conseguenza questi

ultimi dovevano rimanere stabili anche dopo il fronte attivo del clock (tempo di tenuta positivo).

Tutti i circuiti moderni hanno tuttavia tempi di set-up positivi e di conseguenza tempi di tenuta

negativi.

A differenza dei flip-flop comandati sui fronti, nei flip-flop master-slave a livelli il master accetta

i dati di ingresso durante tutto il semiperiodo attivo del clock, mentre lo slave commuta in funzione del

contenuto del master nell'intervallo tra un impulso di clock e l'altro.

Pertanto in questi flip-flop per un corretto funzionamento e' indispensabile che gli ingressi

rimangano stabili durante l'intero semiperiodo attivo del clock. E' opportuno quindi che la durata

dell'impulso di clock sia la minima possibile, compatibilmente con i dati forniti dal costruttore.

Qualsiasi sia poi il dispositivo, comandato a fronti o a livelli, e' necessario assicurarsi che i tempi

di salita e di discesa non superino determinati valori. Infatti, anche se i dispositivi non sono

direttamente sensibili all'inclinazione dei fronti, quando tali tempi fossero molto lunghi, il segnale di

clock si troverebbe in prossimita' dei livelli di soglia per tempi superiori al ritardo di propagazione del

flip-flop, e si potrebbero avere, in presenza di disturbi anche piccoli, determinati ad esempio da

diafonia, delle commutazioni multiple.

E' opportuno pertanto che il segnale di clock abbia dei tempi di commutazione non superiori a 5 6 volte il ritardo di propagazione del dispositivo.

3.5.3) Le famiglie logiche.

Si e’ gia’ accennato in precedenza a cosa si intenda per famiglia logica. Si prendano ora in

considerazione (tabelle 3.1 e 3.2) a titolo di esempio le caratteristiche riportate sui “data sheet” del

componente LS7410 – LS5410, cioe’ le caratteristiche di un gate di tipo low power Schottky

appartenente alla cosiddetta famiglia TTL.

Tabella 3.1: Condizioni di funzionamento raccomandate

Parametro

Famiglia

Tensione di alimentazione, Vcc

54

74

Corrente di uscita a livello alto, IOH

54

74

Corrente di uscita a livello basso, IOL

54

74

Temperatura di funzionamento in aria, TA

54

74

110

Min.

4.5

4.75

-55

0

Nom.

5

5

Max. Unita’

5.5

V

5.25

-400

µA

-400

4

mA

8

125

°C

70

Capitolo III

I circuiti logici.

Tabella 3.2: Caratteristiche elettriche nell’intervallo di temperatura di funzionamento (se non

altrimenti specificato).

Parametro

Condizioni di misura * Famiglia Min. Tip.** Max. Unita’

2

VIH Tensione di ingresso

V

a livello

alto

54

0.7

VIL Tensione di ingresso

V

74

0.8

a livello basso

-1.5

VI Tensione di taglio di Vcc = min.

V

II = -18 mA

ingresso

54

2.5

3.4

VOH Tensione di uscita a Vcc =min.

V

VIL = VIL max

74

2.7

3.4

livello alto

IOH =max.

54

0.25

0.4

VOL Tensione di uscita a Vcc =min.

V

VIL = 2 V

74

0.35

0.5

livello basso

IOH =max.

0.1

II Corrente di ingresso Vcc = max

mA

alla

massima VI = 5.5 V

tensione di ingresso

20

IIH Corrente di ingresso a Vcc = max

µA

VIH = 2.7 V

livello alto

-0.36 mA

IIL Corrente di ingresso a Vcc = max

VIL = 0.4 V

livello basso

54

-6

-40

IOS Corrente di uscita in Vcc = max

mA

74

-5

-42

cortocircuito ***

* Per le condizioni di misura indicate con min e max usare i valori appropriati riportati nelle condizioni di

funzionamento raccomandate.

** Tutti i valori tipici si riferiscono a Vcc = 5 V, TA = 25 °C

*** Non cortocircuitare piu’ di un’uscita

Le due serie, 54 e 74, differiscono in quanto la prima, detta serie industriale, e’ in grado di

funzionare in condizioni meno pesanti della serie 54 che e’ quella a norme militari. Per tutte le

considerazioni che seguono si fara’ riferimento al dispositivo della serie industriale. (LS7410).

Il primo parametro su cui conviene fissare l’attenzione e’ la IOH, corrente di uscita allo stato

alto, pari a –400 µA. Cio’ sta ad indicare che allo stato alto si puo’ prelevare dall’uscita una corrente

massima di 400 µA senza che alcuna caratteristica del dispositivo ne risulti compromessa.

Analogamente la IOL, pari a 8 mA, indica che allo stato basso il dispositivo e’ in grado di

assorbire questa corrente senza compromettere le sue caratteristiche.

Si vede immediatamente che il comportamento della porta e’ assolutamente dissimmetrico nei

due stati logici.

Altro parametro di interesse e’ la VIL, massima tensione di ingresso sicuramente riconosciuta

come tensione dello stato basso e pari a 0,8 V; analogamente e’ assegnata la VIH, pari a 2 V, con il

significato di minima tensione di ingresso sicuramente riconosciuta come tensione dello stato alto.

Si individua pertanto una fascia di incertezza situata nell’intervallo di tensione compreso tra 0,8 e 2

V.

111

Capitolo III

I circuiti logici.

Analoghi parametri vengono assegnati con riferimento all’uscita. La VOL, pari a 0,4 V, assume

il significato di massima tensione di uscita allo stato basso, nelle peggiori condizioni di

funzionamento possibili, mentre la VOH, pari a 2,7 V e’, sempre nelle peggiori condizioni, la

minima tensione di uscita allo stato alto. Si noti che questi ultimi due parametri sono specificati in

corrispondenza a correnti d’uscita pari alle massime correnti consentite per il componente.

Esistono infine le correnti di ingresso IIL = -0,36 mA e IIH = 40 µA, cioe’ le correnti

rispettivamente erogate o assorbite dall’ingresso (valori massimi) quando tale ingresso si trovi alla

tensione VIL e VIH. Anche per l’ingresso vi e’ quindi un’asimmetria delle correnti nei due stati; e’

questo un comportamento tipico di tutte le famiglie bipolari, cioe’ di quelle logiche che vengono

realizzate con transistori a giunzione.

L’esame di questi parametri permette di verificare la compatibilita’ del dispositivo. Infatti

VOH > VIH

VOL < VIL

Il margine di rumore apparente nei due stati logici e’:

VNH = VOH – VIH = 0,7 V

VNL = VIL –VOL = 0,4 V

La compatibilita’ tra dispositivi logici permette di definire in modo piu’ preciso il concetto di

famiglia logica. Appartengono cioe’ alla stessa famiglia logica circuiti elettricamente compatibili

realizzati in una stessa tecnologia.

Sotto quest’ultimo punto di vista possono allora essere individuate due categorie fondamentali di

famiglie logiche. Esistono cioe’ le famiglie logiche bipolari, realizzate con transistori a giunzione e

quelle MOS che utilizzano invece i transistori ad effetto di campo a gate isolato.

Esistono certamente anche realizzazione, quali ad esempio le BiCMOS, che utilizzano,

ricavandoli dello stesso substrato, sia transistori bipolari che MOS, ma normalmente i dispositivi cosi’

realizzati sono di uso specifico e non formano famiglia logica.

La piu’ diffusa famiglia bipolare attualmente in uso e’ la TTL (transistor – transistor logic),

presente sul mercato in un gran numero di varianti. Tra i dispositivi MOS, la famiglia di gran lunga piu’

diffusa e’ la CMOS, famiglia che utilizza contemporaneamente MOS a canale N e P ricavati dallo

stesso substrato e anch’essa presente sul mercato in un gran numero di varianti.

Rimanendo per il momento nell’ambito delle famiglie bipolari possono venir citate, piu’ per

ragioni storiche che per altro

•

•

•

La famiglia RTL (resistor – transistor logic)

La famiglia DTL (diode – transistor logic)

La famiglia HTL (hig thresold logic)

Sono viceversa a tutt’oggi impiegate e con un notevole grado di diffusione

•

•

La famiglia TTL (transistor – transistor logic)

La famiglia ECL (emitter coupled logic)

Di queste la prima, in relazione al grandissimo successo che il mercato le ha tributato, ha generato

tutta una serie di sottofamiglie in ciascuna delle quali una delle caratteristiche (ad esempio la velocita’

operativa o la dissipazione di potenza) e’ stata ottimizzata.

112

Capitolo III

I circuiti logici.

La famiglia ECL, talvolta chiamata anche CML (current mode logic) e’ una famiglia ad elevata

velocita’ ed e’ l’unica famiglia bipolare che nasce non saturata.

Nel campo dei dispositivi MOS si possono citare le famiglie “storiche” PMOS, NMOS e

CMOS4XXX. Quest’ultima, anziana ormai per piu’ di vent’anni, e’ stata la prima famiglia MOS a

simmetria complementare ed ha avuto una larghissima diffusione. Al giorno d’oggi esistono in pratica

solo famiglie in tecnologia CMOS, non appartenenti tuttavia alla 4XXX. Esse pur conservando i

vantaggi della famiglia capostipite, sono maggiormente compatibili con le altre famiglie logiche, in

particolare con quella bipolare TTL e sono presenti sul mercato in numerose varianti.

3.6) Cenni sulle famiglie bipolari “storiche”.

3.6.1) La famiglia RTL

I circuiti logici RTL sono stati storicamente i primi ad essere fabbricati ed usano solo transistori e

resistenze per realizzare il circuito base della famiglia. Un tipico circuito RTL e' riportato in fig. 3.20 e

realizza in logica positiva la funzione NOR.

R2

C

A

R1

A

R

B

B

C

1

figura 3.20

Nelle prime realizzazioni la tensione di alimentazione era compresa tra 3.0 e 3.6 volt e i valori

circuitali erano:

R1 = 450 ohm

R2= 640 ohm

I tempi di propagazione erano abbastanza buoni, aggirandosi sui 12 nsec; la dissipazione non

eccessiva, essendo di circa 10 mW per gate.

Quali aspetti negativi possono essere citati la bassa escursione del segnale, la non eccezionale

immunita' al rumore, il basso fan-out (max. 5) e il basso fan-in (max. 4).

In verita' da questo circuito base sono state sviluppate molte versioni modificate, di cui le piu'

importanti sono la DCTL (direct coupled transistor logic), logica ad accoppiamento diretto, senza

resistenza di base, e la RCTL, in cui l'accoppiamento e' di tipo RC, tale da accelerare la commutazione,

come illustrato a tratteggio in fig. 3.20.

113

Capitolo III

I circuiti logici.

I ritardi di propagazione sono comunque sempre rimasti compresi tra i 10 e i 30 nsec per i gate e

tra 20 e 50 nsec per i flip - flop, le dissipazioni tra i 10 e i 25 mW.

3.6.2) La famiglia DTL

La logica a diodi e transistori e' una delle piu' anziane, ma a differenza di quanto e' accaduto con

altre famiglie, quali ad esempio la RTL, l'introduzione di componenti piu' moderni non l'ha fatta

scomparire del tutto. Parecchie generazioni DTL si sono succedute e per un certo periodo questa e' stata

la famiglia piu' popolare. Da essa e' derivata tuttavia la famiglia TTL e, alla luce delle migliori

prestazioni di quest'ultima, la logica DTL non e' piu' stata usata nei nuovi progetti. D'altra parte, a causa

della compatibilita' dei livelli logici e della tensione di alimentazione, si trovano ancora circuiti in cui

coesistono le due famiglie. Il circuito base e' illustrato in fig. 3.21 e realizza in logica positiva la

funzione logica NAND.

1.6 K

D1

2.0 K

C

D3

A

A

B

C

T1

B

5K

D2

figura 3.21

Se ambedue gli ingressi A e B sono al livello alto, i diodi D1 e D2 sono interdetti. Il diodo D3 e'

invece polarizzato direttamente e fa si' che T1 si porti in saturazione. Se invece almeno uno dei due

ingressi si porta a livello basso, il corrispondente diodo passa in conduzione e drena verso massa la

corrente che circola sul resistore da 1.6 Kohm, facendo interdire T1. Il diodo D3 ha lo scopo di

compensare le cadute su D1 e D2 quando sono in conduzione, in modo da assicurare buone condizioni

di funzionamento all'interdizione.

La tensione di alimentazione nominale per la logica DTL e' 5 V e i livelli logici sono:

VOL = 0.6 V

VOH = 2.6 V

VIL = 1.3 V

VIH = 1.8 V

Pertanto i margini di rumore apparente sono:

NH = 0.8 V

NL = 0.7 V

e possono essere considerati discreti.

Il fan-out medio della famiglia e' 8, anche se di essa fanno parte particolari gate ad alto fan-out

(30).

114

Capitolo III

I circuiti logici.

La dissipazione si aggira sui 5 mW per gate nel caso normale, e sui 20 mW nel caso di gate ad

alto fan-out. Il ritardo di propagazione e' mediamente 15 - 20 nsec. Infine, data la struttura degli stadi di

uscita, e' ammesso il wired-or.

3.6.3) La famiglia HTL

La famiglia logica ad alta immunita' (high thresold logic) e' una famiglia sviluppata per impieghi

particolari. La sua principale caratteristica e' un'elevata immunita' al rumore e per tale motivo viene

impiegata in ambienti industriali dove dispositivi elettromeccanici possono dar luogo a transienti di

tensione di ampiezza elevata. Il circuito fondamentale di un elemento HTL e' illustrato in fig. 3.22 e

ricorda molto da vicino la struttura degli elementi DTL. Ci sono tuttavia da notare i valori

relativamente elevati di R1, R2, R3 e il valore nominale della tensione di alimentazione che e' di 15 V.

Il diodo zener fa salire la soglia di commutazione a circa 7 volt. Piu' esattamente i livelli garantiti di

ingresso e di uscita sono:

VOL = 1.5 V

VOH = 12.5 V

VIL = 6 V

VIH = 8 V

Il margine di rumore, sia allo stato alto che allo stato basso, e' quindi di 4.5 volt. Il fan-out tipico

della famiglia e' 10, la dissipazione si aggira sui 30 mW per gate.

R

2

15 K

D1

A

R

4

R6

3K

T1

D

2

D

1.5 K

T2

R1

12 K

B

R3

1K

C

D4

A

B

C

3

T3

R5

5K

figura 3.22

I tempi di propagazione non sono ovviamente dei migliori; sono anzi in assoluto i piu’ alti tra

tutti quelli delle famiglie logiche, potendo giungere fino a 150 nsec. Tale fatto d'altra parte non puo'

115

Capitolo III

I circuiti logici.

essere considerato un dato del tutto negativo in quanto migliora le caratteristiche di immunita' al

rumore in corrente alternata.

3.7) La famiglia TTL.

La famiglia TTL e’, assieme alla CMOS, quella piu’ largamente usata al giorno d’oggi. Tutti i

principali fabbricanti hanno oggi una linea di produzione TTL, che comprende, oltre alla famiglia TTL

standard, tutta una serie di sottofamiglie, ciascuna delle quali ottimizza una particolare caratteristica.

3.7.1) La sottofamiglia TTL standard.

In fig. 3.23 e' riportato il circuito dell'elemento fondamentale TTL, che in logica positiva realizza

la funzione logica NAND. Esso opera con una singola alimentazione di 5 volt.

L'elemento standard e' compatibile con qualsiasi altro elemento appartenente alle sottofamiglie e

con gli elementi della logica DTL.

invertitore

ingresso

R1

4 kΩ

A

B

R2

1.6 k Ω

T1

T2

uscita

Vcc (+ 5 volt)

R4

130 Ω

T4

D1

T

R3

3

1 kΩ

figura 3.23

Il ritardo di propagazione e' compreso tra 5 e 10 nanosecondi, la dissipazione e' di 10 mW per

gate, mentre la massima frequenza operativa si aggira sui 35 MHz.

Il circuito puo' essere funzionalmente suddiviso in tre parti: uno stadio di ingresso associato ad un

transistore multiemettitore, un invertitore di fase e uno stadio di uscita atto ad ottenere i livelli di

tensione e di impedenza stabiliti in sede di progetto.

Spesso tra gli ingressi e la massa sono connessi dei diodi di protezione con la funzione di tosare

eventuali segnali negativi applicati all'ingresso.

116

Capitolo III

I circuiti logici.

Quando l'uno o l'altro dei due ingressi e' al livello basso il transistore T1 diviene conduttore e di

conseguenza nessuna corrente circola nella base di T2. T2 pertanto e' interdetto; la sua tensione di

collettore coincide in pratica con la tensione di alimentazione, mentre la sua tensione di emettitore e' in

pratica nulla. In tale situazione T4 passa in conduzione, T3 si interdice e l'uscita si porta a livello alto.

Nella pratica lo stadio di uscita puo' assumere diverse configurazioni, ciascuna delle quali offre

vantaggi e svantaggi. Non si ritiene tuttavia opportuno in questa sede condurre un esame dettagliato

degli stadi di uscita. Bastera’ ricordare che le principali modificazioni riguardano la struttura della parte

alta dello stadio di uscita, che viene spesso realizzata con la connessione di tipo Darlington, come

illustrato in figure 3.24.

Vcc

Uscita

figura 3.24

Questo tipo di connessione permette di ottenere una minor impedenza di uscita allo stato alto e

quindi di pilotare senza compromettere eccessivamente le caratteristiche di velocita’ carichi capacitivi

anche non trascurabili.

Un ulteriore tipo di stadio di uscita e’ quello a collettore aperto (figura 3.25), con il quale tuttavia

si perdono tutti i vantaggi del totem-pole. Per contro si possono connettere direttamente due o piu’

uscite, realizzando il “wired – OR”.

Uscita

figura 3.25

Se infatti si prende in esame cosa accade quando due uscite a collettore aperto vengono connesse

assieme e riportate all’alimentazione tramite un opportuno resistore, come appare nello schema di

figura 3.26,

117

Capitolo III

I circuiti logici.

U

A

B

C

D

y = C.D

y = A.B

2

1

figura 3.26

ci si accorge che l’uscita U puo’ trovarsi allo stato alto solo se sua y1 che y2 si trovano allo stato alto. In

altre parole

U = y1 . y 2 = A. B. C. D = A. B + C. D

Si riesce cioe’ ad ottenere una funzione complessa al prezzo di una semplice connessione

metallica.

A qualsiasi tipo di uscita puo' essere aggiunta una resistenza esterna di "pull-up", connessa tra

uscita e VCC in modo da far avvicinare la tensione di uscita allo stato alto a quella di alimentazione.

Tuttavia solo i circuiti 3,4,5 possono essere spinti piu' in alto della tensione di alimentazione o una

resistenza di “pull-down” in modo da far avvicinare la tensione di uscita dello stato basso a quella di

massa.

a) Caratteristica di trasferimento.

In fig. 3.27 e' riportato il grafico della tensione di uscita in funzione della tensione di ingresso,

cioe' la caratteristica di trasferimento, in condizioni statiche.

"1"

H

4.0

3.0

J

2.0

1.0

L

"0"

0

0.4

0.8

1.2

1.6

figura 3.27

118

2.0

2.4

2.8

Capitolo III

I circuiti logici.

E' importante far rilevare che la curva di trasferimento varia in modo non trascurabile con la

temperatura, la tensione di alimentazione e il carico. La curva illustrata si riferisce ad una temperatura

di 35 gradi, ad una tensione di alimentazione di 5 volt e ad un fan-out pari a 10.

Con riferimento alla fig. 3.23, l'analisi puo' essere condotta pensando di riunire i due ingressi A e

B. Man mano che la tensione applicata cresce, a partire da 0 volt, la corrente di base di T1 viene

gradualmente deviata dagli emettitori al collettore; di conseguenza T2 inizia a condurre. La tensione di

ingresso alla quale T2 esce dall'interdizione e' compresa tra 0.7 e 0.8 volt (punto H della caratteristica).

Dal punto H al punto J il transistore T2 opera in regime lineare, con un guadagno di tensione

determinato dal rapporto tra il resistore di collettore e quello di emettitore. La tensione di base di T4

gradualmente diminuisce portando il transistore verso l'interdizione. In definitiva nel tratto H-J l'uscita

ripete l'andamento della tensione di collettore di T2, in quanto T4 funziona da inseguitore.

Arrivati al punto J comincia a condurre il transistore T3, aprendo una via a bassa impedenza verso

massa per la corrente di emettitore di T2; come risultato aumentano il guadagno di tensione di T4 e la

pendenza della caratteristica.

Tra i punti J e L i transistori T2, T3 e T4 conducono contemporaneamente; solo al punto L T4 si

interdice. A tale istante la tensione di uscita e' approssimativamente pari a 0.2 volt e la transizione dallo

stato alto a quello basso e' completata.

Da quanto esposto si possono trarre due importanti considerazioni. La prima e' che nel tratto J-L

vi e' un percorso a bassa impedenza tra VCC e massa, formato da R4, T4 , D1, T3, sede di una corrente

non trascurabile. E' questo uno degli svantaggi della famiglia TTL, in quanto durante il funzionamento

si hanno degli impulsi di corrente, che, oltre ad aumentare la potenza dissipata al crescere della

frequenza, sono una sorgente di rumore che puo' interferire con il normale funzionamento del circuito.

La seconda considerazione e' che durante il funzionamento tutti i transistori, con l'eccezione di

T4, passano dall'interdizione alla saturazione e viceversa, limitando pertanto, come avviene in ogni

logica saturata, la velocita' operativa.

b) Tensioni e correnti di ingresso e di uscita.

La caratteristica di trasferimento appena esaminata fornisce alcune interessanti informazioni sul

valore delle tensioni di ingresso e di uscita nei due stati.

Dalla curva di fig. 3.27 si puo' vedere che se gli ingressi sono pilotati ad una tensione superiore a

0.8 volt il circuito inizia a commutare verso l'uscita logica 0. In modo del tutto simile, se uno qualsiasi

degli ingressi scende ad una tensione inferiore a 1.4 volt l'uscita inizia a commutare verso il valore

logico 1. In prima approssimazione si potrebbe quindi affermare che se l'ingresso e' mantenuto al di

fuori della zona compresa tra 0.8 e 1.4 volt, l'uscita del gate definisce senza ambiguita' i valori logici 1

e 0.

La precisa definizione dei valori limite e' tuttavia complicata dal fatto che la curva varia con la

temperatura, la tensione di alimentazione e il fan - out.

Per tale ragione e' prassi comune che i costruttori di circuiti integrati garantiscano i valori

massimi e minimi delle tensioni di ingresso e di uscita nelle peggiori condizioni di funzionamento. E'

stato gia' chiarito in precedenza il significato di tali tensioni, che per la famiglia TTL standard valgono:

VIH = 2 volt

VIL = 0.8 volt

VOH = 2.4 volt

VOL = 0.4 volt

119

Capitolo III

I circuiti logici.

Ugualmente importanti sono le correnti che entrano o escono da un elemento logico nei due stati.

La fig. 3.28 mostra il flusso di corrente attraverso gli ingressi e l'uscita di due porte NAND nelle

due possibili condizioni di lavoro. Quando l'uscita della porta 1 e' allo stato alto la corrente circola dal

transistore T4 della porta 1 verso l'emettitore di T1 della porta 2. Quando la porta 1 e' nello stato basso

la corrente circola dall'emettitore di T1 della porta 2 all'emettitore di T3 della porta 1.

La corrente di ingresso allo stato alto e' garantita inferiore a 40 microampere, valore trascurabile

nel determinare il fan-out, mentre la corrente erogata dall'ingresso allo stato basso e' garantita inferiore

a 1.6 milliampere e deve richiudersi a massa attraverso T3.

Pertanto affinche' sia assicurato un fan-out pari a 10 T3 deve poter assorbire una corrente di 16

milliampere senza che la sua tensione di saturazione VCES salga a valori al di sopra di VOL = 0.4 volt.

T4

R1

1

D1

T3

I OH

I OL

Flusso di corrente

0

R2

I IH

I IL

T1

T2

figura 3.28

In definitiva si ha:

IIH < 40 mA

intendendo con IIH la corrente che fluisce in un ingresso quando ad esso e' applicata una tensione Vi ≥ 2

volt, mentre

IIL < 1.6 mA

e' la corrente che esce da un ingresso quando ad esso e' applicato un livello logico 0, cioe' una tensione

di ingresso inferiore a 0.8 volt. Analogamente

IOH ≥ 0.4 mA

120

Capitolo III

I circuiti logici.

e' la corrente che puo' essere fornita dall'uscita a livello logico alto senza che la sua tensione scenda al

di sotto di VOH = 2.4 volt. Il valore relativo all'uguaglianza e' il minimo necessario a garantire un fanout pari a 10.

Sempre per garantire un fan - out pari a 10 e' necessario che :

IOL ≥ 16 mA

intendendo ovviamente, come gia' e' stato detto, che IOL sia la corrente che puo' essere iniettata

nell'uscita allo stato basso senza che la tensione di uscita salga al di sopra di 0.4 volt.

c) Impedenze di ingresso e di uscita.

Per quanto riguarda l'impedenza di ingresso di una porta TTL si possono fare le seguenti

considerazioni. Per tensioni di ingresso superiori a 2 volt essa e' molto alta; vale circa 4 kohm tra +1 e 0.5 volt, mentre per tensioni inferiori e' molto bassa a causa del diodo di protezione connesso tra

ingresso e massa. La caratteristica di ingresso e' riportata in fig. 3.29.

mA

80

70

60

50

diodo di

protezione

40

30

20

regione operativa normale

10

volt

-3

-2

-1

-10

1

2

3

4

5

-20

-30

figura 3.29

La caratteristica di uscita e' riportata invece in fig. 3.30. Si puo' vedere che l'impedenza d'uscita e'

di basso valore in ambedue gli stati. Nello stato basso l'impedenza e' determinata dalla resistenza offerta

dal transistore T3 in condizioni di saturazione, pari a circa 8 ohm. A correnti elevate, iniettate

dall'esterno nel terminale di uscita, in particolare se si opera a basse temperature, il transistore puo'

uscire di saturazione facendo salire l'impedenza di uscita. Allo stato alto viceversa l'impedenza d'uscita

e' determinata in pratica dal valore di R4.

121

Capitolo III

I circuiti logici.

mA

90

80

Stato basso

70

60

50

~ 8Ω

Rsat =

40

30

20

10

volt

-1

-10

1

2

3

-20

T

-30

5

4

6

non saturato

stato alto

-40

-50

4

~ R

= 4

-60

figura 3.30

E' interessante notare che, commutando dallo stato basso a quello alto, la struttura a totem-pole

dello stadio di uscita consente, a causa della sua bassa impedenza d'uscita, un rapido raggiungimento

delle condizioni di regime anche in presenza di carichi capacitivi. In questo caso tuttavia, le correnti,

relativamente rilevanti, circolano anche sulla rete di distribuzione dell'alimentazione, che deve quindi

essere corta ed adeguatamente disaccoppiata.

Inoltre, se durante la transizione dallo stato basso allo stato alto T4 passa in conduzione prima che

T3 sia interdetto, come normalmente avviene, si ha un assorbimento di corrente impulsivo di breve

durata, i cui effetti si propagano comunque attraverso la rete di alimentazione.

3.7.2) La sottofamiglia low power TTL .

In un rilevante numero di applicazioni i circuiti TTL standard sono notevolmente piu' veloci del

necessario; si e' ritenuto pertanto opportuno rinunciare al sovrappiu' di velocita' in favore di una

riduzione della potenza dissipata. E' stata pertanto introdotta dai costruttori, quasi contemporaneamente

alle porte TTL standard, la sottofamiglia low power TTL (LPTTL).

Il circuito e' identico a quello della TTL standard, con l'unica eccezione che i valori dei resistori

risultano moltiplicati per un fattore, che a seconda del fabbricante e' compreso tra 4 e 10. Di

conseguenza la potenza dissipata diminuisce dal 75% al 90% mentre il tempo di propagazione aumenta

di 3-4 volte.

Valori tipici sono 1 mW per gate per quanto riguarda la potenza dissipata, 33 nsec per il tempo di

propagazione e 3 MHz per la velocita' massima.

E' bene far rilevare che una riduzione del consumo non si riflette solamente sulla dimensione e

sul costo dell'alimentatore, ma porta anche ad una semplificazione del progetto termico del sistema per

la minor quantita' di calore sviluppato.

Inoltre, poiche' i dispositivi LPTTL utilizzano i medesimi involucri degli elementi standard, le

temperature alle giunzioni sono inferiori a tutto favore di una maggior affidabilita'.

122

Capitolo III

I circuiti logici.

Dal punto di vista del rumore vi sono due distinti vantaggi; la riduzione delle correnti in gioco fa

si' che l'autogenerazione di rumore risulti notevolmente diminuita, permettendo di usare un minor

numero di condensatori di disaccoppiamento e semplificando il progetto del circuito stampato. Oltre a

cio' la minor velocita' di commutazione fa si' che l'immunita' al rumore in corrente alternata sia

superiore.

Il fan-out nell'ambito della sottofamiglia e' 10; tuttavia e' bene far notare che la LPTTL e'

perfettamente compatibile con qualsiasi altro elemento TTL. Per un elemento LPTTL che pilota un

TTL standard il fan-out sara' compreso tra 1 e 4, mentre nel caso di un TTL standard che pilota un

LPTTL il fan-out sara' compreso tra 25 e 60.

A causa del ridotto valore della correnti di ingresso degli elementi LPTTL, essi costituiscono una

buona interfaccia verso i circuiti MOS le cui impedenze di uscita sono generalmente abbastanza alte.

In conclusione la LPTTL e' la piu' facile da impiegare tra tutte le sottofamiglie TTL e andrebbe

utilizzata in tutte quelle occasioni in cui non risulti penalizzata dalla sua ridotta velocita'.

3.7.3) La sottofamiglia high speed TTL .

Dopo l'introduzione della famiglia TTL la domanda dei produttori di calcolatori, di

strumentazione e di apparecchi di comunicazione ha spinto tale famiglia a evolversi verso l'alta

velocita', facendo nascere dapprima la high speed TTL (HTTL) e successivamente la Schottky TTL

(STTL), di caratteristiche ancora migliori.

V cc

2.8 k Ω

T3

T1

T4

Uscita

T2

Ingresso

D1

56 Ω

760 Ω

D2

T

470 Ω

5

4 kΩ

figura 3.31

Il circuito base HTTL, riportato in fig. 3.31, nasce da quello della TTL standard con l'aggiunta di

una coppia Darlington in sostituzione del transistore superiore del totem-pole di uscita e con la

diminuzione del valore di tutte le resistenze.

La coppia Darlington aumenta la velocita' con cui la corrente di T4 puo' essere commutata; in

aggiunta la diminuzione dei valori resistivi minimizza l'effetto delle capacita' parassite, aumentando

pertanto la velocita' con cui il circuito puo' cambiare stato.

Valori tipici per tale sottofamiglia sono 6 nanosecondi per il tempo di propagazione, 50 MHz

come velocita' massima e 22 mW per gate come potenza dissipata.

123

Capitolo III

I circuiti logici.

Al giorno d'oggi i dispositivi HTTL sono usati quasi esclusivamente per ridurre i ritardi in alcuni

itinerari critici in sistemi realizzati con elementi TTL standard; presentano l'inconveniente di una

maggior potenza dissipata, di una maggior autogenerazione di rumore e rendono piu' critica la

disposizione dei componenti sulla scheda a circuito stampato, per motivi che verranno illustrati

brevemente piu' avanti.

3.7.4) La sottofamiglia TTL Schottky.

Le varie famiglie e sottofamiglie fin qui prese in esame sono tutte relative a logiche saturate; i

transistori cioe' sono portati in conduzione con una corrente di base sufficiente a condurli al limite della

saturazione anche con il guadagno di corrente minimo e nelle peggiori condizioni di temperatura e di

carico. Di conseguenza un transistore riceve in media una corrente di base di gran lunga superiore a

quella necessaria e si addentra percio' profondamente nella zona di saturazione. Si forma un accumulo

di portatori di minoranza nella zona di base e per portare poi nuovamente il transistore in interdizione e'