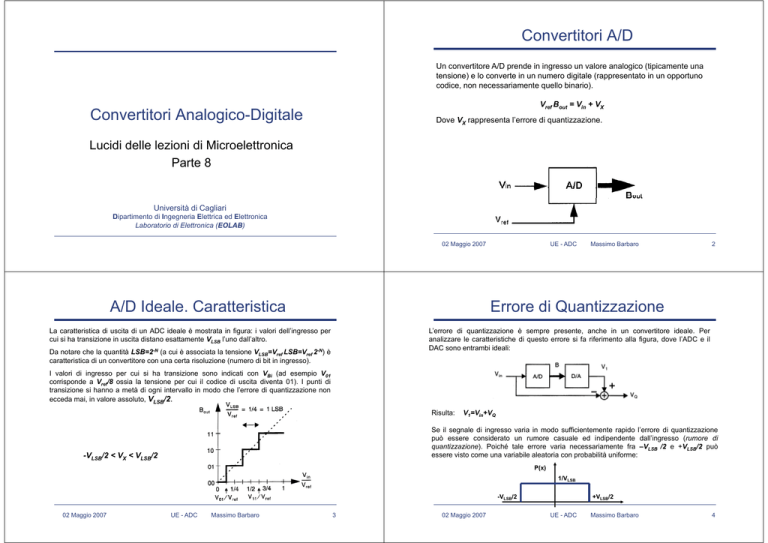

Convertitori A/D

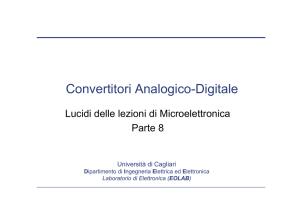

Un convertitore A/D prende in ingresso un valore analogico (tipicamente una

tensione) e lo converte in un numero digitale (rappresentato in un opportuno

codice, non necessariamente quello binario).

Vref Bout

o t = Vin + VX

Convertitori Analogico-Digitale

Dove VX rappresenta l’errore di quantizzazione.

Lucidi delle lezioni di Microelettronica

Parte 8

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

02 Maggio 2007

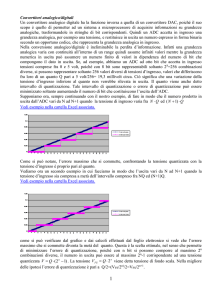

A/D Ideale. Caratteristica

UE - ADC

Massimo Barbaro

2

Errore di Quantizzazione

La caratteristica di uscita di un ADC ideale è mostrata in figura: i valori dell’ingresso per

cui si ha transizione in uscita distano esattamente VLSB l’uno dall’altro.

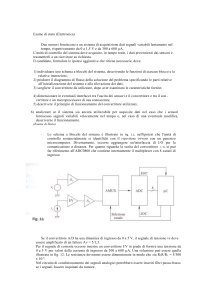

L’errore di quantizzazione è sempre presente, anche in un convertitore ideale. Per

analizzare le caratteristiche di questo errore si fa riferimento alla figura, dove l’ADC e il

DAC sono entrambi ideali:

Da notare che la quantità LSB=2-N (a cui è associata la tensione VLSB=Vref LSB=Vref 2-N) è

caratteristica di un convertitore con una certa risoluzione (numero di bit in ingresso).

g

per cui si ha transizione sono indicati con VBi ((ad esempio V01

I valori di ingresso

corrisponde a Vref/8 ossia la tensione per cui il codice di uscita diventa 01). I punti di

transizione si hanno a metà di ogni intervallo in modo che l’errore di quantizzazione non

ecceda mai, in valore assoluto, VLSB/2.

Risulta:

V1=Vin+VQ

Se il segnale di ingresso varia in modo sufficientemente rapido l’errore di quantizzazione

può

ò essere considerato

id t un rumore casuale

l ed

d indipendente

i di

d t dall’ingresso

d ll’i

(

(rumore

di

quantizzazione). Poiché tale errore varia necessariamente fra –VLSB /2 e +VLSB/2 può

essere visto come una variabile aleatoria con probabilità uniforme:

-VLSB/2 < VX < VLSB/2

P( )

P(x)

1/VLSB

-V

VLSB/2

02 Maggio 2007

UE - ADC

Massimo Barbaro

3

02 Maggio 2007

+VLSB/2

UE - ADC

Massimo Barbaro

4

Rumore di Quantizzazione

SNR dell’ADC Ideale

La media del rumore di quantizzazione è evidentemente nulla:

Il rapporto segnale/rumore risulta quindi:

⎛V

SNR = 20 log⎜⎜

⎝V

+∞

= ∫ xP ( x) dx = 0

V

in ( rms )

−∞

Q ( avg )

Q ( rms )

La potenza quadratica media del rumore di quantizzazione è data da:

V

Q ( rms )

=

+∞

V

LSB

LSB

−∞

SNR = (6.02N + 1.76) dB

La relazione precedente mette in relazione lo SNR con la risoluzione del convertitore: per

ogni aumento di un bit abbiamo un aumento del SNR di circa 6dB. Questo vale nel caso di

ingresso full-scale, se l’ingresso non ha ampiezza pari al range del convertitore lo SNR

diminuirà di conseguenza.

Si p

può allora calcolare il rapporto

pp

segnale/rumore

g

nel caso di ingresso

g

sinusoidale con

ampiezza picco-picco pari al range di ingresso (Vref) dell’ADC.

Vin = Vref/2 sin ((2π/ T) t)

Se

N

REF

Questo risultato lo si ottiene ricordando che VLSB=VLSB 2-N, da cui:

∫ x P( x)dx = 12

2

⎞

⎛ V (2 12 ) ⎞

⎛ 3 ⎞

⎟ = 20 log⎜⎜

⎟⎟ = 20 log⎜⎜ 2 ⎟⎟

⎟

⎝ 2 ⎠

⎝ V / 12 ⎠

⎠

la potenza del segnale di ingresso risulta pari a:

V

2 2

REF

02 Maggio 2007

UE - ADC

Massimo Barbaro

5

02 Maggio 2007

A/D: Misura Prestazioni

UE - ADC

Massimo Barbaro

6

A/D: Misura Prestazioni

I parametri rispetto ai quali si misurano le prestazioni di un ADC non ideale

sono:

DNL (Differential Nonlinearity): E’ la massima differenza fra la distanza di

due punti di transizione adiacenti ed il valore ideale (VLSB)

Risoluzione: Numero di bit in uscita N

INL (Integral Nonlinearity): E’ la massima deviazione fra i valori di uscita e la

retta che passa per i punti estremi della caratteristica.

Offset error: La differenza fra il valore di ingresso per cui in uscita si ha la

transizione al codice 00..001 ed il valore ideale pari a VLSB/2 (Vref / 2N+1)

Missing Codes: E’ l’equivalente della monotonicità nei DAC. Si parla di

missing codes quando non tutti i possibili codici di uscita vengono generati al

g

in tutto il range

g disponibile.

p

variare dell’ingresso

Gain Error: Di quanto si discosta la pendenza della retta che passa per i

punti estremi della caratteristica di uscita dalla pendenza ideale (in genere

unitaria).

Tempo di Conversione: E’ il tempo necessario per effettuare la conversione

(che limita la massima frequenza di campionamento). In convertitori con

architetture pipeline il tempo di conversione per il singolo campione può non

coincidere col periodo minimo tempo di campionamento (la latency aumenta il

tempo di conversione per il singolo campione).

Gli errori di offset e gain sono lineari e quindi non gravi, in quanto non

introducono distorsione in uscita

SNR e SNDR:

SNDR Rapporto

R

segnale/rumore

l /

e segnale/(rumore+distorsione)

l /(

di

i

)

02 Maggio 2007

UE - ADC

Massimo Barbaro

7

02 Maggio 2007

UE - ADC

Massimo Barbaro

8

A/D: Misura Prestazioni

A/D: Misura Prestazioni

Sampling Time Uncertainty: E’ l’incertezza nel tempo esatto di campionamento,

legata all’aperture jitter visto per i campionatori. Tale incertezza causa un errore nel

valore convertito che può essere stimato.

stimato

Effective Number of Bits (ENOB): E’ il numero effettivo di bit del

convertitore. Infatti se il convertitore di risoluzione N ha un certo SNDR

(dovuto globalmente alle sue non idealità, fra cui le non linearità che

introducono distorsione), si può dire che tale convertitore è equivalente ad

un convertitore ideale ma con un numero inferiore M di bit che avrebbe un

SNR 6 02M 1 76

SNR=6.02M+1.76.

Se l’ingresso è un’onda sinusoidale con ampiezza pari al full-range del convertitore:

Vin = Vref/2 sin ((2πf t))

un errore nell’istante di campionamento porterà ad un errore nel valore campionato

pari a:

∆V = V

V’ ∆t

ENOB = (SNDR – 1.76)

1 76) / 6

6.02

02

L’errore massimo si ha in corrispondenza della massima derivata (ossia nei punti di

attraversamento dello zero del seno):

∆Vmax = Vref πf ∆t = VLSB2Nπf ∆t

Si vuole ovviamente che tale errore sia inferiore a VLSB quindi:

∆t < 1/(2Nπf)

Nel caso di un segnale di 1MHz in ingresso ad un convertitore a 16 bit si ottiene un

limite di 5ps.

02 Maggio 2007

UE - ADC

Massimo Barbaro

9

02 Maggio 2007

Tipologie di Convertitori

UE - ADC

Massimo Barbaro

10

Dual-Slope

Dual-Slope: veramente molto lenti (tconv=2N/fs), richiedono pochi componenti analogici

(nAN = 1-3), elevata risoluzione (N<21bit), richiedono circuiteria digitale non

estremamente complessa.

complessa

Il convertitore dual-slope è utilizzato per strumenti di misura in quanto molto preciso (fino a

per convertire segnali

g

in continua).

)

20 bit)) ma anche molto lento ((usato p

Si basa su una doppia integrazione: si fa caricare la capacità C1 con una carica

proporzionale all’ingresso e poi si misura il tempo necessario per scaricare la stessa

capacità usando una corrente costante e nota.

Ciclici / SA (ad Approssimazioni Successive): lenti (tconv=N/fs), richiedono pochi

componenti analogici (nAN = 1), media risoluzione (N<15bit), richiedono circuiteria

digitale complessa

Convertitori Flash: molto veloci (tconv=1/fs), richiedono molti componenti analogici

(nAN = 2N), poco pratici per convertitori ad alta risoluzione (N<10bit), richiedono

circuiteria digitale

Pipeline: molto veloci (tconv=1/fs) ma con uscita ritardato rispetto all’ingresso

(tdelay=N/fs), richiedono un numero medio di componenti analogici (nAN = N), media

risoluzione (N<15bit),

(N<15bit) richiedono registri digitali a scorrimento

Sigma-Delta: molto lenti (tconv=OSR/fs), richiedono pochi componenti analogici (nAN =

1-4), risoluzione molto elevata (N<21bit), richiedono circuiteria digitale molto

complessa (filtro decimatori) proprio perché spostano la complessità dalla parte

analogica a quella digitale

02 Maggio 2007

UE - ADC

Massimo Barbaro

11

02 Maggio 2007

UE - ADC

Massimo Barbaro

12

Dual-Slope: Funzionamento

Approssimazioni Successive (1)

Il principio di funzionamento del

convertitore SA si basa sull’algoritmo di

ricerca “binary

binary search

search”.

In pratica si suddivide, via via, l’intervallo

di ricerca in due e si va a vedere in quale

intervallo cade il segnale di ingresso fino

a trovare l’approssimazione che meglio

lo rappresenta.

Il numero di passi di ricerca è pari al

numero di bit di risoluzione del

convertitore.

Fase I: lo switch S1 è connesso a -Vin e nel tempo fissato (determinato dalla logica di

p

C1 si carica alla tensione Vx=(V

( inT1 ) / ((R1C1)

controllo)) T1=2NTclk la capacità

Fase II: lo switch S1 è connesso a Vref e la capacità C1 si scarica con corrente

costante pari a –Vref / R1, la tensione Vx va a zero nel tempo T2=2NBoutTclk (in

corrispondenza del quale scatta il comparatore e la logica di controllo blocca il

conteggio) Eguagliando le cariche si ricava Bout=Vin / Vref

conteggio).

02 Maggio 2007

UE - ADC

Massimo Barbaro

13

Approssimazioni Successive (2)

UE - ADC

Massimo Barbaro

UE - ADC

Massimo Barbaro

14

Approssimazioni Successive (3)

L’implementazione pratica più

comune si basa sull’uso di un

convertitore a redistribuzione di

carica

ed

una

versione

leggermente

modificata

dell’algoritmo:

dell

algoritmo: piuttosto che

modificare ad ogni passo l’uscita

del convertitore D/A si modifica

g

e si confronta sempre

p

l’ingresso

con lo zero.

Il diagramma a blocchi è mostrato in figura. E’ necessario un S&H, un comparatore,

g

g

ed una cicuiteria digitale

g

di controllo e

un convertitore digitale/analogico

memorizzazione per conservare i bit individuati in ogni fase.

02 Maggio 2007

02 Maggio 2007

15

02 Maggio 2007

UE - ADC

Massimo Barbaro

16

SA: Implementazione

SA: Hold Mode

La parte analogica (escluso il controllo digitale) che implementa l’algoritmo precedente

((nel caso unipolare,

p

, ossia con ingresso

g

solo p

positivo)) è mostrata in figura.

g

Il

funzionamento è diviso in 3 fasi (sample mode, hold mode, bit cycling) in cui vengono

opportunamente modificate le connessioni degli switch S1, S2, S3 e bi

Hold Mode: l’amplificatore è connesso ad anello aperto (funziona da comparatore), il

plate di tutte le capacità

p

è connesso a massa in modo che (p

(per la

bottom p

conservazione della carica) sul morsetto invertente compaia la tensione –Vin. Lo switch

S1 si connette a Vref.

Sample Mode: la configurazione degli switch è quella della figura, con S1 connesso

all’ingresso e l’amplificatore connesso ad inseguitore. Tutte le capacità sono connesse

fra l’ingresso e la massa virtuale. La carica Q1 immagazzinata nel morsetto invertente

è dunque pari a Q1=-VinCTOT. Questa fase serve appunto a campionare il valore di

i

ingresso

sull bottom

b tt

plate

l t delle

d ll capacità.

ità

02 Maggio 2007

UE - ADC

Massimo Barbaro

17

SA: Bit Cycling

UE - ADC

Massimo Barbaro

UE - ADC

Massimo Barbaro

18

SA: Implementazione bipolare

Bit Cycling: a questo punto inizia la fase di approssimazioni successive vera e

propria. Uno dopo l’altro i bottom plate di ogni capacità vengono connessi a Vref.

Quando, ad esempio, b1 commuta, per la conservazione della carica deve risultare

Vx=-Vin+Vref/2 (questo perché la capacità che sta commutando è pari a 16C ossia la

metà della capacità totale). Questo valore viene confrontato con lo zero, se è

maggiore di zero significa che Vin<Vref/2, quindi b1=0, se invece è minore di zero allora

Vin>Vref/2,

/2 quindi b1=1.

b1=1 Il valore di b1 viene memorizzato nella parte digitale,

digitale se b1=0

lo switch è riportato a massa (Vx=-Vin) altrimenti viene lasciato dov’è e si procede a

trovare il bit successivo. Quando commuta b2 infatti la ∆V è pari a Vref / 4 e così via.

02 Maggio 2007

02 Maggio 2007

Per implementare il convertitore precedente in modo da convertire segnali positivi e

g

((bipolari)

p

) si p

può ricorrere ad una verione leggermente

gg

modificata del circuito.

negativi

Sample Mode: la configurazione degli switch è quella della figura, con S1 connesso

all’ingresso e l’amplificatore connesso ad inseguitore. B1 è connesso a Vref/2 mentre

le altre capacità a Vin.

Vin

19

02 Maggio 2007

UE - ADC

Massimo Barbaro

20

SA bipolare: Hold Mode

SA bipolare: Bit Cycling

Hold Mode: Tutte le capacità tranne b1 sono connesse a massa e l’opamp è connesso

ad

d anello

ll aperto.

t Sul

S l morsetto

tt invertente

i

t t la

l tensione

t

i

è Vx= –V

Vin/2 (a

( differenza

diff

del

d l caso

unipolare in cui Vx=-Vin).

02 Maggio 2007

UE - ADC

Massimo Barbaro

21

Stima dei Ritardi

UE - ADC

Massimo Barbaro

02 Maggio 2007

UE - ADC

Massimo Barbaro

22

Convertitore Algoritmico (Ciclico)

Il limite maggiore nella velocità di questa tipologia di convertitori è legato al ritardo

p

Col metodo delle costanti di tempo

p a circuito aperto

p

si p

può

dovuto alle capacità.

stimare questo ritardo come somma dei ritardi associati a ciascuna capacità, per

esempio nella fase di sample. RS1 e RS2 sono le resistenze degli switch S1 e S2

mentre R sono le resistenze degli switch corrispondenti ai bit. Ogni capacità “vede” la

stessa resistenza (RS1+RS2+R):

Tdelay=(RS1+RS2+R)2NC

02 Maggio 2007

Bit Cycling: a questo punto inizia la fase di approssimazioni successive. Si

distinguono due casi:

1) Se Vx< 0 (ossia Vin>0) 16C viene lasciata com’è, b1=1 e la conversione procede

come nel caso unipolare per b2, b3,…, bN.

2) Se Vx> 0 (ossia Vin<0) allora b1=0 e 16C viene connessa a massa. In questo

modo Vx diventa Vx=-Vin/2-Vref/4 (per la conservazione della carica). Tale valore è

diventato necesariamente positivo e da adesso in poi si può procedere come nel

caso unipolare.

Lo svantaggio rispetto al caso unipolare è che l’ingresso viene diviso per 2 rendendo

più critico il funzionamento del comparatore.

Il convertitore ciclico è simile a

quello

q

ad

approssimazioni

pp

successive ma piuttosto che

continuare a dividere per due il

riferimento

(Vref),

calcola

ll’errore

errore ad ogni ciclo e lo

moltiplica sempre per 2 per

poterlo confrontare con la

g

stessa soglia.

23

02 Maggio 2007

UE - ADC

Massimo Barbaro

24

Convertitore Algoritmico (2)

Algoritmico: Implementazione

Lo schema blocchi è mostrato in figura. Servono un S&H, un comparatore, un circuito

per il calcolo della differenza ((residuo)) e un circuito p

p

per moltiplicare

p

il residuo p

per 2. La

moltiplicazione (più differenza) è l’operazione più critica.

La moltiplicazione per 2 può essere implementata con capacità commutate. Con lo

g

e suddividendo il funzionamento in 4 fasi è p

possibile ottenere una

schema in figura

moltiplicazione molto precisa che non dipede dai valori relativi delle capacità. In pratica

si ottiene la moltiplicazione sommando due volte la stessa quantità sulla stessa

capacità.

Fase 1: L’opamp è resettato, QC1=C1Verr = Q1

QC2 = 0

02 Maggio 2007

UE - ADC

Massimo Barbaro

25

Algoritmico: Implementazione (2)

02 Maggio 2007

UE - ADC

Massimo Barbaro

26

Algoritmico: Implementazione (3)

Fase 2: L’opamp è

controreazionato con C2,,

C1 è cortocircuitata (massa

e massa virtuale) quindi la

carica precedente si

trasferisce su C2

Fase 4: L’opamp è

p

connesso ad anello aperto

(da comparatore) e le due

cariche precedenti (uguali)

si sommano su C1

QC1= Q1 + Q2 = 2 C1Verr

QC1=0

QC2=C1Verr = Q1

Questo fa sì che:

Vout= QC1 / C1= 2 Verr

Fase 3: L’opamp

p p è resettato,,

C1 è connessa all’ingresso.

L’errore viene moltiplicato per 2 utilizzando sempre la stessa capacità (C1) quindi, a

parte errori dovuti ad iniezioni di carica, ogni imprecisione nel rapporto fra C1 e C2 è

cancellata.

QC1 = C1Verr = Q2

QC2 = C1Verr = Q1

02 Maggio 2007

UE - ADC

Massimo Barbaro

27

02 Maggio 2007

UE - ADC

Massimo Barbaro

28

Convertitore Flash

Convertitore Flash: Problematiche

Il convertitore flash usa il

massimo grado di parallelismo

per raggiungere la massima

velocità di conversione (tutti gli

N bit ottenuti in un colpo solo)

al prezzo di un enorme

aumento

dei

componenti

necessari.

Con un partitore resistivo

vengono generati i 2N valori

analogici

di

riferimento

associati ad ogni codice di

ingresso e la tensione di

ingresso viene confrontata con

ogni valore per mezzo di 2N

comparatori.

Il codice in uscita dai

comparatori è termometrico e

necessita

di

un’ulteriore

codifica (digitale) per diventare

binario.

02 Maggio 2007

Elevata capacità di ingresso: essendoci 2N comparatori in ingresso il ritardo introdotto

g

può essere consistente,, ed aumenta con la risoluzione.

p

dal nodo di ingresso

“Resistor String Bowing”: in comparatori ad elevata velocità può essere necessario

implementare i comparatori con stadio di ingresso a BJT. In tale caso il comparatore

assorbe corrente che,

che per quanto piccola,

piccola può generare degli errori nei valori di

riferimento soprattutto per i valori centrali (bowing=inarcamento).

g

i 2N p

percorsi che p

portano l’ingresso

g

ai comparatori

p

possono

p

Ritardo dell’ingresso:

avere ritardi associati differenti

Clock skew: ritardi nel clock che pilota i diversi comparatori possono introdurre un

errore (jitter) nel tempo di campionamento per i vari comparatori

Generazione di “bolle”: nel codice termometrico, per le cause precedenti, possono

g

in uscita non è perfettamente termometrico ma sono

comparire bolle, ossia il segnale

presenti dei “buchi”. Tali bolle possono fare fallire la logica di decodifica.

UE - ADC

Massimo Barbaro

29

02 Maggio 2007

Flash: Eliminazione Bolle

UE - ADC

Massimo Barbaro

Massimo Barbaro

30

Flash: Two-Step

Per ridurre il numero di componenti si può adottare uno schema di conversione a

due passi come quello mostrato in figura. Un primo convertitore flash a N/2 bit trova

gli N/2 bit più significativi con una conversione grossolana (coarse). Viene poi

calcolato l’errore fra il valore in ingresso e l’uscita di un DAC pilotato da tali bit e

l’errore viene amplificato di 2N/2 per poter essere di nuovo convertito con un flash a

N/2 per ottenere i bit meno significativi. Come secondo flash può anche essere

riutilizzato il primo con un funzionamento a due fasi.

fasi

Se si utilizzano due flash il numero di resistenze e comparatori è pari a 2N/2+1 anziché

2N (es. N=10, 33 anziché 1024)

Conversion D/A, differenza e moltiplicazione possono essere realizzate

contemporaneamente con un circuito a switched capacitors (chiamato MDAC,

Multiplier and Digital Analog Converter) ricavato dal DAC a redistribuzione di carica.

Per ridurre il problema delle “bolle” è possibile complicare leggermente la parte

g

, nel circuito in figura

g

gli zeri spurii

g

p

possono essere eliminati ((solo se c’è un

p

digitale,

solo zero, il circuito non corregge bolle di più di uno zero).

02 Maggio 2007

UE - ADC

31

02 Maggio 2007

UE - ADC

Massimo Barbaro

32

Interpolating Converters

Interpolating Converters (2)

Per ridurre il numero di

preamplificatori

p

p

e ridurre di

conseguenza la capacità di

ingresso e l’occupazione di area

si può adottare un’architettura

ad interpolazione.

interpolazione

Con la prima stringa di

resistenze si generano 4

tensioni

di

riferimento.

I

preamplificatori (con guadagno

piccolo) suddividono l’intervallo

fra due riferimenti adiacenti in

modo lineare per aumentare il

numero di riferimenti fino al

numero

richiesto

dalla

risoluzione.

Da notare che con questo

schema NON si riduce il numero

totale di latch.

02 Maggio 2007

Ogni preamplificatore genera un’uscita proporzionale alla differenza fra l’ingresso e la

gli è applicata

pp

(quando q

(q

questa differenza diventa g

grande

tensione riferimento che g

l’amplificatore satura). Il partitore resistivo fra due uscite di preamplificatori suddivide

poi la differenza di potenziale fra le due uscite di amplificatore (centrate in posizioni

differenti dell’asse Vin) in un numero opportuno di sottointervalli. Nel caso in figura da

ogni intervallo se ne ottengono 4 quindi il convertitore ha una risoluzione di 4 bit (16

valori) con solo 4 preamplificatori anziché 16 ma con 16 latch (e resistenze).

UE - ADC

Massimo Barbaro

33

02 Maggio 2007

Folding Converters

Massimo Barbaro

34

Folding Converters (2)

I

convertitori

folding

lavorano in modo simile ai

two-step

two

step

(trovano

separatamente bit più e

meno

significativi)

ma

effettuano

una

preelaborazione

l b

i

anziché

i hé usare

un DAC, inoltre i due gruppi

di

bit

sono

generati

contemporaneamente

co

te po a ea e te e non

o

in sequenza.

Il segnale di ingresso passa

attraverso i folding blocks

che

h generano uscite

it come

quelle in figura, centrate in

intervalli diversi.

p

i bit p

più significativi

g

Spesso

vengono identificati proprio

dai folding blocks.

02 Maggio 2007

UE - ADC

Il principio di funzionamento è il seguente:

g blocks “ripiegano”

p g

il segnale

g

di ingresso

g

in un numero M di volte ((nel caso in

i folding

figura 4 volte, una per ogni transizione della caratteristica ingresso/uscita del folding

block). In questo caso si ottengono i 4 segnali V1, V2, V3 e V4.

I 2 bit più significativi determinano in quale dei 4 sottointervalli ci si trova. All’interno di

tale sottointervallo le uscite dei folding block rappresentano un codice termometrico

particolare.

Se Vin è compreso nel primo o terzo sottointervallo il codice termometrico di V1, V2,

g

aumenta il numero di 1),

) mentre negli

g

V3 e V4 è normale ((al crescere dell’ingresso

altri due intervalli il codice termometrico è rovesciato (all’aumentare del segnale il

numero di 1 diminuisce).

In particolare con Vin fra 0 e ¼ V1,V2,V3,V4=0000,0001,0011,0111,1111 poi con Vin

tra ¼ e ½ V1,V2,V3,V4=1110,1100,1000,0000

V1 V2 V3 V4=1110 1100 1000 0000 e così via.

via

Vantaggi: si riduce il numero di latch (4 anziché 16) ma non si riduce di molto la

g

((a causa del modo in cui è realizzato il folding

g block, si veda il

capacità di ingresso

lucido successivo).

UE - ADC

Massimo Barbaro

35

02 Maggio 2007

UE - ADC

Massimo Barbaro

36

Folding Converters (3)

Folding e Interpolazione

Il blocco di folding può

essere realizzato in questo

modo.

L’output Vout è in qualche

modo l’OR di Va e Vb

(Vout è bassa solo se lo

sono sia

i Va

V che

h Vb).

Vb)

Va va alto con Vin fra Vr1

e Vr2 (quando non scorre

corrente

co

e te su R1)) mentre

e t e Vb

b

va

basso

quando

Vr3<Vin<Vr4.

Visto

che

con

l’interpolazione si riduce

capacità di ingresso ma

NON il numero di latch e

che

con

l’approccio

folding si riduce il

numero di latch

l t h ma NON

la capacità di ingresso in

genere le due cose

e go o

applicate

app

cate

vengono

contemporaneamente

come nel circuito in

figura.

C

Come

sii vede

d Vin

Vi va in

i

ingresso a 4 coppie

differenziali per ogni blocco

folding

g p

per un totale di 16

coppie

differenziali,

esattamente quanto si

avrebbe nel caso di un

fl h classico

flash

l

i (full-flash).

(f ll fl h)

02 Maggio 2007

UE - ADC

Massimo Barbaro

37

Pipeline Converters

L’architettura two-step

può

essere

generalizzata in modo

che ad ogni step venga

convertito un solo bit. I

vari

step

possono

essere poi organizzati

in pipeline in modo da

avere un uscita ad ogni

colpo di clock.

clock

I

blocchi

DAPRX

contengono il S&H, il

confronto, il calcolo del

residuo

e

la

moltiplicazione per due.

L’errore così ottenuto

viene dato in pasto al

DAPRX successivo per

generare

il

bit

seguente.

02 Maggio 2007

UE - ADC

Massimo Barbaro

39

02 Maggio 2007

UE - ADC

Massimo Barbaro

38