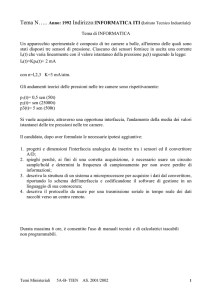

Esame di stato (Elettronica)

Due sensori forniscono a un sistema di acquisizione dati segnali variabili lentamente nel

tempo, rispettivamente da 0 a 1,5 V e da 300 a 600 µA.

L'unità di controllo del sistema deve acquisire, in tempo reale, i dati provenien ti dai sensori e

trasmetterli a un ricevitore su richiesta.

Il candidato, formulate le ipotesi aggiuntive che ritiene necessarie, deve:

1) individuare uno schema a blocchi del sistema, descrivendo le funzioni di ciascun blocco e le

relative interazioni;

2) produrre il diagramma di flusso della soluzione del problema specificando le parti relative

all'inizializzazione del sistema e alla rilevazione dei dati;

3) scegliere il convertitore da utilizzare, dopo aver esaminato le caratteristiche fornite;

4) dimensionare le eventuali interfacce tra l'uscita dei sensori e il convertitore e tra il con vertitore e un microprocessore di sua conoscenza;

5) descrivere il principio di funzionamento del convertitore utilizzato;

6) analizzare se il sistema sia ancora utilizzabile per acquisire dati nel caso che i sensori

forniscano segnali variabili velocemente nel tempo e, nel caso di una eventuale modifica,

descriverne il funzionamento.

(Esame di Stato)

-

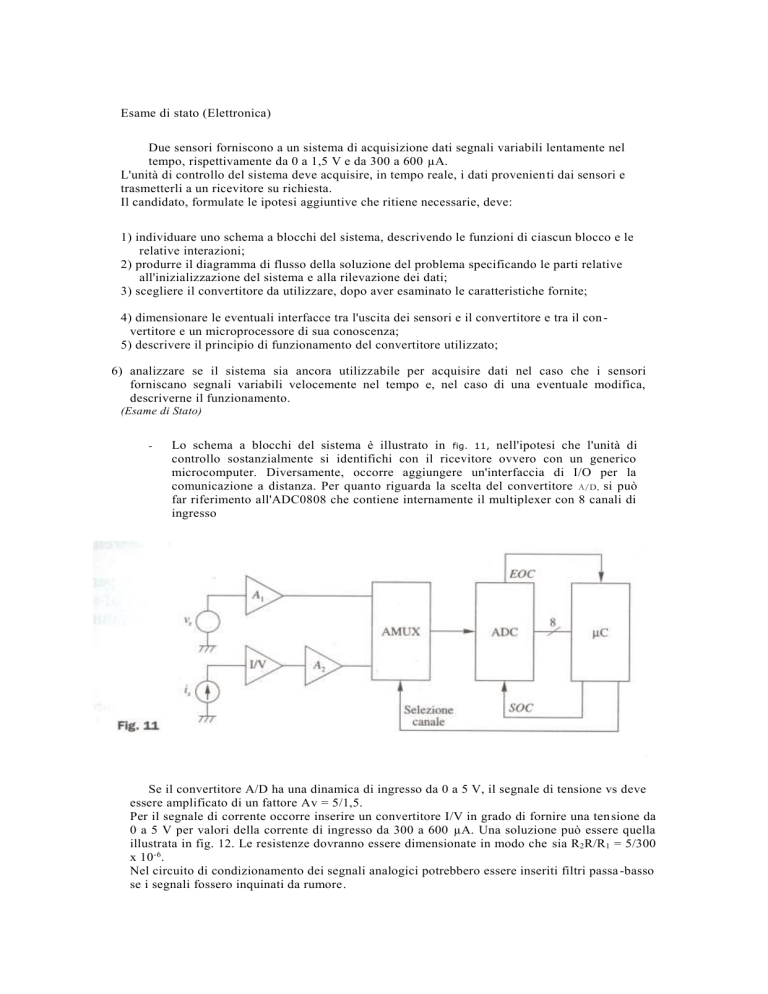

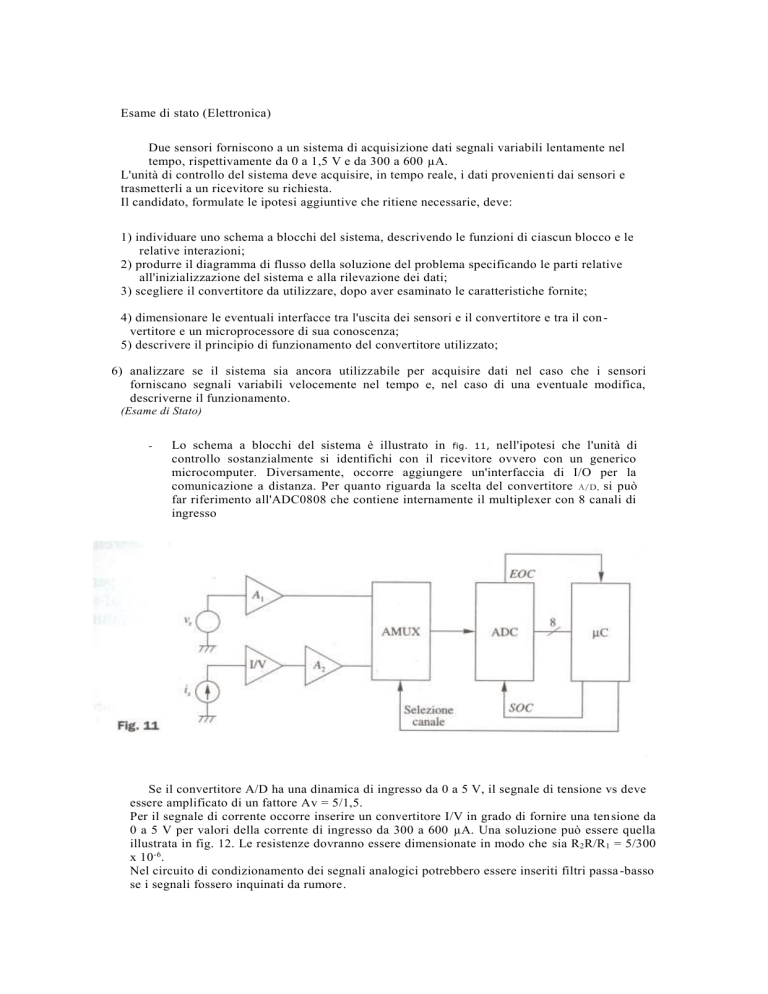

Lo schema a blocchi del sistema è illustrato in fig. 11, nell'ipotesi che l'unità di

controllo sostanzialmente si identifichi con il ricevitore ovvero con un generico

microcomputer. Diversamente, occorre aggiungere un'interfaccia di I/O per la

comunicazione a distanza. Per quanto riguarda la scelta del convertitore A/D, si può

far riferimento all'ADC0808 che contiene internamente il multiplexer con 8 canali di

ingresso

Se il convertitore A/D ha una dinamica di ingresso da 0 a 5 V, il segnale di tensione vs deve

essere amplificato di un fattore Av = 5/1,5.

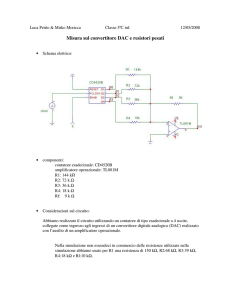

Per il segnale di corrente occorre inserire un convertitore I/V in grado di fornire una ten sione da

0 a 5 V per valori della corrente di ingresso da 300 a 600 µA. Una soluzione può essere quella

illustrata in fig. 12. Le resistenze dovranno essere dimensionate in modo che sia R2R/R1 = 5/300

x 10-6.

Nel circuito di condizionamento dei segnali analogici potrebbero essere inseriti filtri passa -basso

se i segnali fossero inquinati da rumore.

Utilizzando il convertitore ADC0808, si può sfruttare il multiplexer interno po nendo a massa

tutte le linee di indirizzo, a eccezione di Ao che viene pilotata dall'unità di controllo. Per quanto

riguarda 1'interfacciamento dell'ADC con l'unità di controllo e ricezione dati, si può fare

riferimento a quanto studiato a sistemi.

Relativamente al punto 6), si può osservare che con il convertitore scelto si possono otte nere

tempi di conversione dell'ordine di 100 µs, il che limita la frequenza di campionamento di

ciascun segnale a f c = 5 kHz. La frequenza f c, potrebbe essere raddoppiata utilizzando due ADC,

uno per ogni canale di ingresso, multiplandone le uscite digitali.

Un altro aspetto da considerare è che, se la variazione del segnale applicato all'ADC durante

il tempo di conversione è superiore al valore di 1LSB (nel nostro caso par i a circa 20 mV), per

mantenere una risoluzione di 8 bit occorre inserire uno (o due) circuiti S/H.